SDRAM高速PCB布线策略与技巧

需积分: 49 185 浏览量

更新于2024-07-24

收藏 911KB PDF 举报

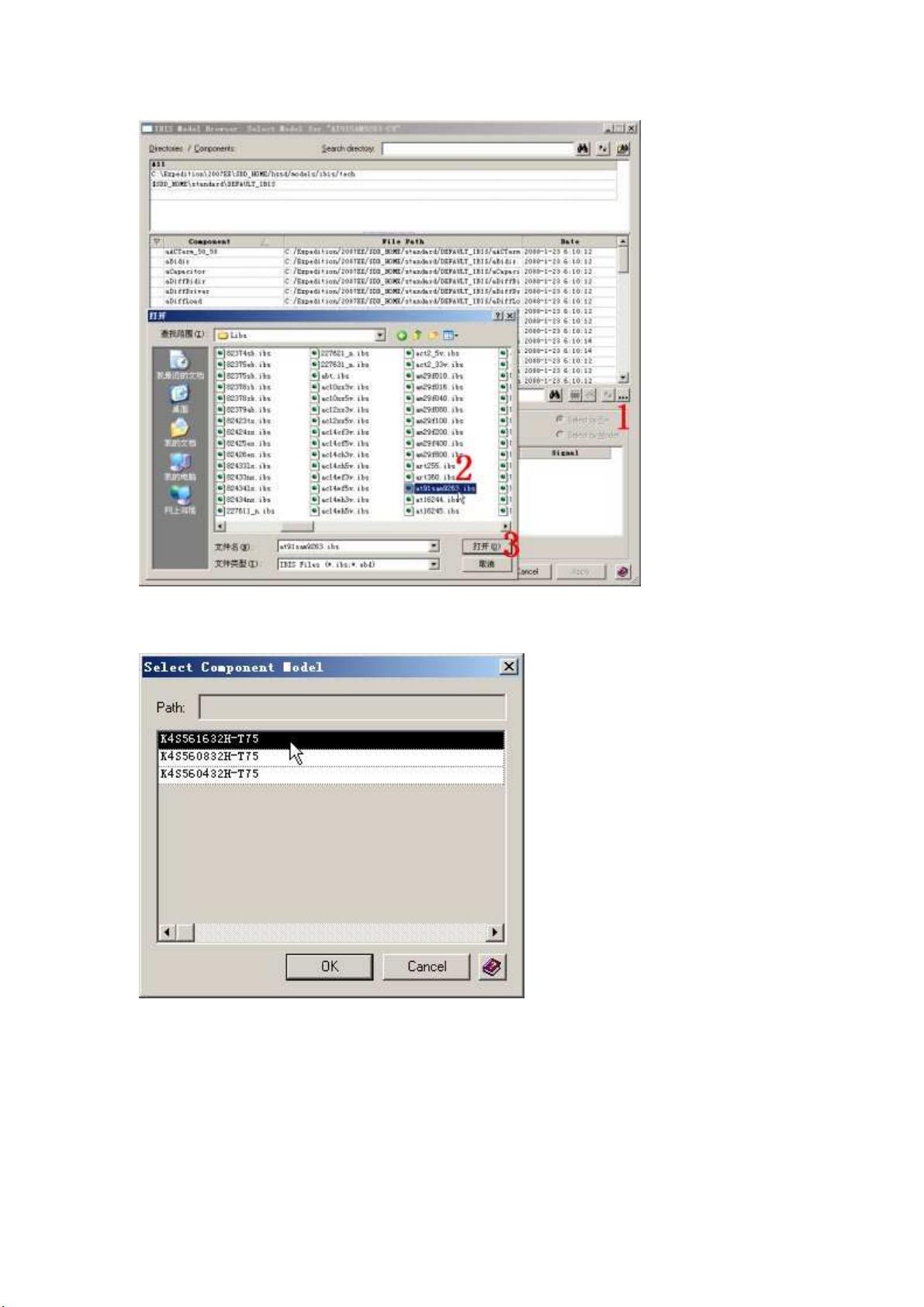

"这篇文章主要探讨了在CADENCE的ALLEGRO PCB设计软件中处理SDRAM电路布线的规则,以及在高速数字PCB设计中的注意事项。作者通过对比MentorWG、DxDesigner、Expedition和CES等工具,强调了高速PCB设计的知识和技巧的重要性。文中提到,尽管SDRAM的布线要求相对较低,但DDR内存的布线更具挑战性。"

在高速数字PCB设计中,SDRAM(Synchronous Dynamic Random-Access Memory)的布线规则至关重要,因为它们直接影响到系统的性能和稳定性。SDRAM是一种同步内存,其数据读取和写入操作与系统时钟同步,因此需要精确的时序控制。以下是一些关键的布线考虑因素:

1. **线长匹配**:SDRAM的数据线和地址线通常需要匹配长度,以确保所有信号在同一时刻到达目的地,避免时序错误。这可以通过等长布线、缓冲器插入或调整走线路径实现。

2. **信号完整性**:SDRAM工作在较高的频率下,信号的上升时间和下降时间非常短,因此需要确保信号在传输过程中没有失真。减小回路面积,使用适当的过孔设计,以及采用低阻抗材料可以帮助改善信号完整性。

3. **电源和地平面**:稳定的电源和良好的接地对于减少噪声和提高信号质量至关重要。SDRAM的电源层和地层应尽可能连续且靠近信号线,形成紧密的电源-地参考平面。

4. **避免串扰**:相邻的高速信号线之间的相互干扰是高速PCB设计中的另一个挑战。通过适当的布线策略,如隔离、分隔或使用屏蔽层,可以降低串扰的影响。

5. **EMI/RFI控制**:高速信号产生的电磁辐射可能对其他电路造成干扰。合理布局,采用屏蔽设计,以及使用滤波器和去耦电容可以降低电磁干扰(EMI)和射频干扰(RFI)。

6. **热管理**:高速组件可能会产生大量热量,需要考虑散热设计,以防止温度升高导致性能下降或系统不稳定。

作者提到了MentorWG软件,虽然它功能强大,但存在许多BUG,使用时需要谨慎。同时,他建议初学者可以从《High-Speed Digital System Design》这样的书籍开始,理解高频系统设计的基本概念,然后再结合实际工具进行实践。

在DDR(Double Data Rate)内存的布线中,由于其数据在时钟的上升沿和下降沿均传输,布线规则更加严格,对时序和信号完整性的要求更高。作者表示,DDR内存的布线是高速PCB设计的一个重要实践领域,但目前他没有相关的项目进行验证。

无论使用哪个PCB设计工具,理解高速数字PCB设计的基本原则和技巧是至关重要的。设计师需要不断学习和实践,才能应对不断提升的系统速度和复杂性。

2020-04-27 上传

2012-07-20 上传

2011-12-02 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

都尉

- 粉丝: 0

- 资源: 3

最新资源

- 平尾装配工作平台运输支撑系统设计与应用

- MAX-MIN Ant System:用MATLAB解决旅行商问题

- Flutter状态管理新秀:sealed_flutter_bloc包整合seal_unions

- Pong²开源游戏:双人对战图形化的经典竞技体验

- jQuery spriteAnimator插件:创建精灵动画的利器

- 广播媒体对象传输方法与设备的技术分析

- MATLAB HDF5数据提取工具:深层结构化数据处理

- 适用于arm64的Valgrind交叉编译包发布

- 基于canvas和Java后端的小程序“飞翔的小鸟”完整示例

- 全面升级STM32F7 Discovery LCD BSP驱动程序

- React Router v4 入门教程与示例代码解析

- 下载OpenCV各版本安装包,全面覆盖2.4至4.5

- 手写笔画分割技术的新突破:智能分割方法与装置

- 基于Koplowitz & Bruckstein算法的MATLAB周长估计方法

- Modbus4j-3.0.3版本免费下载指南

- PoqetPresenter:Sharp Zaurus上的开源OpenOffice演示查看器