"Design Compiler综合原理与全过程详解"

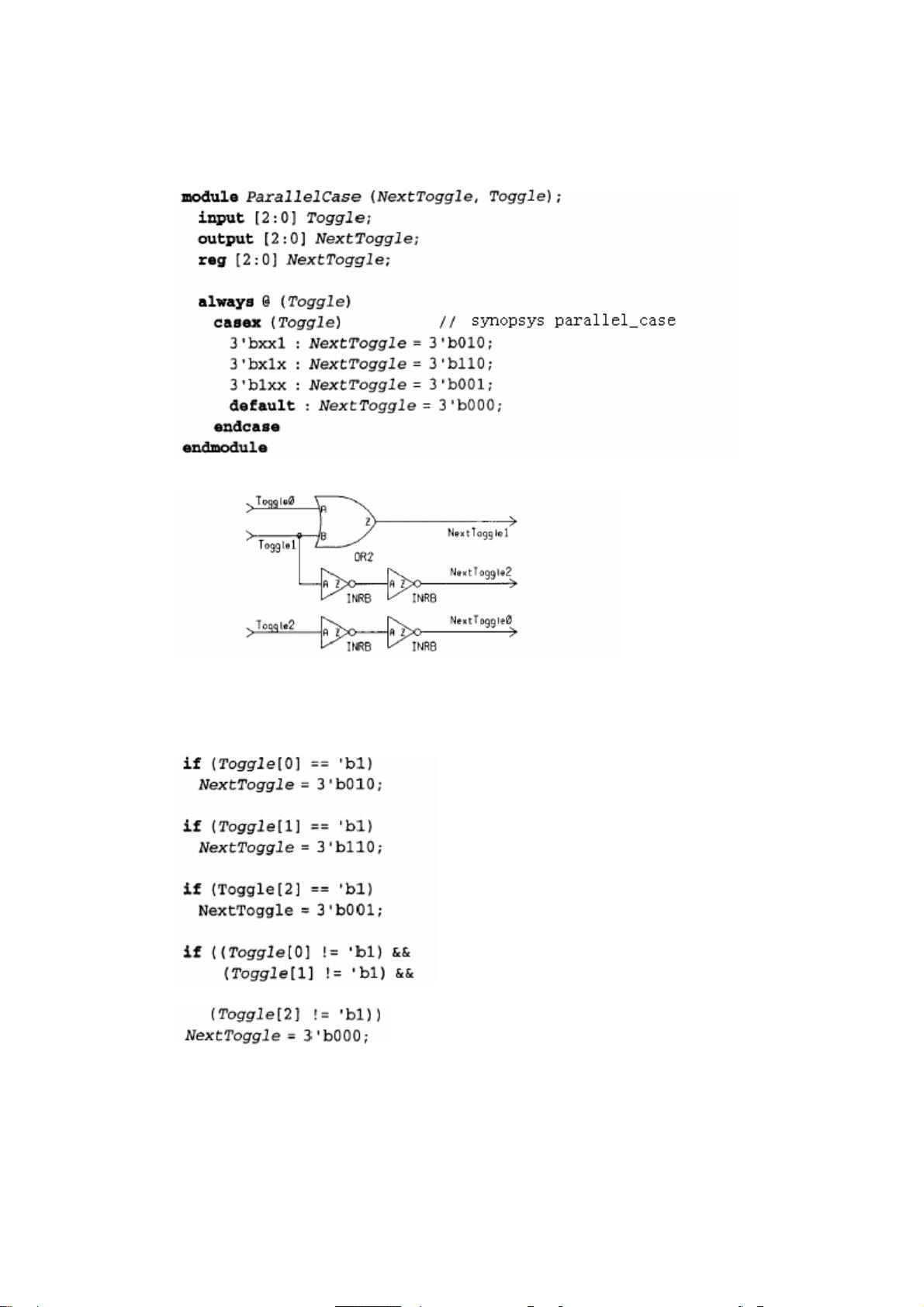

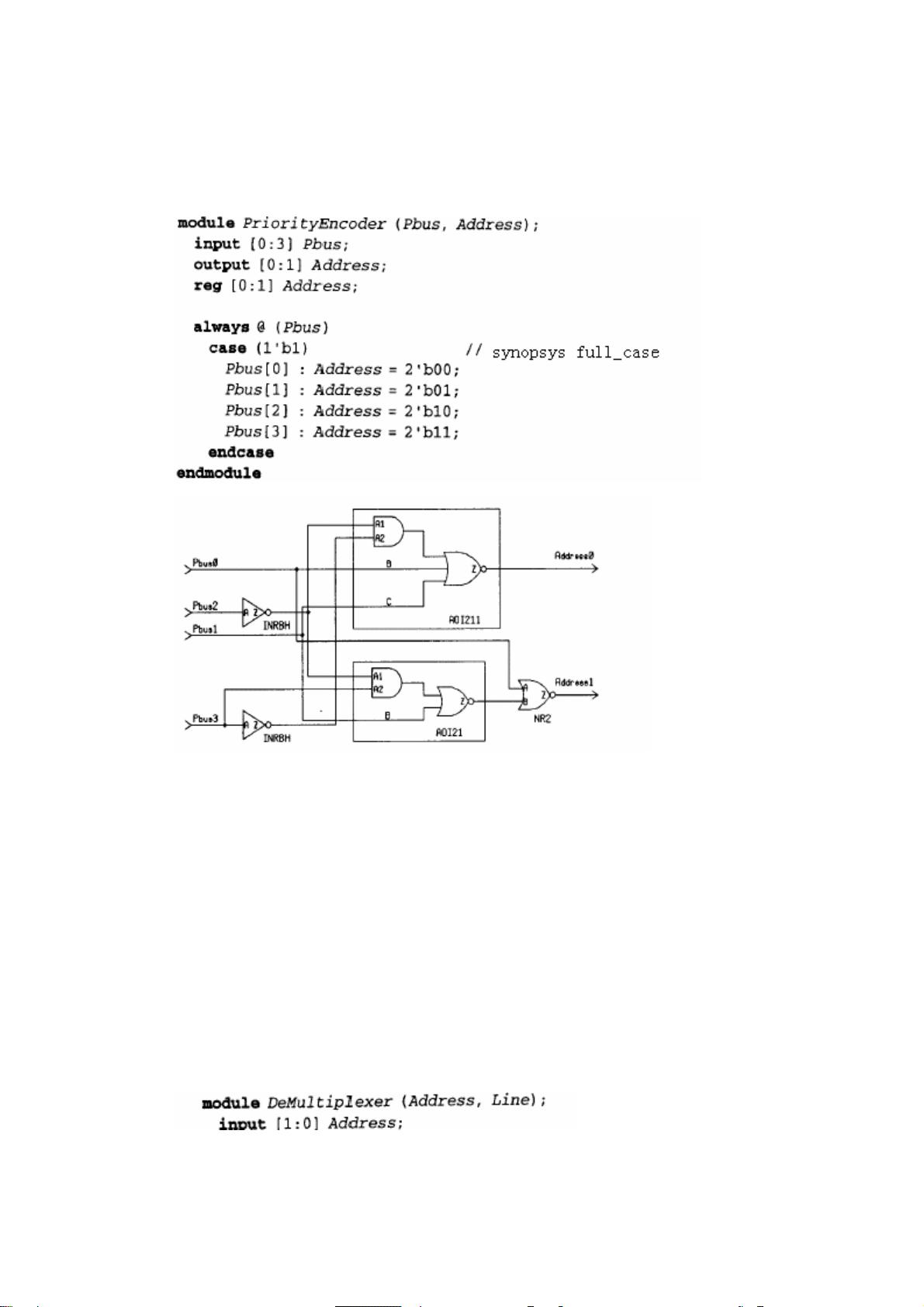

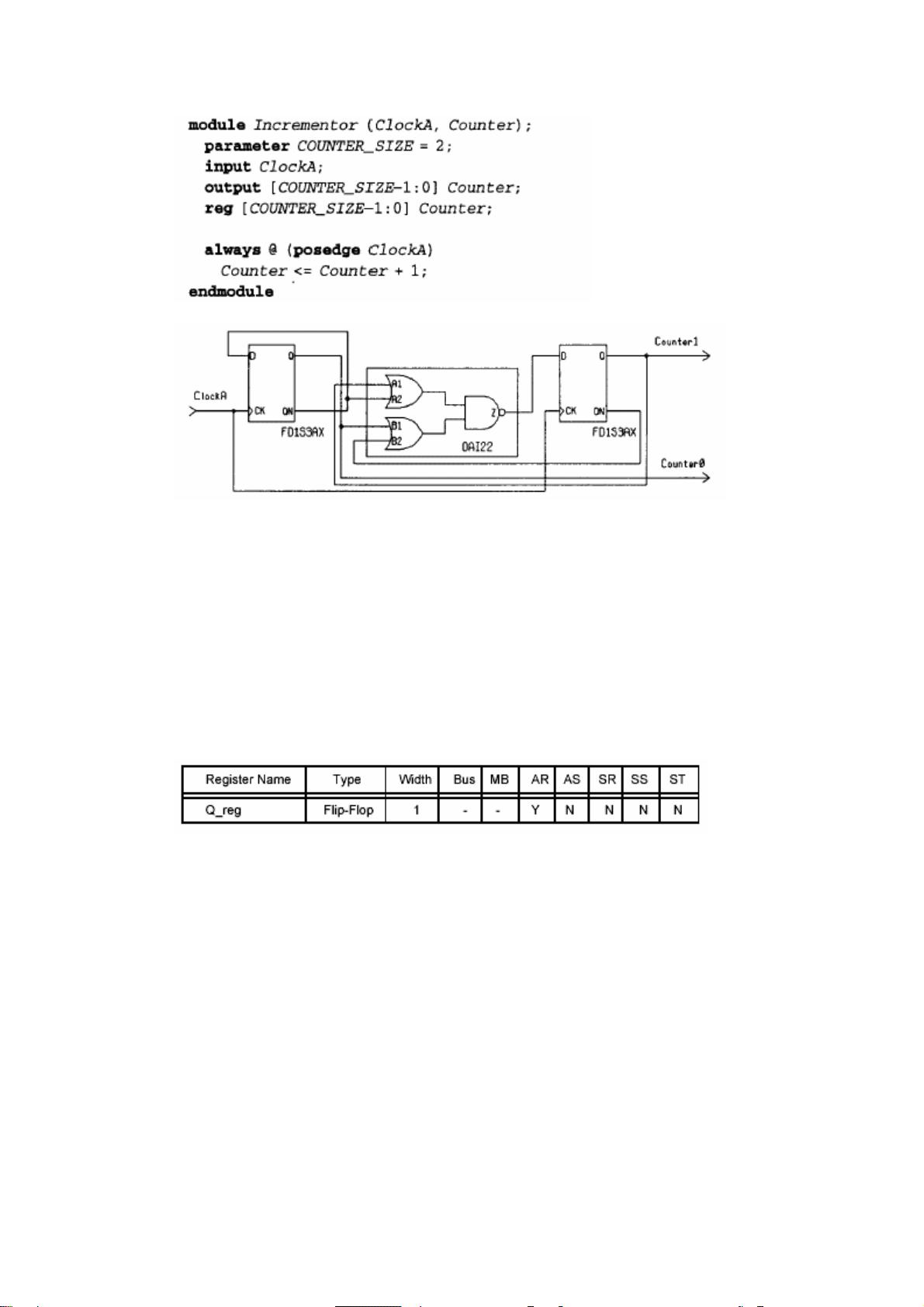

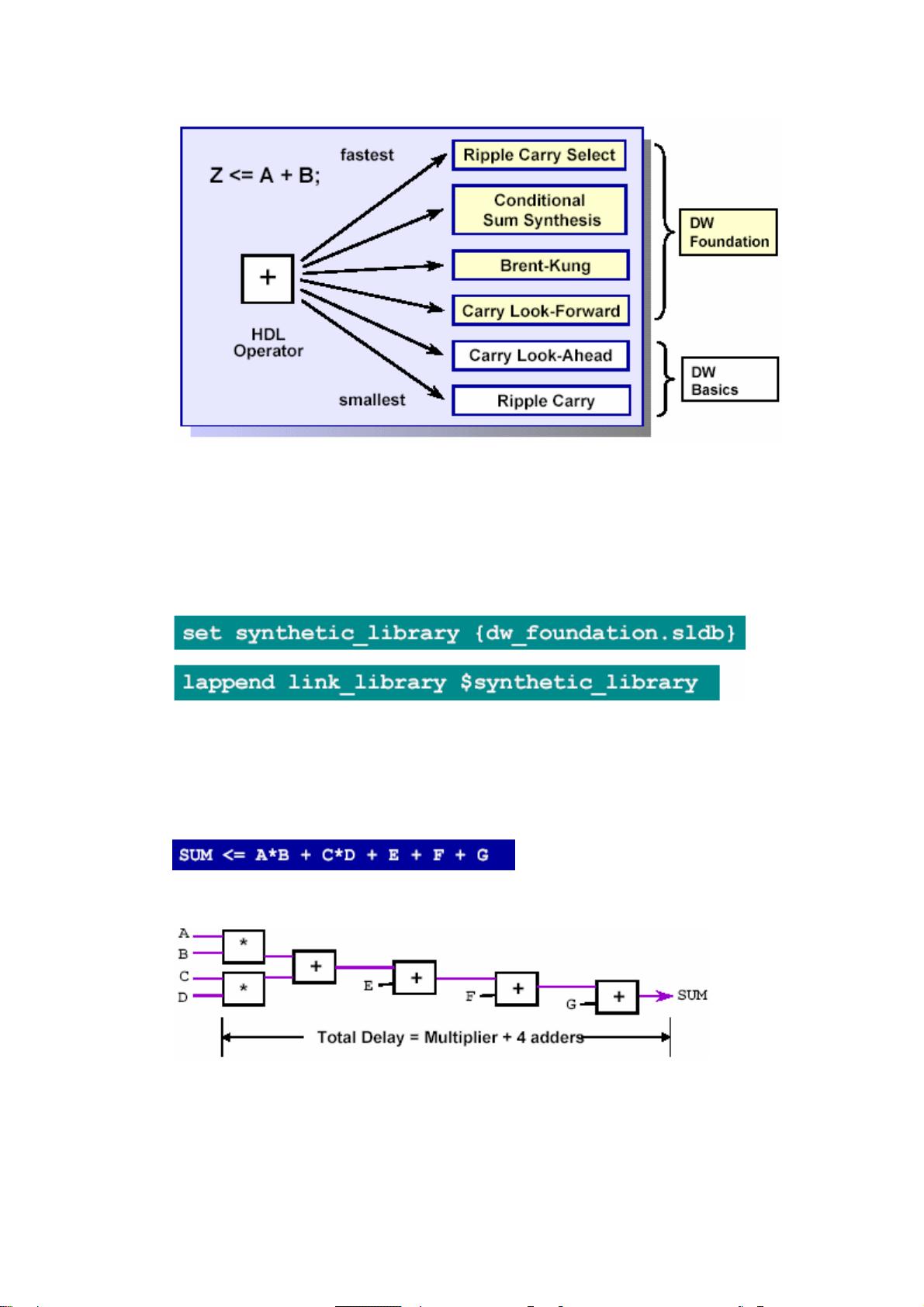

Design Compiler 是 Synopsys 公司的一款用于电路综合的核心工具,它是前端模块设计中重要的一步。在电路设计中,综合的过程是将行为描述的电路、RTL 级的电路转换为门级的电路网表。Design Compiler 能够方便地将使用 HDL 语言描述的电路转换为基于工艺库的门级电路网表。 综合是一种使用软件的方法来设计硬件的过程,它将门级电路的实现与优化工作留给综合工具。综合的目标是在满足设计电路的功能、速度和面积等限制条件下,寻找出一个逻辑网络结构的最佳实现方案。为此,综合需要根据系统的逻辑功能和性能要求,在包含众多已知结构、功能和性能的单元库的支持下,将行为级描述转换为指定的技术库中单元电路的连接。 综合的过程可以分为三个阶段:转换、映射和优化。在转换阶段,综合工具将使用的硬件描述语言(HDL)的代码转换为内部数据结构,以便后续的处理。映射阶段是将这些内部数据结构映射到指定的技术库单元电路上的过程。优化阶段是对映射后的电路进行优化,以满足设计要求和限制条件,并提高电路的性能。综合工具会根据设计要求和性能目标对电路进行细粒度的优化,以减小电路的面积、功耗和时延。 Design Compiler 提供了丰富的综合功能和优化策略,使用户能够根据具体需要进行电路综合和优化。它支持多种硬件描述语言,如Verilog和VHDL,并且能够与其他EDA工具进行无缝集成,如物理设计工具和时序分析工具。用户可以使用 Design Compiler 来实现对电路结构的灵活控制,以获得最佳的综合结果。 使用 Design Compiler 进行电路综合的全过程包括以下几个主要步骤: 1. 环境设置:设置 Design Compiler 的运行环境,并导入所需的库文件和设计文件。 2. 分析和优化约束:对设计进行分析,并设置合适的优化约束,包括面积、时序和功耗等约束。 3. 逻辑综合:使用 Design Compiler 将 HDL 代码转换为门级网表。这一步骤中,综合工具会自动进行逻辑优化,以减小电路的面积和功耗。 4. 技术映射:将转换得到的门级网表映射到指定的技术库单元电路上,以满足设计要求和限制条件。 5. 对综合结果进行优化:对映射后的电路进行进一步的优化,包括时序优化、功耗优化和面积优化等。 6. 验证与分析:进行电路的功能验证和时序分析,以确保综合结果符合设计要求。 7. 输出结果:生成最终的综合结果,包括门级网表、时序约束文件和报告等。 综合是数字电路设计过程中不可或缺的一步,它能够将行为级描述转换为门级电路实现的关键工具。Design Compiler 作为一款强大的综合工具,具有丰富的功能和优化策略,能够帮助设计工程师快速且高效地完成电路的综合和优化工作。通过合理设置综合约束和优化策略,设计工程师可以获得符合设计要求的最佳综合结果。

剩余113页未读,继续阅读

- 粉丝: 0

- 资源: 6

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

信息提交成功

信息提交成功

评论0