深亚微米ASIC设计流程:从系统行为到布局布线

需积分: 32 176 浏览量

更新于2024-07-24

收藏 2.13MB PDF 举报

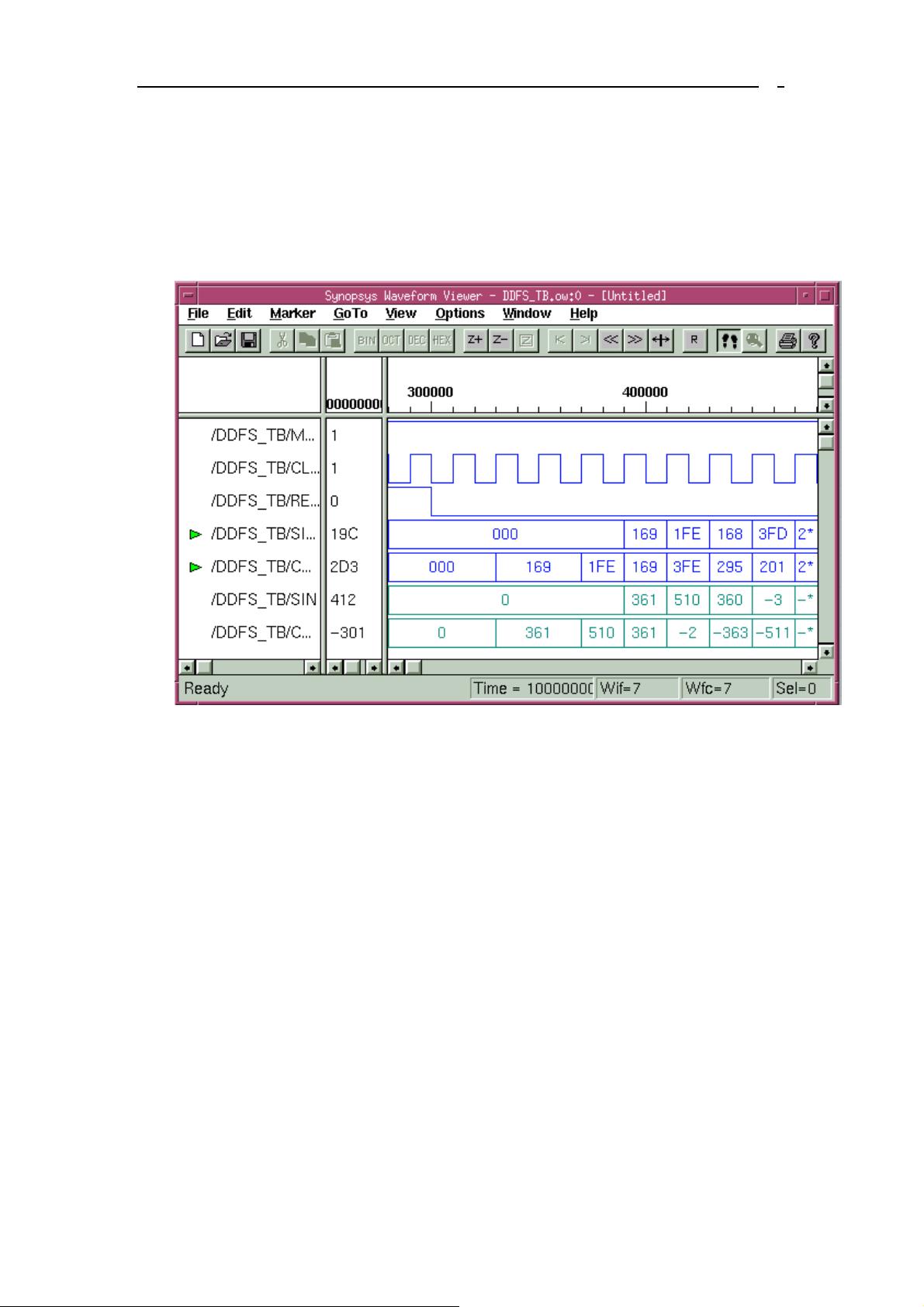

"本文详细介绍了基于标准单元库的深亚微米数字集成电路的ASIC设计流程,包括从系统行为级描述到最终版图后仿真的全过程。文章以Synopsys的VSS工具进行仿真,Design Compiler进行综合,以及Cadence的Silicon Ensemble进行自动布局布线,同时使用Active-HDL进行版图后仿真验证。文中通过DDFS实例具体阐述设计流程,探讨了设计语言、验证方法、设计重用、自动化工具等关键环节在现代ASIC设计中的应用和重要性。"

在ASIC(Application-Specific Integrated Circuit)设计中,流程通常分为多个阶段,这些阶段在描述中被详细列出:

1. **设计规格**:首先,确定IC的功能需求和性能指标,这通常基于系统级的行为描述,例如使用VHDL或Verilog这样的硬件描述语言(HDL)。

2. **系统行为级仿真**:使用VSS(VHDL System Simulator)等工具进行系统行为级的功能验证,确保设计符合预期的行为。

3. **设计综合**:经过验证后,通过Design Compiler等综合工具将行为级描述转化为门级网表,这个过程会考虑时序、面积和功耗等约束。

4. **综合后仿真**:对综合后的设计进行门级仿真,以确认其在物理实现前的正确性。

5. **自动布局布线**:使用Cadence的Silicon Ensemble等自动化工具进行布局布线,这是将逻辑设计转化为实际物理版图的过程,需要考虑布线延迟、功耗和面积等因素。

6. **版图后仿真**:版图完成后,使用Active-HDL等工具进行版图后仿真,确保物理实现后的设计仍然满足功能和性能要求。

7. **设计优化**:在整个流程中,可能需要多次迭代,优化设计以达到最佳的性能、功耗和面积平衡。

8. **设计预算**:设计预算方法学允许设计者在早期阶段预测和控制设计的质量,如质量-of-result (QOR),并考虑环境约束。

9. **设计重用**:通过模块编译器和ECO技术,可以复用已验证的IP核,加快设计进程。

10. **形式验证**:与传统的动态仿真相比,形式验证能更快地发现设计错误,且不受工艺和测试平台限制。

11. **数据路径设计**:对于复杂的无规则数据路径,自动化工具帮助简化设计任务。

12. **版图提取和分析**:增强逻辑设计与物理设计之间的互动,优化逻辑综合时对版图的考虑。

这些技术和工具的使用极大地提高了ASIC设计的效率和准确性,适应了深亚微米时代下对设计速度和性能的高要求。

608 浏览量

153 浏览量

2021-09-21 上传

117 浏览量

2010-01-12 上传

点击了解资源详情

153 浏览量

162 浏览量

121 浏览量

leong5566

- 粉丝: 0

- 资源: 1

最新资源

- DEV自定义控件,多按钮用户控件。包含新增,修改,删除,保存等

- Generative_CA:该项目包含使用生成模型继续验证来自H-MOG日期集的运动传感器数据的实现

- restafari,.zip

- Office补丁解决“由于控件不能创建,不能退出设计模式”

- 直流电机PID学习套件1.0,c语言词法分析生成器源码,c语言

- 设计世界

- 单片机防火防盗防漏水仿真protues

- Milestone_three

- matrixmultiplication:c中两个矩阵的乘法

- 易语言窗体设计原代码

- AVL-Tree,c语言游戏源码及素材,c语言

- IOS应用源码之【应用】Skin or Blob Detection(皮肤检测).rar

- openWMail:社区运行wmail的分支-https:github.comThomas101wmail

- basysr:文件pertama

- geomajas-client-common-gwt-command-2.0.0.zip

- DxAutoInstaller-souce.zip