VHDL数据类型与运算符:IEEE标准包概览

需积分: 9 186 浏览量

更新于2024-08-01

收藏 58KB PDF 举报

"这篇文档是关于VHDL中 IEEE 标准包的介绍,主要涵盖了数据类型和操作符,以及如何在设计中使用 IEEE 标准库。文档由 Silvia Chiusano 编写,是 ECE465:数字系统设计模块的一部分,详细讲解了VHDL语言中的数据类型、运算符以及IEEE提供的标准包,包括`std_logic_1164`、`std_logic_arith`、`std_logic_unsigned`、`std_logic_signed`和`std_logic_misc`等。"

在VHDL编程中,理解和掌握 IEEE 标准包至关重要,因为它们提供了广泛的数据类型和操作符,用于描述和实现数字逻辑系统。以下是关键知识点的详细说明:

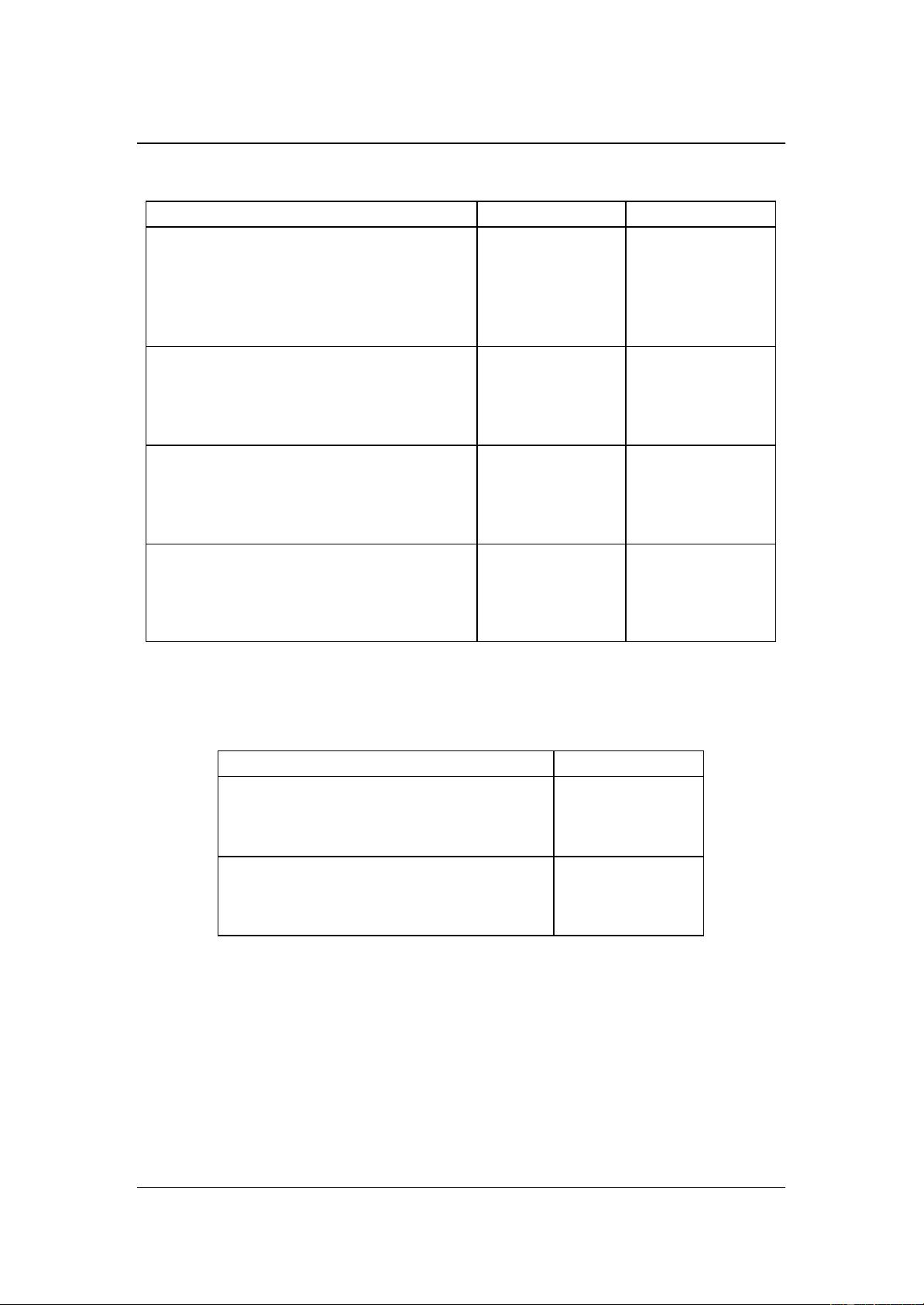

1. **数据类型(Datatypes)**

- VHDL 提供了多种数据类型,如 `std_logic` 用于表示单个信号的状态,它可以是 '0'、'1'、'Z' (高阻)、'U' (未知)、'X' (冲突)、'L' (低电平)、'H' (高电平) 和 '-' (未初始化)。

- `std_ulogic` 类型与 `std_logic` 类似,但不区分大小写。

- `integer` 类型用于表示整数,可以进行算术运算。

- `real` 类型表示浮点数,但通常不用于硬件描述,更多用于软件模拟。

2. **运算符(Operators)**

- **算术运算符** 包括 '+', '-', '*',用于执行基本的数学运算。

- '+' 用于加法,'-' 用于减法,'*' 用于乘法。

- **比较运算符** 包括 '<', '<=', '>', '>=', '=', '/=',用于比较两个表达式。

- `<` 和 `>` 分别表示小于和大于,`<=` 和 `>=` 表示小于等于和大于等于,`=`, `/=` 用于判断相等或不相等。

- **转换运算符** 如 `to_integer` 或 `to_stdlogicvector` 用于在不同数据类型间转换。

- **移位运算符** 如 `shift_left` 和 `shift_right`,用于对二进制数进行左移和右移操作。

3. **IEEE 标准包**

- **Package Standard** 提供了基本的 `std_logic` 类型定义。

- **Package Std_logic_1164** 是最常用的标准包,包含了 `std_logic` 和 `std_ulogic` 的类型定义及相关的操作符。

- **Package Std_logic_arith** 提供了对 `std_logic_vector` 进行算术运算的操作符,但不推荐在现代设计中使用,因为可能会导致非预期的行为。

- **Package Std_logic_unsigned** 和 `Std_logic_signed` 提供了对无符号和有符号 `std_logic_vector` 的算术运算,包括加减乘除等。

- **Package Std_logic_misc** 包含了一些不常见的逻辑操作,如取反、异或等。

使用 IEEE 标准包时,通常需要通过 `use` 语句引入必要的库和组件。例如:

```vhdl

library ieee;

use ieee.std_logic_1164.ALL;

use ieee.std_logic_arith.ALL; -- 或 use ieee.std_logic_unsigned.ALL; use ieee.std_logic_signed.ALL;

```

这样,设计者就可以在VHDL代码中方便地使用这些数据类型和操作符来描述数字逻辑系统。在实际设计中,需根据具体需求选择合适的标准包,以确保设计的正确性和可综合性。

2008-10-18 上传

2020-03-08 上传

2023-08-24 上传

2017-10-01 上传

147 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

dadabuley

- 粉丝: 0

- 资源: 1

最新资源

- C++笔试面试宝典2009版

- Ubuntu中文参考手册

- c#教程c#快速入门教材

- 园区网IP地址规划设计

- Prentice.Hall.JBoss.Seam.Simplicity.and.Power.Beyond.Java.EE.Apr.2007.pdf

- 基于CB220的AT指令式GSM远程安全系统的设计与实现

- IIS的一些问题 IIS常遇问题详解

- DIVCSS布局大全.pdf

- 熟练掌握java反射机制

- Dynamips使用手册

- 锐捷企业网赛复习资料

- Oracle数据库的应用及处理

- PowerBuilder8.0中文参考手册

- 基于arm的单总线数字温度计

- 压力传感器的原理压力传感器的原理压力传感器的原理

- Keil C51集成开发环境、DP-51PRO仿真实验仪使用及案例学习