FPGA中SPI复用配置的高效编程策略

19 浏览量

更新于2024-08-30

收藏 242KB PDF 举报

本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)的FPGA(现场可编程门阵列)开发中,如何有效地利用SPI(Serial Peripheral Interface,串行外围设备接口)进行复用配置的编程方法。SPI作为一种高效的通信接口,因其简洁的连接需求(仅需4根线),能够显著节省硬件资源,特别是对于那些芯片引脚有限的应用场景。在Spantan-3E的配置流程中,FPGA通过SPI接口与第三方SPI Flash进行通信,将硬件结构的bit文件以及小型应用软件工程的代码保存在同一片SPI Flash中,这在资源紧张的项目中显得尤为经济。

首先,配置过程涉及以下几个关键步骤:

1. **SPI配置介绍**:

- SPI是全双工、同步通信方式,适用于数据传输速率较高的应用。

- 它采用简单的4线连接,包括SCK(时钟)、MISO(主设备输入,从设备输出)、MOSI(主设备输出,从设备输入)和CS(片选)。

2. **Spantan-3E SPI配置流程**:

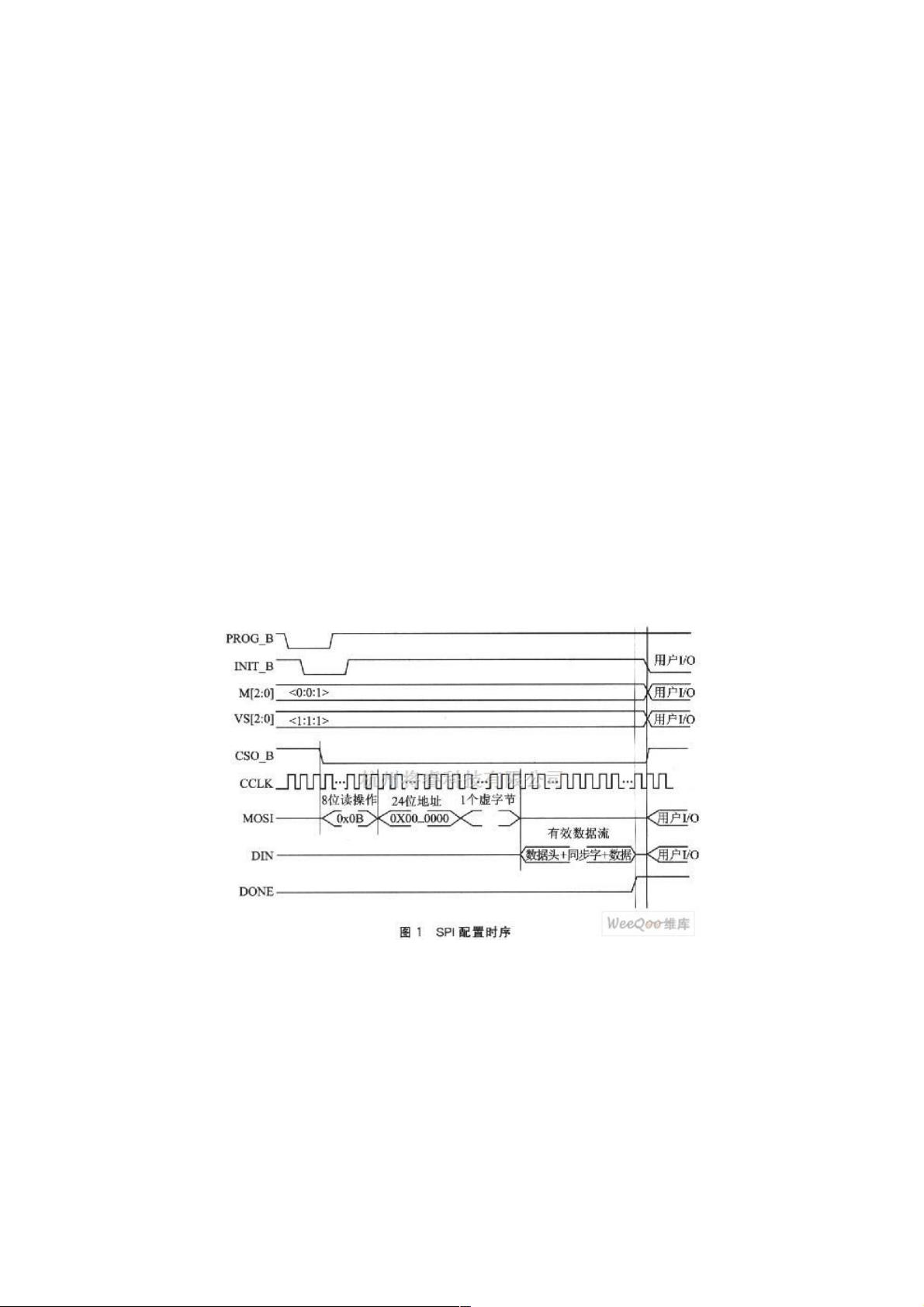

- FPGA配置开始时,系统通过PROG_B引脚发送低脉冲,进行初始化,清除内部配置存储器。

- 初始化过程中,DONE和INIT_B引脚状态会发生变化。

- 当初始化完成,INIT_B引脚变为高,然后FPGA会采样VS[2:0]引脚来识别要执行的SPI命令集。

- 发出CSO_B低电平信号后,FPGA通过CCLK引脚控制SPI Flash,执行读取操作,包括地址和命令集。

3. **复用SPI Flash的优势**:

- 小型应用软件工程编译后的代码可以与FPGA的配置bit文件共享同一块SPI Flash,降低了成本。

- 这种方法简化了硬件设计,减少了板卡上的连接线,有利于PCB布局优化。

文章详细介绍了如何利用SPI接口的特性,在EDA/PLD的FPGA设计中实现复用配置的编程策略,这对于资源管理和硬件设计效率的提升具有重要意义。通过合理的SPI配置,可以在保证性能的同时,优化硬件成本和整体系统设计。

240 浏览量

104 浏览量

2015-10-28 上传

2022-11-07 上传

104 浏览量

119 浏览量

117 浏览量

weixin_38618315

- 粉丝: 1

- 资源: 920

最新资源

- Spring与iBATIS的集成

- ARM体系结构与应用系统设计示例

- SIMOTION 快速入门-西门子

- 计算机编程语言-IDL编程技术

- FREESCALE HCS12xs系列单片机资料

- 三种虚拟化解决方案的比较

- 用链表与文件实现一个简单的学生成绩管理

- IEC61850 8-1 特定通信服务映射

- struts2配置文件

- 2410中文datasheet

- oracle数据库的优化

- Understanding The Linux Kernel 3rd edition

- 深入浅出系列之二_SubVersion

- 走进Linux图形环境

- tomcat performance tuning 性能调整

- mapgis 学习讲义