Vivado XDC时钟约束详解:入门与技巧

XDC约束技巧-时钟篇1.1

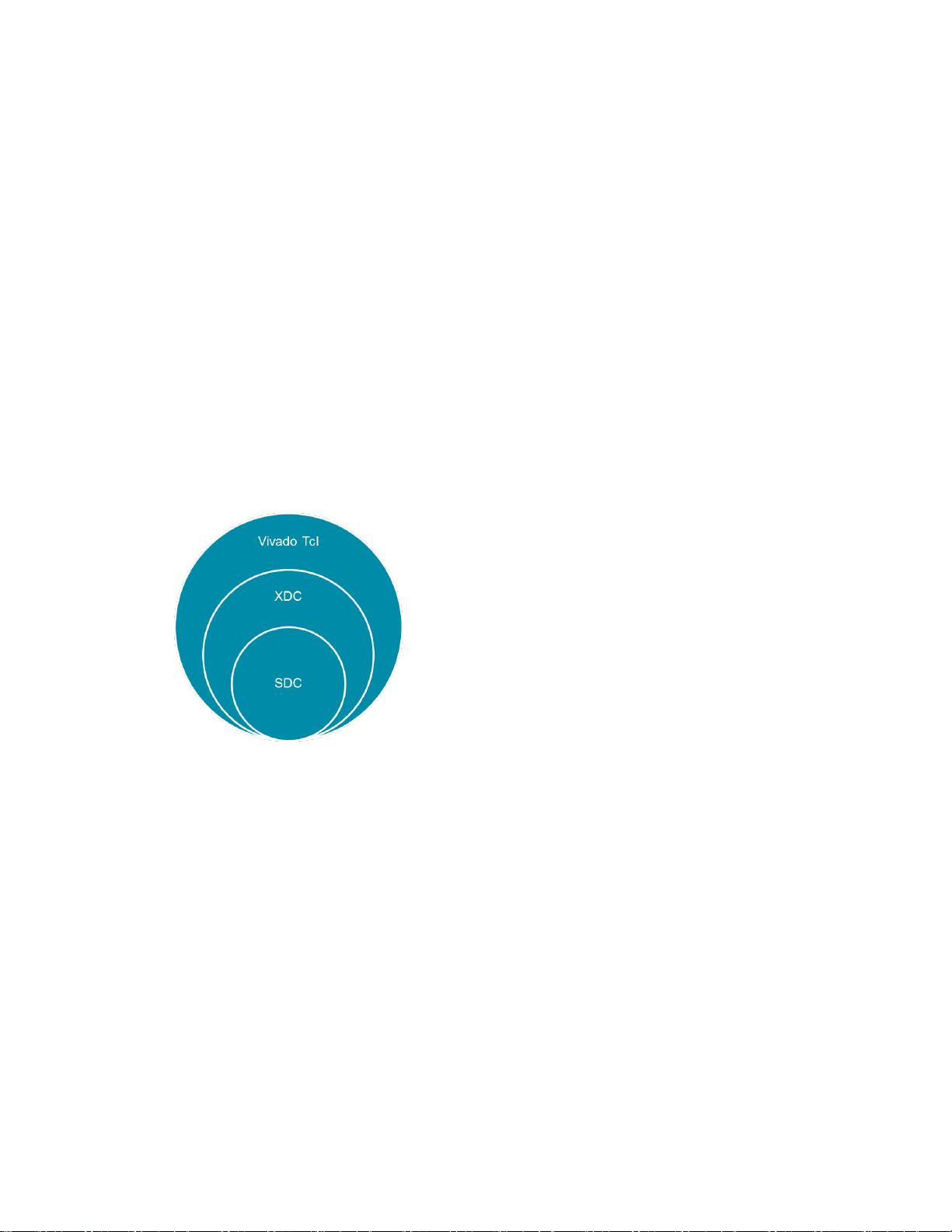

在Xilinx新一代设计套件Vivado中,XDC(Xilinx Design Constraints)取代了先前的UCF(Unified Constraint Format)作为主要的设计约束工具。XDC的优势在于它将前后端约束格式标准化,使得管理变得更加高效。它采用Tcl语言为基础,支持变量、列表和基本运算符等,同时允许实时录入和执行,通过增量设置提高调试效率。XDC的语法结构清晰,易于理解,与业界通用的SDC(Synopsys Design Constraints)规范兼容,增强了设计的移植性和兼容性。

XDC与UCF的主要区别在于处理方式和约束优先级。UCF是以一次性读取整个文件的形式处理,而XDC则是逐条执行,这就意味着约束的顺序至关重要。在XDC中,时序约束通常需要在定义相应的时钟之前设定。UCF默认假设时钟间除非明确标记为同步,否则被视为异步,而XDC遵循ASIC设计的全同步假设,工具会自动分析跨时钟域的路径,除非有明确的时序例外。

XDC的基本语法主要包括三个部分:时钟约束、I/O约束和时序例外约束。在Vivado的UltraFast设计方法学(UG949)中,推荐按照特定的步骤来约束设计,例如先设置时钟约束,再处理I/O,以确保时序完整性。时钟约束可能涉及时钟树的定义、时钟频率、相位关系等;I/O约束则关注信号的驱动能力、扇出限制等;时序例外约束用于指定在特定条件下,设计应如何偏离标准时序规则。

在实际使用XDC时,开发者需要熟练掌握Tcl语言的基础,因为XDC的基本语法受限于Tcl,但可以通过Vivado内的Tcl脚本扩展功能。理解并正确运用这些约束技巧能显著提升设计质量和效率,减少设计周期,确保系统在Vivado工具中的正确实现和优化。

2022-09-20 上传

2017-12-25 上传

2020-12-28 上传

2019-02-27 上传

点击了解资源详情

点击了解资源详情

liekie

- 粉丝: 0

- 资源: 14

最新资源

- 一步步教你安装VMware虚拟机

- Java正则表达式详解

- Symbian OS C++ for Mobile Phones Volume 3.pdf

- he elements of statistical learning data mining ,inference and prediction

- C语言矩阵求逆(源代码)

- C#编码命名规则,规范C#项目的命名

- 西电汤子瀛操作系统答案

- C#文件下载以及相关问题的处理

- c#WinForm生成安装程序

- 表单信息提交到指定邮箱

- oralce 基础学习资料

- Flex 3 CookBook 简体中文

- How Tomcat Works

- Struts+2+Design+and+Programming+A+Tutorial.pdf

- learning opencv computer vision with the opencv_library

- pureMVC中文版文档