【Vivado中XDC约束的高级应用】:提升设计灵活性,专家级应用技巧

发布时间: 2024-11-13 23:42:53 阅读量: 79 订阅数: 28

# 1. XDC约束的基础知识介绍

## 1.1 XDC约束概述

XDC约束文件是FPGA设计中用于定义硬件设计项目的物理实现细节的重要部分。它为时序、输入输出(IO)等提供了精确的指导和限制,确保设计能够在硬件上正确无误地运行。

## 1.2 XDC约束文件的作用

约束文件的作用是在物理设计阶段规定了各种资源的配置,包括时钟资源分配、IO引脚的定位、时序要求以及布线资源的使用等。它帮助设计者将高层次的意图转化为硬件可以理解的详细指令。

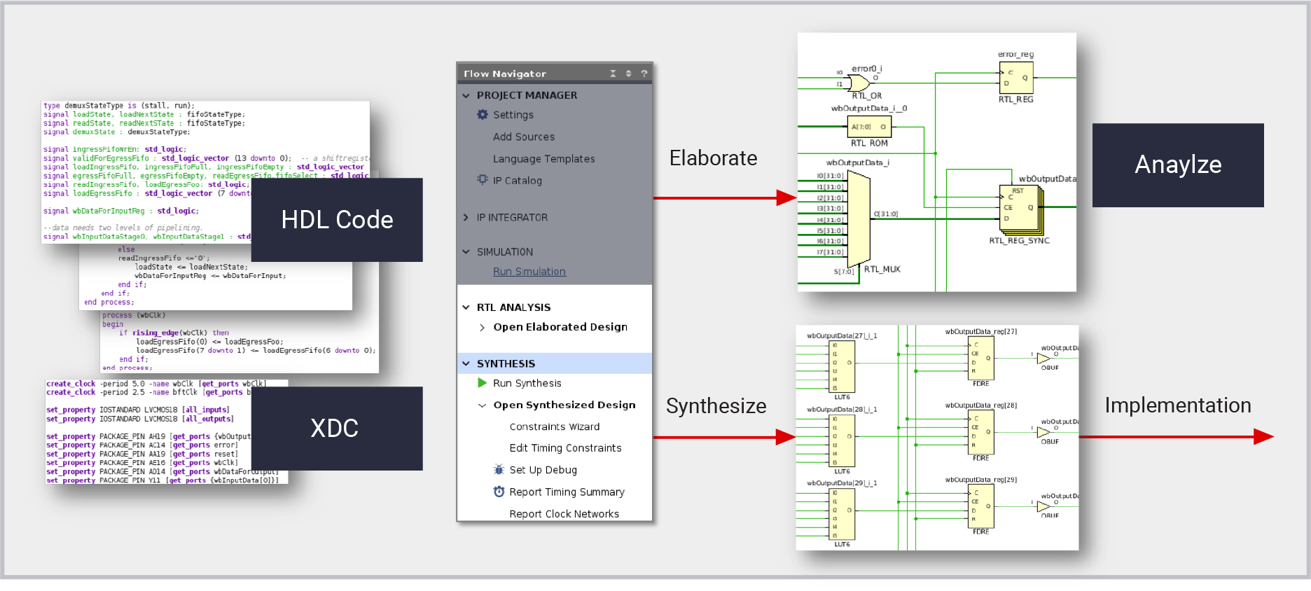

## 1.3 XDC约束与设计流程

在FPGA项目中,XDC约束通常在设计的早期阶段被创建,并随着设计的迭代进行更新。它们在综合、实现和布局布线(P&R)等关键步骤中起着桥梁作用,确保设计的物理实现与预期目标一致。

在下一章节,我们将深入探讨XDC约束的高级语法应用,包括语法结构、时序控制和IO约束策略等核心内容。

# 2. XDC约束的高级语法应用

## 2.1 XDC语法的深入解析

### 2.1.1 基本语法结构和元素

XDC(Xilinx Design Constraints)文件是用于约束FPGA设计的文件,其基本语法结构包括了定义约束的各种元素。如约束的种类、对象、以及具体的值等。语法元素一般由以下部分构成:

- `NET`:表示物理的信号线,比如FPGA的引脚。

- `CELL`:表示设计中的逻辑元件,如寄存器、查找表等。

- `DELAY`:设置信号的传播延迟。

- `CREATE_CLOCK`:创建时钟信号约束。

- `SET_MAX_DELAY`、`SET_MIN_DELAY`:分别设置最大和最小的信号路径延迟。

下面的代码块展示了一个基本的XDC语法结构:

```tcl

# 创建一个时钟约束

create_clock -name sys_clk -period 10.000 -waveform {0.000 5.000} [get_ports {clk}]

# 设置一个信号的最大延迟

set_max_delay -from [get_ports {src}] -to [get_ports {dst}] 5.0

```

这里,`create_clock`用于定义一个名为`sys_clk`的时钟,具有10ns的周期和特定的波形。`set_max_delay`则用于指定从`src`端口到`dst`端口的最大延迟为5ns。

### 2.1.2 高级语法特性和使用场景

高级语法特性使设计者可以实现更复杂的约束需求。例如:

- `create_generated_clock`:用于生成时钟(如PLL输出)。

- `set_multicycle_path`:用于设置多周期路径约束。

- `set_false_path`:用于设置假路径,即不进行时序分析的路径。

高级特性让设计者能够在特定的时钟域间设置复杂的依赖关系,实现更加精确的时序控制。例如,如果有一个路径需要在两个时钟周期内完成,就可以使用`set_multicycle_path`进行配置:

```tcl

# 假设src信号在两个时钟周期内到达dst

set_multicycle_path -from [get_ports {src}] -to [get_ports {dst}] -end -setup 2

```

这段代码表示`src`到`dst`路径的建立时间(setup time)需要考虑两个时钟周期。

## 2.2 XDC约束的时序控制

### 2.2.1 时序约束的基本原则

时序约束是保证数字电路设计中信号能在指定时间内到达目的地的关键。它包括建立时间(setup time)、保持时间(hold time)和路径延迟等。基本原则是确保:

- 所有路径满足建立时间要求,以避免数据竞争。

- 所有路径满足最小路径延迟要求,以保证数据在下一个时钟边沿前稳定。

- 避免不必要的时序冲突。

### 2.2.2 高级时序约束技巧

高级时序约束技巧涉及对特定路径的精确控制,包括:

- `set_max_delay`和`set_min_delay`的灵活运用,允许设计者对于特定的路径设置非默认的延迟限制。

- `set_multicycle_path`的使用,可以放松对于多周期路径的时序限制,从而优化设计性能。

- `set_clock_groups`用于定义不同时钟域之间的关系,可以用于指定两个时钟域互不相关。

```tcl

# 定义两个不相关时钟域

set_clock_groups -exclusive -group [get_clocks clk1] -group [get_clocks clk2]

```

这条命令表示将名为`clk1`和`clk2`的两个时钟域定义为互不相关的独立时钟域,这样可以避免跨时钟域的时序分析。

## 2.3 XDC约束的IO约束策略

### 2.3.1 IO标准和引脚分配

IO约束包括为FPGA的引脚指定特定的标准(比如LVCMOS、LVDS等)以及引脚分配。正确的IO标准和引脚分配是确保信号完整性和电路板级互连质量的重要因素。

- `set_property`命令用于为FPGA的端口或引脚指定属性,例如电压标准。

- `set PACKAGE_PIN`用于指定特定的FPGA引脚位置。

示例代码:

```tcl

# 为端口指定LVCMOS 3.3V标准

set_property PACKAGE_PIN T12 [get_ports {serial_data}]

set_property IOSTANDARD LVCMOS33 [get_ports {serial_data}]

```

### 2.3.2 IO约束的高级应用实例

在处理高速信号时,可能会用到延迟匹配(Delay Matching)等高级技术。延迟匹配确保了具有相同路径长度的信号具有相同的延迟,这对于差分信号和同步信号尤为重要。

```tcl

# 对高速差分信号对进行延迟匹配

set_property PACKAGE_PIN U14 [get_ports {diff_data_p}]

set_property PACKAGE_PIN U13 [get_ports {diff_data_n}]

set_property DELAY_CHAIN true [get_ports {diff_data_p}]

set_property DELAY_CHAIN true [get_ports {diff_data_n}]

```

此例展示了如何为一对差分信号设置延迟链(Delay Chain),来确保信号对的匹配延迟。

通过上述示例和代码,我们可以看到XDC约束的高级应用在确保设计可靠性、性能优化以及功能正确性方面发挥了重要作用。理解并运用高级语法特性,能够极大地提高设计的灵活性和效率。

# 3. XDC约束在项目中的实践应用

在深度理解XDC约束的基础知识和高级语法之后,本章节将详细探讨XDC约束在实际项目中的应用,从设计优化、资源管理到调试过程的方方面面。我们将深入分析约束如何影响项目质量、如何在实际开发中处理资源分配的冲突,并提供实用的调试方法。

## 3.1 约束在设计优化中的作用

### 3.1.1 优化设计的约束策略

在数字逻辑设计领域,约束不仅是实现预期设计的保障,还是进行设计优化的关键工具。XDC约束允许设计者明确指定设计的某些方面,这些方面包括时序、I/O位置和资源使用等,从而引导综合工具对设计进行优化。

例如,设计者可以通过设置时钟约束确保数据在预定的时钟沿准时采样。更进一步,约束可以精细调整以满足特定的性能指标,例如延迟和功耗,这些指标是决定设计成功与否的关键因素。

一个常见的约束策略是先设置基本的时序约束,然后逐步引入更高级的约束条件,比如多周期路径和false paths。这样可以帮助设计者逐步优化设计,同时确保每次更改都不会引入新的时序问题。

0

0