【Vivado IP集成基础】:简化复杂设计,掌握高效集成的10大技巧

发布时间: 2024-11-13 23:31:33 阅读量: 36 订阅数: 28

Xilinx Vivado IP库

# 1. Vivado IP集成概述

在现代FPGA和SoC设计中,Vivado IP集成是一个重要的步骤,它涉及到将预先设计好的IP(Intellectual Property)核心集成到更大的系统设计之中。IP核能够显著提高开发效率,缩短产品上市时间,并确保设计的可重用性和可靠性。

IP集成工作流程通常包括选择合适的IP核,对其进行配置和定制,然后将其封装成符合特定接口标准的形式。在集成过程中,设计者必须考虑IP核与整体设计的兼容性、性能和资源占用等关键因素。

本章将作为全文的导引,简要介绍Vivado IP集成的相关概念,为进一步深入探讨IP核的配置、仿真验证、综合实现以及优化策略等后续内容奠定基础。在下一章,我们将深入探讨IP核的基础知识,从而更好地理解IP集成的复杂性和其在现代电子设计中的重要性。

# 2. 理解Vivado IP核基础

### 2.1 IP核的定义与分类

#### 2.1.1 内置IP核与第三方IP核的区别

在现代FPGA(现场可编程门阵列)设计中,IP核(Intellectual Property Core)是可重复使用的设计单元,它们可以被集成到更大的系统中,以减少设计复杂性并缩短设计周期。在Xilinx的Vivado设计套件中,IP核主要分为两类:内置IP核和第三方IP核。

内置IP核是Vivado软件自带的,它们通常已经过优化,可以直接集成到设计中。内置IP核的优点包括:

- **性能优化**:内置IP核经常与FPGA硬件紧密集成,能够提供最佳性能。

- **可靠性**:由于是官方提供的,因此内置IP核拥有较高的质量和文档支持。

- **易于集成**:因为是Vivado的一部分,所以内置IP核与Vivado的集成工作流程无缝对接。

第三方IP核是由独立开发者或公司开发的,它们可以在Xilinx的IP Catalog中找到,也可以从其他来源获取。第三方IP核的优势在于:

- **多样性**:第三方IP核往往覆盖更广泛的应用需求,因为内置IP核更注重通用性和性能优化。

- **创新性**:第三方开发者可能会提供更为新颖的解决方案和设计。

- **灵活定制**:第三方IP核通常支持更广泛的定制选项,满足特定设计需求。

然而,第三方IP核的使用也存在一些潜在风险,例如可能需要额外的集成工作、可能缺乏必要的文档和支持,以及可能存在兼容性问题。

在选择IP核时,设计者应当根据项目需求、预算、支持和维护等因素综合考虑,选择最适合其设计的IP核。

### 2.1.2 IP核的选择标准和应用场景

在选择合适的IP核时,设计者需要考虑多个因素来决定最合适的IP核。以下是选择IP核时可能需要考虑的标准:

- **性能要求**:是否需要高性能优化,比如对速度、资源消耗或功耗有特别的要求。

- **资源占用**:IP核占用的逻辑资源和内存资源是否在设计限制之内。

- **兼容性**:IP核是否与目标FPGA设备兼容,以及与其他系统组件的兼容性如何。

- **价格和许可**:IP核的成本以及获得许可的条款和条件。

- **支持与维护**:供应商是否提供及时的技术支持和是否经常更新IP核以修复问题和改进性能。

在应用场景方面,IP核的使用取决于设计的具体需求。例如:

- **数据处理**:需要高速数据处理能力时,可以考虑使用内置或第三方的高性能处理器核。

- **接口协议**:当设计需要与外部设备通信时,可以根据需要选择适当的串行通信协议IP核,如PCIe、SPI、I2C等。

- **信号处理**:信号处理应用可能会用到FFT(快速傅立叶变换)、FIR(有限冲击响应)滤波器等专用的数学运算IP核。

在实际设计中,设计者往往需要综合考虑以上标准和应用场景,选择最合适的IP核。最终目标是在满足设计需求的同时,实现成本效益的最佳平衡。

### 2.2 IP核的配置与定制

#### 2.2.1 基于GUI的IP配置方法

Vivado提供了一个直观的图形用户界面(GUI)来配置IP核,这使得用户即使没有深厚的技术背景也能相对容易地完成配置。基于GUI的IP配置过程通常包括以下步骤:

1. 打开Vivado的IP Catalog,浏览可用的IP核列表。

2. 双击所需IP核条目或将其拖放到设计中。

3. 运行IP核生成器,以GUI的形式配置IP核的各种参数。

4. 在向导中,根据设计需求选择或者输入参数值,如数据宽度、时钟频率、协议参数等。

5. 完成配置后,点击“Generate”生成IP核。

6. Vivado将自动创建一个包含该IP核的本地库,并在设计中实例化该IP核。

通过这种方式,用户可以直观地看到每个参数对IP核功能和性能的影响。配置完成后,Vivado会自动更新设计约束文件和代码,以确保IP核的正确集成。

#### 2.2.2 使用Tcl脚本进行IP核定制

虽然基于GUI的配置方式在许多情况下非常方便,但在自动化或重复性任务中,使用Tcl(Tool Command Language)脚本来配置IP核可以显著提高效率。通过编写Tcl脚本,设计者可以自动化整个IP核的配置流程,以及实现IP核的版本控制和脚本可重复使用。

使用Tcl脚本配置IP核的基本步骤如下:

1. 创建一个Tcl脚本文件,并在其中定义IP核配置的参数。

2. 使用Vivado的IP包中的命令,如`create_ip`、`set_property`等,来定义IP核的属性值。

3. 运行Tcl脚本,自动完成IP核的配置。

例如,以下是一个简单的Tcl脚本示例,用于配置一个AXI接口的IP核:

```tcl

# 创建一个IP核实例

create_ip -name axi_protocol_checker -module_name axi_check

# 设置IP核的属性

set_property -name "SUPPORTS_NARROWTRANSFERS" -value "1" -objects [get_ips axi_check]

set_property -name "SUPPORTS_WRITE_RESPONSE" -value "1" -objects [get_ips axi_check]

# 激活IP核生成器

launch_ip核_generator

```

Tcl脚本的灵活性使其成为IP核定制的强大工具,尤其是在需要处理大量IP核或需要在多个项目中重用配置时。

#### 2.2.3 IP核参数化设计的重要性

参数化设计是IP核开发中的一个关键概念。它允许设计者在实例化IP核时为其提供不同的参数值,以适应不同的设计需求。通过参数化设计,可以创建更为通用和灵活的IP核,这在多项目或需要多次定制的环境中尤为有用。

参数化设计的优点包括:

- **灵活性**:设计者可以轻松地调整IP核的功能以满足不同的设计需求。

- **重用性**:一个参数化设计的IP核可以在多个项目中重复使用,无需每次都进行重大修改。

- **维护性**:当IP核更新或需要进行修复时,通过修改参数值可以快速适应。

例如,一个参数化设计的FIFO IP核可以根据提供的数据宽度和深度参数,自动配置其内部的逻辑。这种灵活性使得设计者无需为每种可能的FIFO大小编写和维护单独的IP核。

在Vivado中,通过Tcl脚本或GUI,设计者可以设置和修改这些参数来定制IP核的功能和性能。在参数化设计中,IP核的基本架构保持不变,但其行为可以根据不同的参数设置来调整。

### 2.3 IP核的封装与接口标准

#### 2.3.1 AXI接口规范简介

高级可扩展接口(Advanced eXtensible Interface,AXI)是ARM公司开发的一套面向高性能、高频率系统设计的总线接口协议。AXI接口规范特别适合用于FPGA设计中,它是作为AMBA(高级微控制器总线架构)的一部分提供的。

AXI的主要特点包括:

- **分离的地址/控制和数据通道**:提供了独立的读写地址、控制和数据通道,有助于提高性能。

- **支持非连续的传输**:可以处理不连续的内存地址传输,优化数据流。

- **支持乱序传输**:允许读写操作以任意顺序完成,增加了灵活性并减少了延迟。

- **支持burst传输**:允许数据以数据包的方式传输,提高带宽利用率。

在Vivado中,设计者可以通过内置的AXI IP核生成器来创建各种AXI接口IP核,例如AXI4-Stream、AXI4-Lite和AXI4等。这些IP核有助于简化复杂的通信协议的实现,并确保与ARM处理器或其他支持AXI协议的设备兼容。

#### 2.3.2 用户自定义接口的实现策略

虽然Vivado提供了多种内置的接口标准,但在某些特定应用场景中,设计者可能需要创建用户自定义的接口协议。以下是实现用户自定义接口的一些策略:

1. **定义协议规范**:首先,需要清晰地定义用户自定义接口的协议规范,包括信号名称、信号功能、传输时序和同步机制。

2. **设计接口IP核**:根据协议规范设计相应的接口IP核。这可能需要使用Vivado提供的IP包中的基础构建块,如FIFO、计数器、状态机等。

3. **使用Vivado IP包**:Vivado IP包中的组件可以用来实现复杂的逻辑,如协议转换、数据缓存、错误检测等。

4. **封装和实例化**:在设计好用户自定义接口IP核后,需要对其进行封装,并在主设计中实例化。

例如,考虑一个简单的用户自定义接口,它需要一个简单的握手协议。一个Tcl脚本片段可能如下所示:

```tcl

# 创建一个用户定义的IP核

create_ip -name user_defined_interface -module_name custom_if

# 设置IP核的参数

set_property -name "DATA_WIDTH" -value "32" -objects [get_ips custom_if]

set_property -name "CLOCK_FREQ" -value "100MHz" -objects [get_ips custom_if]

# 实例化IP核

create_bd_***:user_defined_interface:1.0 custom_if_0

```

用户自定义接口的设计和实现需要对硬件设计有深入的理解,并且可能需要对设计进行严格的验证,以确保接口的可靠性和性能。

### 2.4 IP核的验证与仿真

在设计集成IP核时,验证是至关重要的步骤。验证能够确保IP核按照预期工作,并且与设计的其他部分兼容。

#### 2.4.1 仿真环境的搭建

为了验证IP核,首先需要搭建一个适当的仿真环境。仿真环境的搭建通常包括以下步骤:

1. **创建仿真项目**:在Vivado中创建一个新的仿真项目,这将包括设计文件、测试平台、和仿真脚本等。

2. **编写测试平台**:测试平台(Testbench)是一个专用的硬件描述语言(HDL)模块,用于模拟IP核的外部环境并提供输入激励。

3. **运行仿真**:使用Vivado的仿真工具运行测试平台,以验证IP核的行为。

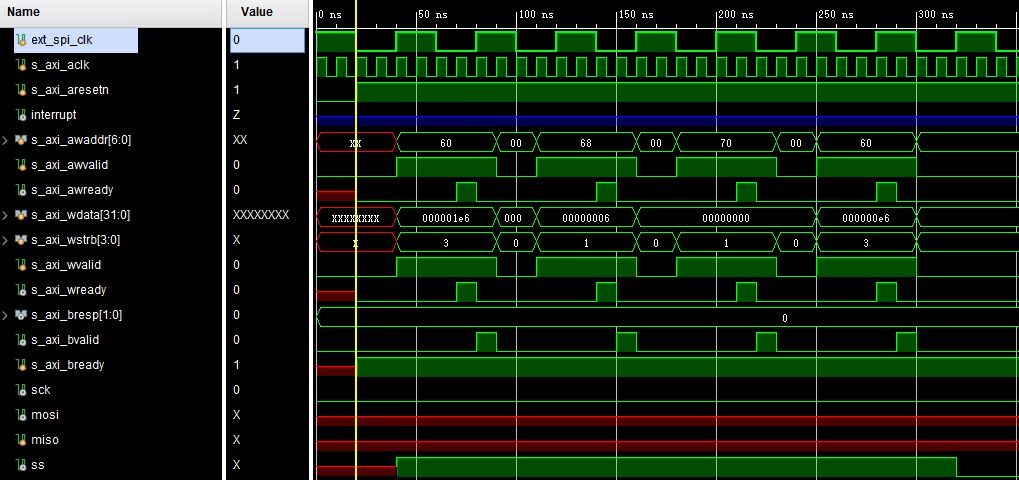

4. **分析仿真结果**:观察仿真波形图和日志文件来检查IP核是否正确响应输入激励,并执行了预定功能。

下面是一个简单的Verilog测试平台示例:

```verilog

module testbench;

// 信号声明

reg clk;

reg reset;

reg [31:0] data_in;

wire [31:0] data_out;

// 实例化待验证的IP核

my_ip核 uut (

.clk(clk),

.reset(reset),

.data_in(data_in),

.data_out(data_out)

);

// 生成时钟信号

initial begin

clk = 0;

forever #10 clk = ~clk; // 产生50MHz的时钟

end

// 测试激励

initial begin

// 初始化信号

```

0

0