【Vivado中的逻辑分析仪使用技巧】:捕捉设计中的细微问题,确保无遗漏

发布时间: 2024-11-13 23:51:24 阅读量: 57 订阅数: 28

Vivado使用教程.zip_vivado中文教程_vivado使用教程_vivado指南_vivado教程_vivado视频教

# 1. Vivado中的逻辑分析仪概述

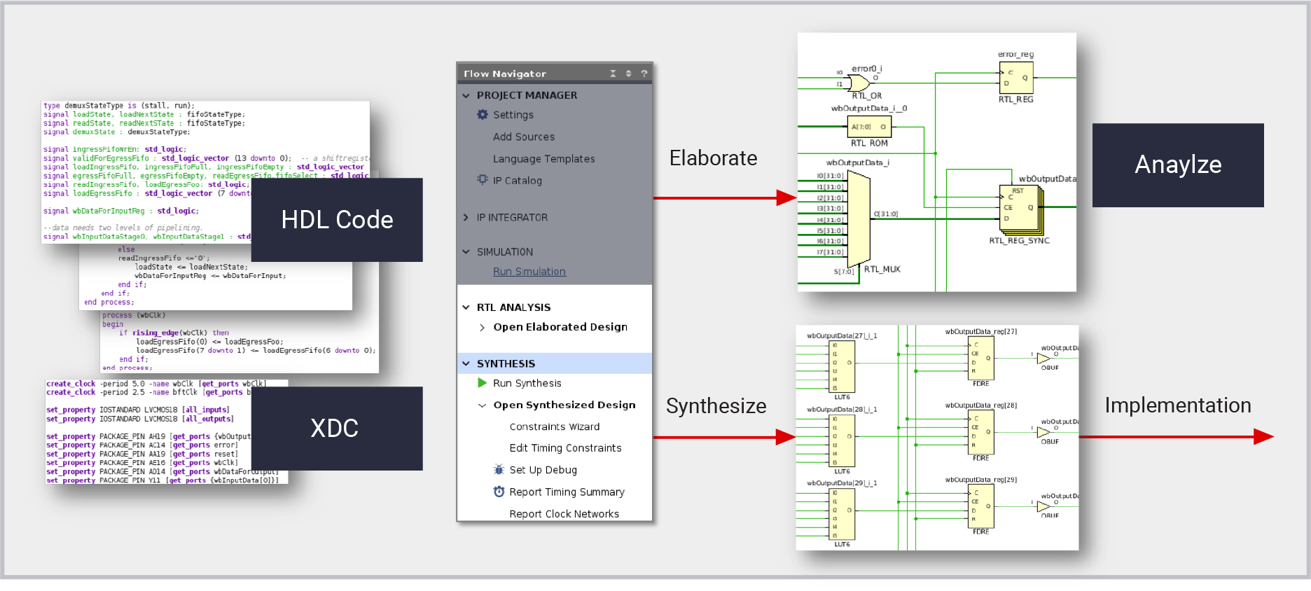

Vivado是Xilinx公司推出的集成设计环境,广泛应用于FPGA设计与分析中。逻辑分析仪是Vivado的重要组成部分,用于在FPGA设计的调试过程中捕捉和分析信号。对于设计人员来说,理解并高效利用逻辑分析仪对于识别和解决硬件设计问题至关重要。

在本章中,我们将简要介绍逻辑分析仪的基础知识,涵盖其在Vivado中的作用和基本操作。紧接着,第二章将深入探讨逻辑分析仪的使用细节,第三章讨论其高级应用,而第四章则集中于数据分析的可视化和报告生成。最后,第五章通过案例研究与实战演练,提供实际操作的经验分享。

逻辑分析仪通过提供实时数据流监控,帮助设计人员观察内部信号状态,诊断电路中的故障,并对信号完整性和时序进行分析。它具有灵活的触发设置,能够准确地捕获感兴趣的数据区间,极大地简化了硬件调试的复杂度。

接下来,我们将深入到逻辑分析仪的基础使用方法,探讨其在日常设计和调试工作中的实用性。

# 2. 逻辑分析仪的基础使用

### 2.1 逻辑分析仪界面布局和功能

#### 2.1.1 主要视图和面板介绍

在 Vivado 设计套件中,逻辑分析仪是设计验证与调试的关键工具,其界面布局直观且功能丰富,可以高效地帮助工程师对FPGA中的信号进行捕获和分析。逻辑分析仪的界面由以下几个主要视图和面板组成:

- **配置视图**:在此区域,用户可以设置触发条件,定义信号捕获深度和时钟源等。

- **数据视图**:一旦信号被成功捕获,数据视图会以表格或波形形式展示信号数据。

- **控制面板**:用于启动信号捕获、停止、保存数据和重置逻辑分析仪等操作。

- **触发设置面板**:允许用户配置复杂的触发条件,包括状态、边沿和脉冲触发。

界面布局的设计使用户能够轻松地在不同视图间切换,并且可以自定义工作区,以适应不同的工作习惯和需求。通过这些视图和面板,用户可以快速配置和操作逻辑分析仪,实时监控和调试FPGA设计。

```mermaid

graph TB

A[开始] --> B[打开逻辑分析仪]

B --> C[配置视图]

B --> D[数据视图]

B --> E[控制面板]

B --> F[触发设置面板]

C --> G[设置触发条件]

D --> H[查看捕获数据]

E --> I[操作信号捕获]

F --> J[高级触发配置]

```

### 2.1.2 触发器和条件设置

触发器是逻辑分析仪中不可或缺的组件,它定义了信号捕获的开始和结束点。在Vivado中配置触发条件通常涉及以下步骤:

1. **选择触发通道**:选择你希望作为触发依据的信号通道。

2. **设置触发模式**:有多种模式可供选择,如边沿触发、脉冲宽度触发、序列匹配触发等。

3. **配置触发条件**:根据实际调试需求,设置具体触发条件,比如上升沿、下降沿、高电平或低电平等。

4. **设置触发点**:在时间线上指定触发的具体位置,例如在第100个时钟周期触发。

5. **验证触发设置**:通过预览功能检查配置是否符合预期。

```mermaid

graph TB

A[开始] --> B[打开触发设置面板]

B --> C[选择触发通道]

C --> D[设置触发模式]

D --> E[配置触发条件]

E --> F[设置触发点]

F --> G[验证触发设置]

G --> H[捕获信号并分析]

```

通过精心设置触发器和条件,用户可以有效地定位设计中的问题,例如数据竞态、未知状态的产生等问题,从而加速调试进程,提升工作效率。

# 3. 逻辑分析仪的高级应用

## 3.1 复杂信号的分析技术

在数字电路设计和调试过程中,复杂信号的分析往往成为验证设计正确性的关键。逻辑分析仪在此过程中扮演着至关重要的角色,特别是在面对多通道信号和高级触发条件时。

### 3.1.1 多通道同步捕获

在复杂系统中,多个信号间可能存在着依赖关系,因此同时捕获多个信号通道对于理解系统行为至关重要。使用逻辑分析仪的多通道同步捕获技术,设计者可以确保不同信号间的时间关系得到精确记录和分析。

**应用多通道同步捕获的步骤如下:**

1. **确定同步要求**:首先确定需要同步捕获的通道数量和它们之间的关联。

2. **配置分析仪**:在逻辑分析仪的设置界面中,选择相应的通道并将它们分组,以保证同步捕获。

3. **设置采样率**:确保逻辑分析仪的采样率足够高,以便准确地记录信号状态变化。

4. **执行捕获**:启动捕获过程,同时观察所有通道上的信号状态变化。

**示例代码:**

```c

// 伪代码 - 用于设置多通道同步捕获的逻辑分析仪配置

//

```

0

0