【Vivado与FPGA资源分配】:高效利用硬件资源,实现资源优化的3大原则

发布时间: 2024-11-13 23:54:53 阅读量: 132 订阅数: 28

Spartan-3 系列 FPGA 用户指南.rar

# 1. Vivado与FPGA资源分配概述

现代FPGA的设计和实现涉及到复杂的资源分配问题。Vivado作为Xilinx公司推出的综合设计套件,它提供了强大的资源管理和分配工具,支持从逻辑资源到存储资源再到I/O资源的详细配置。本章节旨在为读者概述Vivado在FPGA资源分配中的角色,以及如何通过Vivado优化FPGA项目以确保资源得到最有效的使用。

## 1.1 FPGA资源分配的重要性

在FPGA设计中,资源分配的优劣直接关系到项目的性能、功耗和成本。资源分配不当可能会导致设计无法满足时序要求,或者浪费宝贵的硅片面积。Vivado作为一个集成设计环境,它的一个核心功能就是帮助设计者合理分配这些资源,以达到设计优化的目的。

## 1.2 Vivado工具在资源分配中的作用

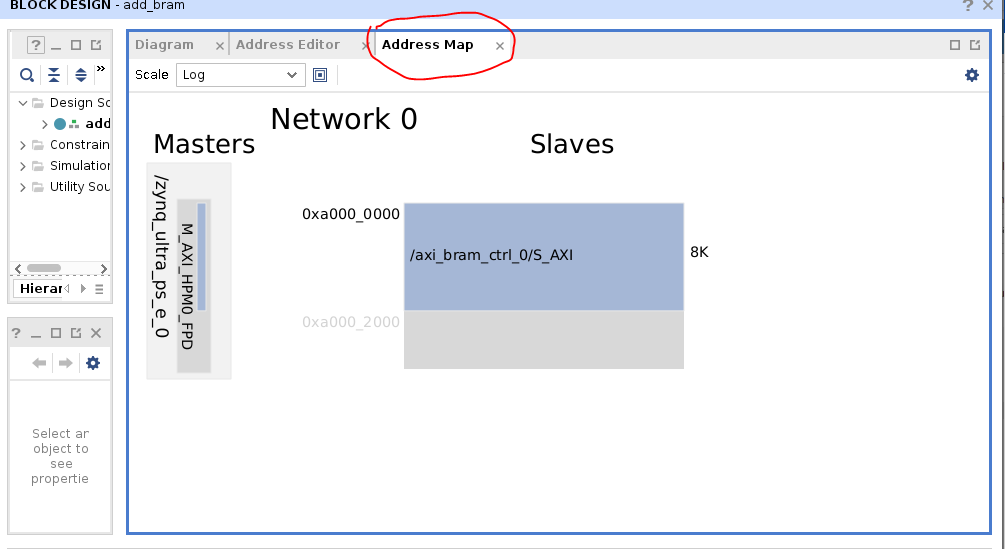

Vivado提供了直观的用户界面、高级的综合算法和多种约束选项,使得工程师能够轻松地管理资源分配。通过图形化界面,用户可以直观地看到设计中资源的使用情况,并实时调整配置来优化设计。利用Vivado的约束文件,可以精确地控制逻辑、存储和I/O资源的分配,确保设计达到最佳性能。

## 1.3 本章小结

本章为读者介绍了Vivado与FPGA资源分配的基础概念,并强调了资源分配对于FPGA设计成功的重要性。通过接下来的章节,我们将深入探讨Vivado如何帮助工程师高效地管理FPGA资源,以及如何在实际设计中应用这些知识。

# 2. FPGA资源类型和特性

## 2.1 逻辑资源的介绍和管理

### 2.1.1 查看和评估逻辑资源

逻辑资源是FPGA中实现各种功能的核心部分,主要包括查找表(LUTs)、触发器(Flip-Flops)、可编程互连等。查看和评估逻辑资源对于优化设计至关重要。在Vivado中,我们可以使用多种方法来查看和评估这些资源的使用情况:

- **使用资源利用率报告**:通过Vivado的资源利用率报告,可以查看LUTs、Flip-Flops的使用情况,以及它们在整个设计中的分布情况。这些报告通常以百分比和数量的形式展现,帮助我们快速定位资源瓶颈。

```mermaid

graph LR

A[开始] --> B[打开Vivado项目]

B --> C[查看资源利用率报告]

C --> D[分析LUTs和Flip-Flops的使用]

D --> E[确定资源瓶颈]

```

- **使用资源分析器**:Vivado提供了一个图形化界面的资源分析器,它可以详细地展示每个资源组件的使用情况。用户可以通过资源分析器筛选不同的资源类型,甚至查看特定模块的资源使用情况,这有助于精确识别资源使用不均的问题。

- **脚本与命令行工具**:除了图形界面外,Vivado还提供了一系列的TCL命令来获取资源使用信息。例如,`report_utilization`命令可以生成详细的资源使用报告。

### 2.1.2 逻辑资源的优化策略

逻辑资源优化是一个持续的过程,旨在提高资源使用效率并减少资源消耗。以下是一些常见的优化策略:

- **逻辑优化**:在HDL代码阶段,逻辑优化主要是通过代码重构来减少资源消耗。例如,可以移除不必要的逻辑门,合并相同功能的逻辑块等。

```vhdl

-- 示例代码,展示逻辑优化前后的差异

-- 优化前

architecturertl of my_entity is

begin

process(a, b)

begin

if (a = '1') then

y <= b AND c;

else

y <= b OR c;

end if;

end process;

end architecture;

-- 优化后

architecture optimized of my_entity is

begin

y <= b AND c when a = '1' else b OR c;

end architecture;

```

- **重新映射**:在综合和实现过程中,重新映射是通过工具自动优化资源的分配和连接。Vivado中的实现策略,如`ExploreWithRemap`,可以在不同映射配置之间探索,优化逻辑资源使用。

- **资源分配**:合理分配逻辑资源,比如将特定的逻辑部分固定到FPGA的特定区域,可以减少互连资源的消耗,并可能提高性能。

## 2.2 存储资源的介绍和管理

### 2.2.1 不同类型的存储资源

FPGA内部的存储资源对于实现各种算法和存储任务至关重要。FPGA的存储资源类型主要包括:

- **块存储器(Block RAMs, BRAMs)**:FPGA中的BRAM是相对较大的存储单元,通常用来存储较大的数据集或作为缓冲区使用。

- **寄存器文件(Register Files)**:寄存器文件是在逻辑层面实现的存储单元,可以用来存储较小的数据集,通常在逻辑优化中创建。

- **分布式存储(Distributed Memory)**:分布式存储可以利用查找表(LUTs)内的存储资源,适合存储小规模、随机访问的数据。

### 2.2.2 存储资源分配的最佳实践

为了高效利用FPGA中的存储资源,以下是一些最佳实践:

- **综合时的存储优化**:在综合阶段就考虑存储结构,可以有助于减少不必要的存储资源浪费,比如通过合并简单的存储操作来减少BRAM资源的使用。

- **使用存储资源适配器**:Vivado提供了多种存储资源适配器,可以自动将HDL代码中的数组和向量映射到FPGA的存储资源中。

```tcl

# 使用TCL脚本自动适配存储资源

create_auto_instance -name my_array -hierarchy [get_ports my_array]

```

- **手动指定存储资源**:在某些情况下,手动指定特定的存储资源比自动适配更有效。可以使用Xilinx的属性和约束来手动指定存储资源。

## 2.3 输入/输出资源的介绍和管理

### 2.3.1 I/O引脚和I/O标准

FPGA的输入/输出(I/O)资源包括引脚和相应的I/O标准。I/O标准如LVDS、HSTL、SSTL等,定义了电气特性、信号电平、驱动能力等。正确使用I/O标准和引脚对于确保信号完整性和系统性能是至关重要的。

- **I/O标准的选择**:根据系统的要求选择合适的I/O标准。例如,如果系统需要高速串行通信,则可能需要使用HSTL或SSTL标准。

- **引脚定位**:I/O引脚的位置直接影响布线的复杂度和信号完整性。FPGA通常提供引脚规划器工具,可以手动或自动规划引脚位置。

### 2.3.2 I/O资源分配的技巧和方法

I/O资源的分配需要考虑信号的同步、时序要求和信号的可靠性。以下是一些有效的技

0

0