基于Proteus的十进制加减可逆计数器设计与仿真

版权申诉

本次课设报告聚焦于十进制加/减可逆计数器的设计与实现,旨在深入理解并掌握计数器在数字电路中的基础应用。首先,计数器作为数字逻辑的核心组件,其重要性不言而喻,特别是MSI集成计数器因其功能多样性和灵活性被广泛应用。课程目标包括熟悉计数器的工作原理,学会利用Proteus等EDA软件进行电路仿真,以及实际安装和调试。

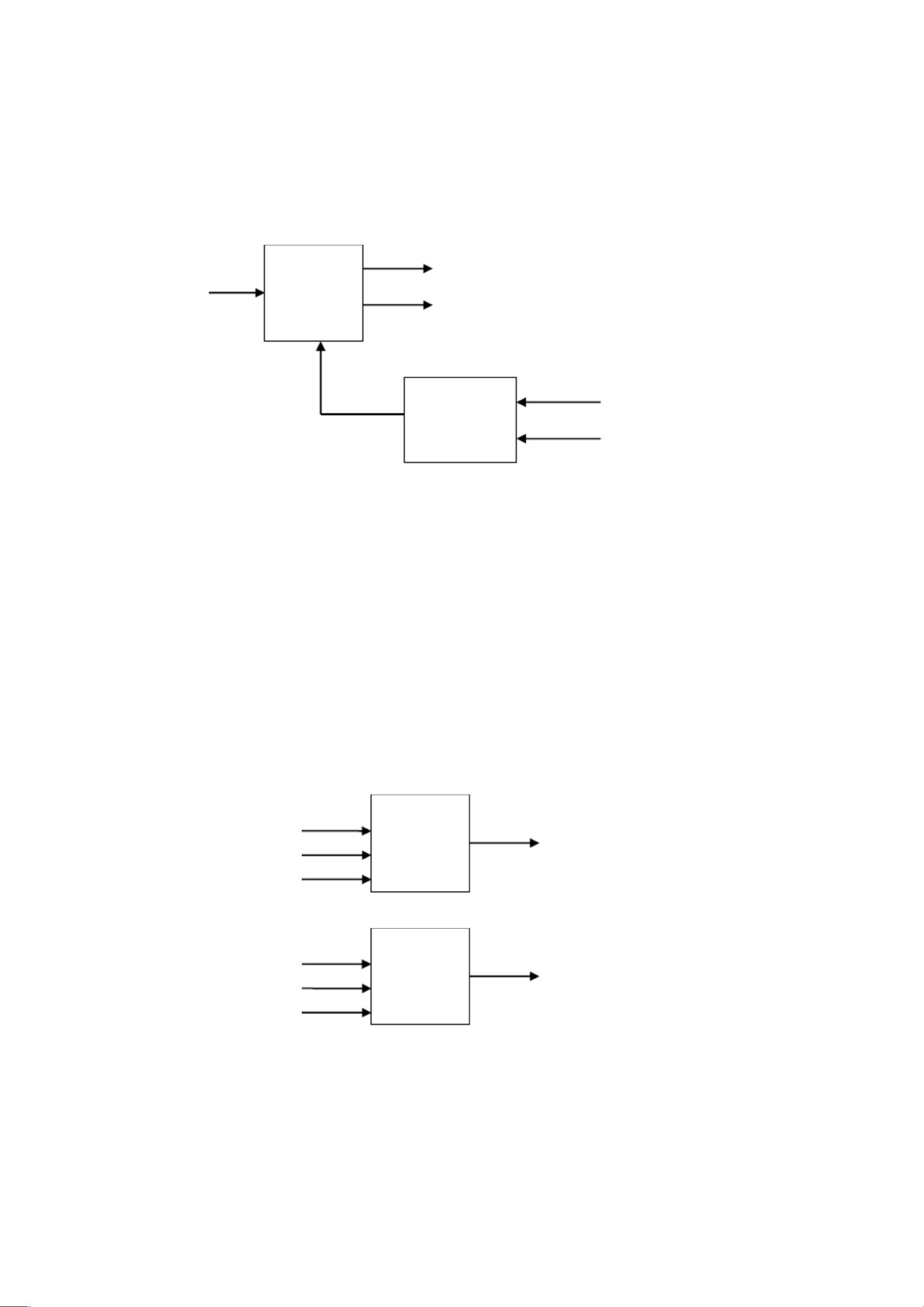

设计方案部分,报告提出两种主要的计数器设计思路:一是手动控制的手动加/减计数器,设计思路围绕如何通过外部输入控制来实现计数的增加或减少;二是自动控制的可逆方式计数器,设计上侧重于内部逻辑的自启动和循环工作模式,确保计数的连续性和可逆性。此外,还涉及到脉冲发生电路、加/减/计数器控制电路的具体实现,包括基本原理的阐述和关键参数的选择与计算。

在电路实现方面,报告详细介绍了脉冲信号的产生,包括其基本工作原理和参数设置,以及如何通过特定的控制逻辑来实现计数器的加、减和可逆操作。对于自动控制可逆计数器的实现,设计者可能会利用时钟脉冲和触发器等元件,确保计数状态能够在0到M-1(M为计数器模数)之间无缝切换。

译码显示单元电路的设计同样重要,如提到的74LS48译码器,它用于将计数结果转化为易于观察的输出形式,如LED数码管显示。这部分内容不仅涉及硬件电路设计,还包括了编码与解码的过程以及如何确保输出信息的准确性。

整个设计过程会遵循一定的步骤,从需求分析到电路设计、仿真验证,再到实际电路制作和测试,每一步都需要严谨对待。报告的结尾会总结课设的体会,可能包括技术挑战、学习收获以及对未来工作的展望。这份报告不仅提供了一个实际的项目案例,也强化了学生对数字电路理论知识的实践运用能力。

2022-06-12 上传

2022-10-16 上传

2022-10-18 上传

2023-06-10 上传

2023-02-24 上传

2023-05-30 上传

2023-05-31 上传

2023-05-31 上传

2023-09-04 上传

xxpr_ybgg

- 粉丝: 6787

- 资源: 3万+

最新资源

- 关于skinmagic的使用说明

- 2009计算机考研大纲

- Applied Java Patterns 英文版 (pdf)

- More Effective C++ 中文PDF版

- 非常有用的EMC秘笈

- 网上数据库大学论文(参考)

- Java泛型技术之发展.pdf

- AJAX In Action(中文版)

- FastReport 3.0 设计手册PDF_SC.pdf

- 批处理常用命令及用法大全

- wSOCKET编程--------------------------------

- 经典c程序100例 很久就收藏了

- SQL例句大全,各种sql基本语法均有

- FLASH四宝贝之-使用ActionScript.3.0组件.pdf

- Oracle常用傻瓜问题1000答

- flxe 3.0 教材PDF版