HINK-E0213A95 2.13英寸EPD模块规格说明书

“HINK-E0213A95规格说明书” 本文档是关于HINK-E0213A95型号的电子纸显示模块的详细规格说明书,主要用于阐述该产品的技术参数、功能特性以及应用范围。HINK-E0213A95是一款2.13英寸的电子纸显示模块,版本号为A4,由Daisy Zhu负责更新和改进。 1. 一般描述 HINK-E0213A95是一款2.13英寸的电子纸显示器,适用于需要低功耗、高对比度和长时间阅读的场景。该模块采用E-Ink电子纸技术,能提供接近纸质的阅读体验,减轻眼睛疲劳。其设计可能包括了边框波形控制、显示更新控制以及刷新时间要求等关键功能,以确保图像质量和响应速度。 2. 特性 - 低功耗:电子纸显示技术在静态状态下几乎不消耗电能,大大降低了设备的总能耗。 - 高对比度:提供清晰的黑白显示,适合文字和图形的呈现。 - 多次刷新选项:支持不同的刷新策略,以优化显示性能和响应速度。 - 可靠性测试:经过多次版本迭代,包括可靠性测试,确保产品在各种环境下的稳定运行。 3. 应用 HINK-E0213A95可能被广泛应用于: - 电子阅读器:用于展示电子书籍、文档或杂志。 - 智能标签:在零售商店中显示价格、产品信息或促销信息。 - 无纸化办公:在便携式设备上显示日程、备忘录等。 - 智能穿戴设备:如智能手表的辅助显示界面。 - 公共信息显示:如公交站牌、广告屏幕等。 4. 机械规格 这部分通常会包含模块的物理尺寸、接口类型、连接器位置以及安装指南等信息。例如,它可能会详细列出模块的宽度、高度、厚度,以及任何必要的安装孔位和间距,以便于集成到不同设备的设计中。 5. 电气特性 A4版本的更新可能涉及到直流特性,这涵盖了模块的工作电压、电流需求、电源稳定性以及电磁兼容性(EMC)要求等。这些数据对于确保模块与系统电源兼容至关重要。 6. 控制命令 文档中提到了“命令表”,这可能是指与HINK-E0213A95交互所需的通信协议和指令集,用于控制显示内容的更新、翻页效果以及其他高级功能。 7. 审批流程 最后,文档中提到了一个客户审批流程,如果接收方在15天内未提出异议,则视为同意规格书内容。这表明HINK-E0213A95在推出前需要经过严格的验证和确认。 HINK-E0213A95是一款经过多轮改进的电子纸显示模块,具备出色的节能特性和良好的显示效果,适用于多个领域,且在设计和制造过程中考虑到了可靠性和用户需求。

剩余41页未读,继续阅读

信息提交成功

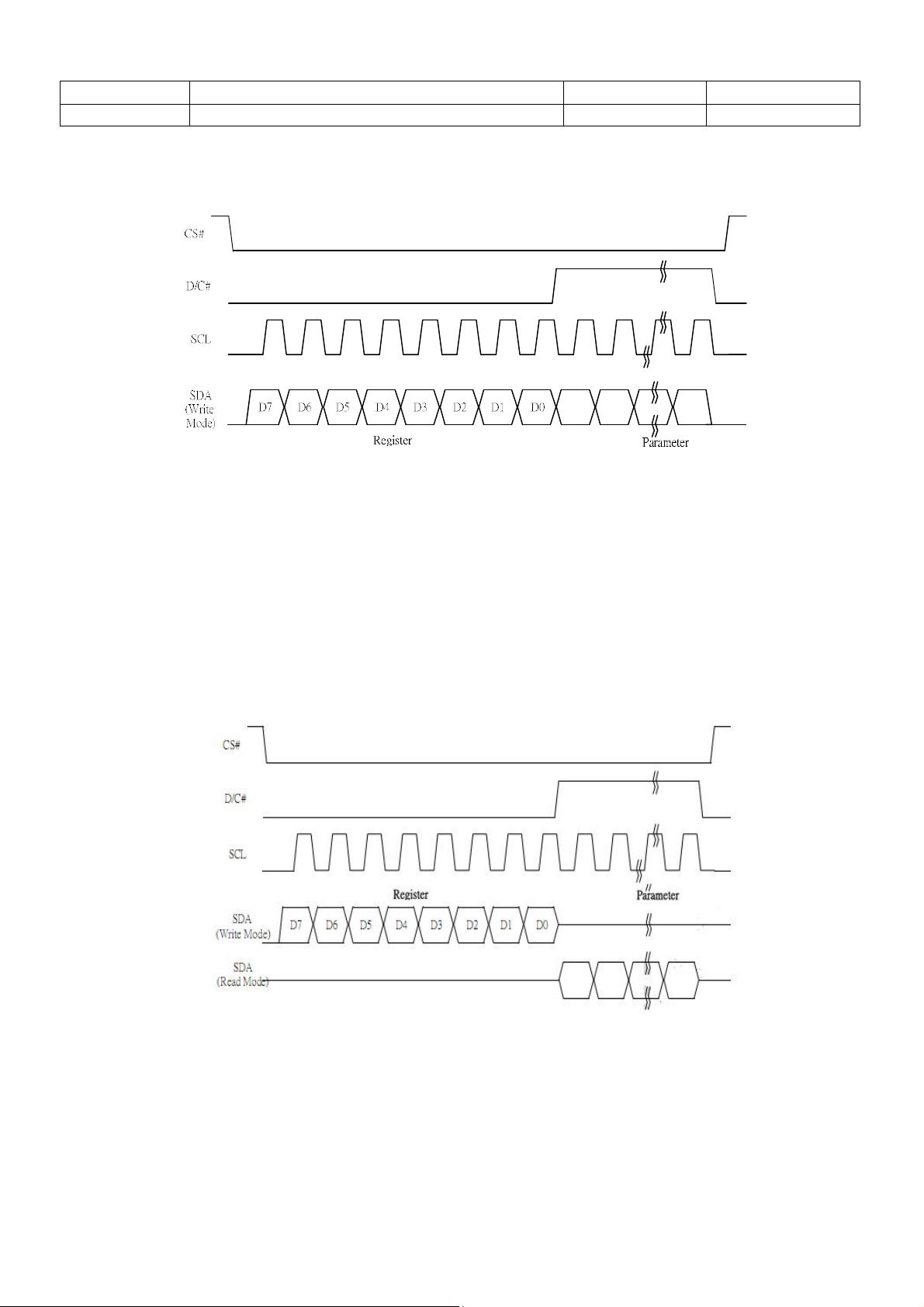

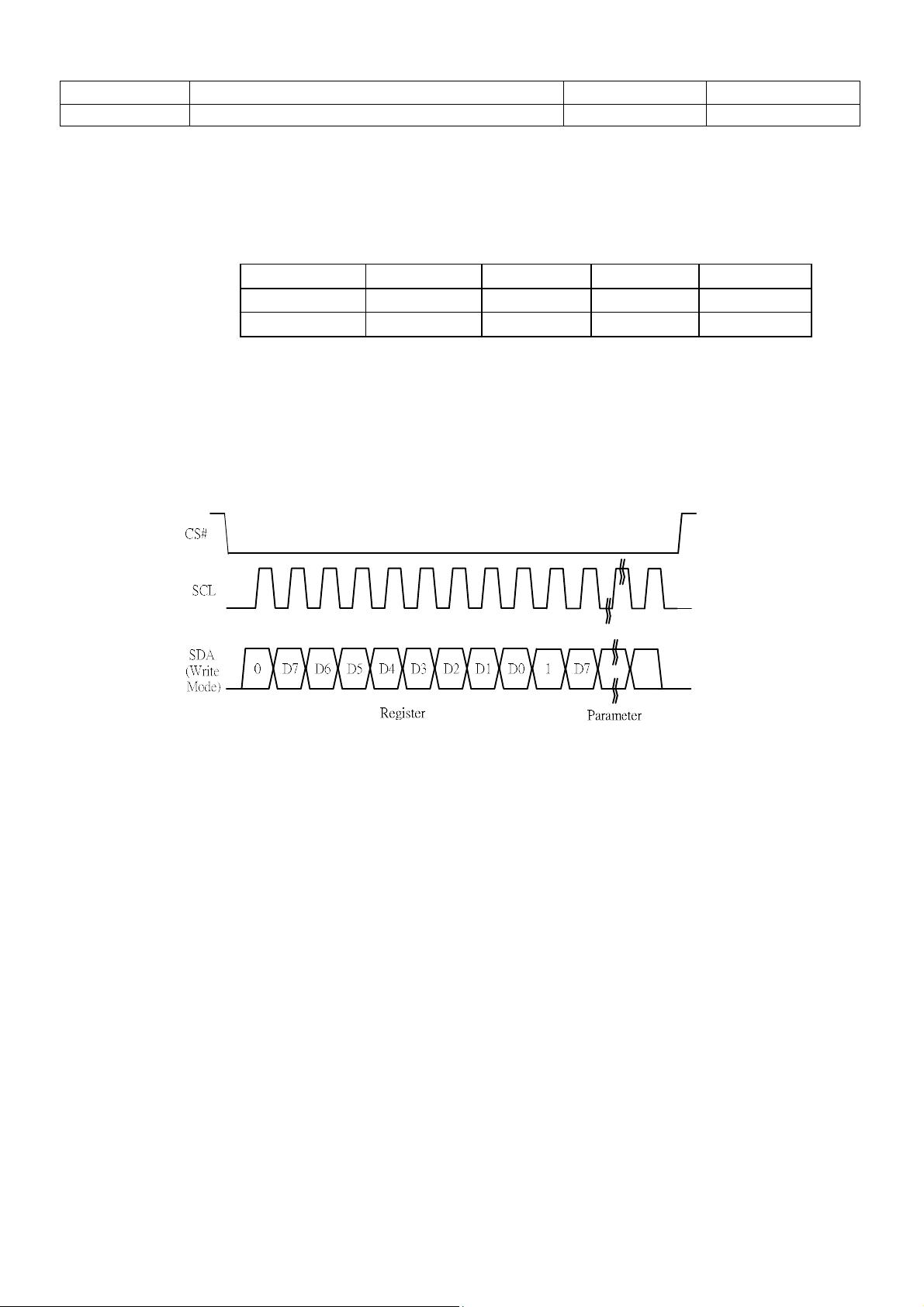

信息提交成功