FPGA实现SDRAM控制:高效FIFO设计

25 浏览量

更新于2024-08-29

收藏 270KB PDF 举报

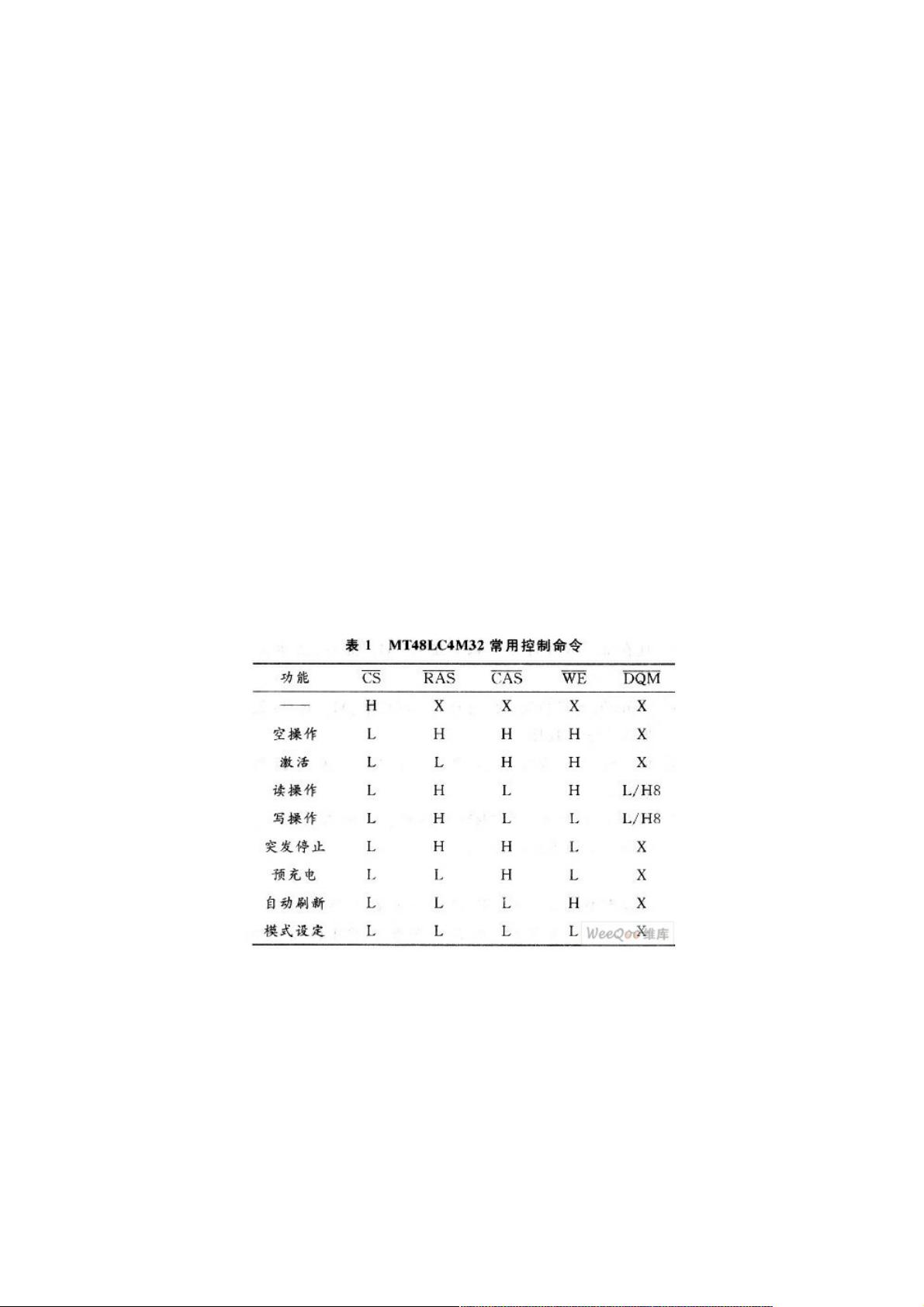

"基于FPGA的FIFO设计和应用,用于解决DSP实时跟踪视频时的数据存储问题,通过FPGA控制SDRAM实现高速缓存,降低商业成本。FPGA选择是因为其可编程性和灵活性,SDRAM选为存储器因其大容量、低价格及高效传输速度。FIFO性能受限于SDRAM的工作频率和突发长度。设计示例采用MT48LC4M3282 SDRAM芯片,具备特定的控制信号和命令集。FIFO系统由FPGA和SDRAM构成,FPGA内含FIFO模块、缓冲器和SDRAM控制器。"

在基于FPGA的FIFO设计中,首要任务是解决DSP系统中高速图像采集的数据存储需求。由于DSP自带的FIFO无法满足这种高容量、高速度的要求,因此需要寻找替代方案。FPGA(Field-Programmable Gate Array)因其可定制化和高性能被选中,它能够作为桥梁,实现对SDRAM(Synchronous Dynamic Random-Access Memory)的控制,以提供更大的数据存储和快速访问能力。

在器件选择上,SDRAM成为理想的存储器,因为它的容量大、价格相对较低,并且其数据突发传输模式可以显著提升数据存取速度。例如,选用的MT48LC4M3282芯片,具有128Mb的存储容量和32位数据带宽,内部结构包括4个Bank,每个Bank有4096行和256列,这样的配置适合处理大量的图像数据。

FIFO的速度主要取决于两个关键因素:一是SDRAM的工作频率,频率越高,数据传输速率就越快;二是SDRAM的突发长度,突发长度增加能提升数据流的吞吐量,从而提高传输速率。在实际设计中,需要根据具体应用的需求来调整这些参数,确保FIFO性能满足系统要求。

FPGA内部的FIFO模块、缓冲器和SDRAM控制器共同构成了FIFO系统。FIFO负责数据的临时存储和传输,缓冲器则可以平滑数据流,防止因读写速度不匹配导致的数据丢失,而SDRAM控制器则负责管理和控制与SDRAM之间的通信,确保数据正确、高效地在FPGA和SDRAM之间移动。

总结起来,基于FPGA的FIFO设计是一种经济高效的解决方案,能够解决在实时视频处理中的大数据量存储问题,通过灵活配置SDRAM参数和优化FPGA内部结构,可以实现高速、大容量的数据处理,从而满足复杂视频应用的实时性需求。

2021-07-13 上传

2010-11-03 上传

2012-06-04 上传

2023-06-08 上传

2023-05-20 上传

2023-08-02 上传

2024-10-30 上传

2023-08-18 上传

2023-06-12 上传

weixin_38742520

- 粉丝: 15

- 资源: 940

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析