没有合适的资源?快使用搜索试试~ 我知道了~

首页DELL G3-3579 笔记本主板LA-F611P技术图纸

DELL G3-3579 笔记本主板LA-F611P技术图纸

需积分: 32 2 下载量 69 浏览量

更新于2024-07-14

收藏 4.71MB PDF 举报

"DELL G3-3579 模型的主板电路图(LA-F611P)"

该文档是关于DELL G3系列笔记本电脑,具体型号为G3-3579的主板电路图(LA-F611P)。此文档由Compal Electronics公司制作,Compal是一家知名的原始设计制造商(ODM),为多个品牌生产电子产品,包括DELL。电路图的详细信息如下:

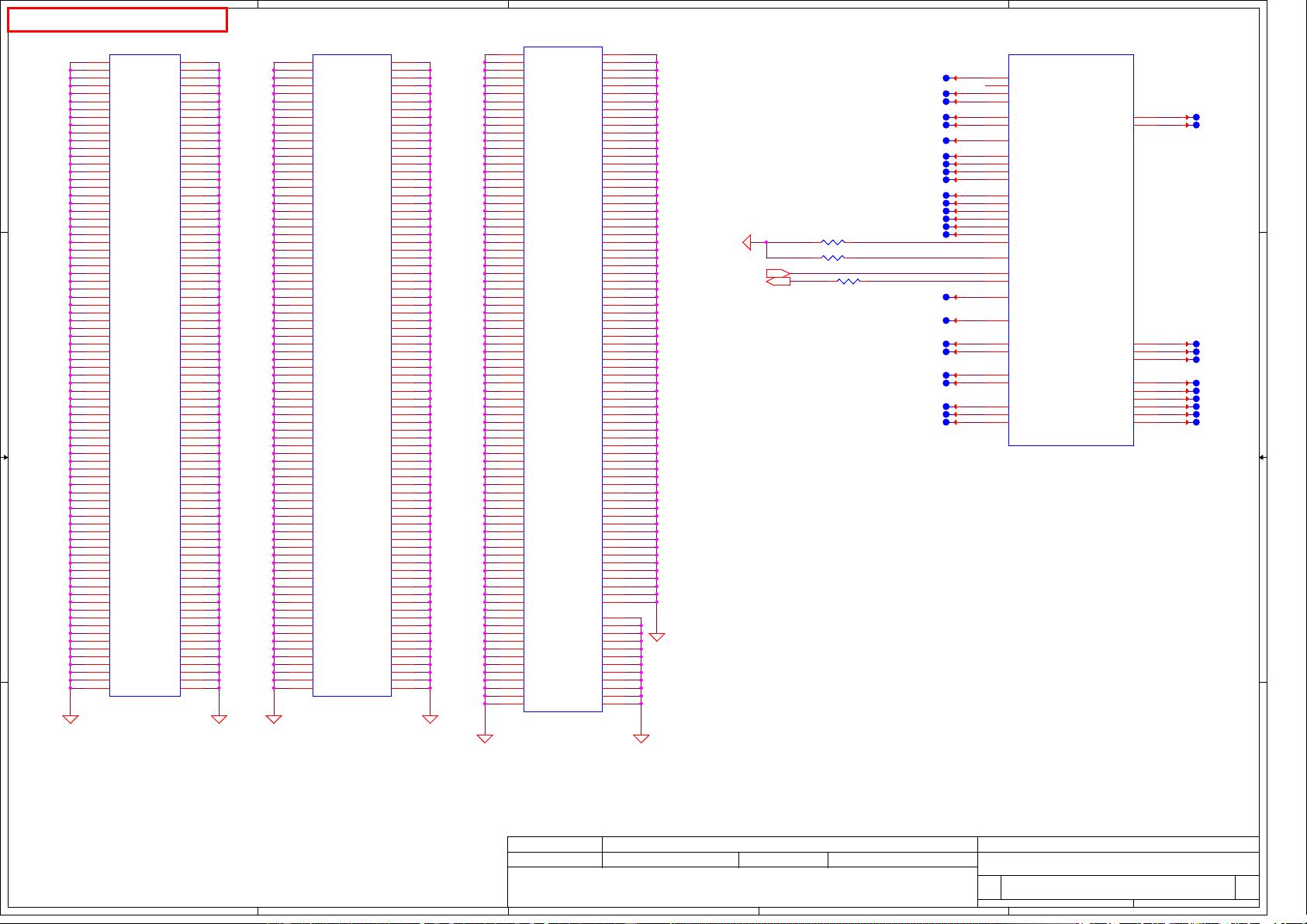

1. **主板板号与组件**:主板的板号为PWB:9HTP8,PCBR1,表明这是特定型号的主板印刷电路板。此外,还有其他组件如CPUR1,这可能是CPU(中央处理器)的连接部分。

2. **CPU信息**:文档提到了CPU的型号,N17P-G0/G1,这对应Intel的Coffee Lake-H系列处理器,可能是Core i7或i5等高性能移动处理器。

3. **电源管理/基本输入输出系统(BIOS)组件**:文档中提到的PWR/BPCBPN:DA4002L3010和IO/BPCBPN:DA6001XF010分别代表电源管理和BIOS相关的电路板部件编号,这些部件负责处理系统的供电和与外部设备的通信。

4. **修订历史**:文件标注了版本Rev:1.0(A00),表示这是设计的第1.0版,A00可能指的是这一版的特定迭代。日期为2018-03-22,说明这是在2018年3月22日完成或更新的设计。

5. **保密性与版权**:文档被标记为"CompalSecretData",表明它是Compal的机密资料,未经许可不得向第三方透露。同时,文档包含了2014年的版权信息,显示了其内容的原创性和法律保护。

6. **图纸信息**:LA-F611P是该电路图的名称,0.3可能是图纸的比例,1/78表示该图纸是整体设计中的第1张,总共有78张,暗示电路图的复杂性。

7. **适用范围**:Loki-G15/17模型名称可能指代DELL G3系列的15寸或17寸版本,表明此电路图适用于不同尺寸的产品。

这份文档对于维修、升级或故障排查DELL G3-3579笔记本电脑的主板部分至关重要,它提供了详细的硬件布局和连接信息,对技术专家来说是宝贵的参考资料。

For DELL review

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Main Func = CPU

PCH_TRIGOUT_R

CPU_TRIGOUT

PCH_TRIGOUT_R22

CPU_TRIGOUT_R22

Title

Size Document Number R ev

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

13 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

CFL-H(8/8)GND/RSVD

Title

Size Document Number R ev

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

13 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

CFL-H(8/8)GND/RSVD

Title

Size Document Number R ev

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

13 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

CFL-H(8/8)GND/RSVD

TC50TP@

TC58TP@

TC35TP@

TC54TP@

TC55 TP@

TC34TP@

TC36TP@

7OF13

CFL_H_SOC

UC1G

CFL-H_BGA1440

VSS

AW5

VSS

AY12

VSS

AY33

VSS

AY34

VSS

B9

VSS

BA10

VSS

BA11

VSS

BA12

VSS

BA37

VSS

BA38

VSS

BA6

VSS

BA7

VSS

BA8

VSS

BA9

VSS

BB1

VSS

BB12

VSS

BB2

VSS

BB29

VSS

BB3

VSS

BB30

VSS

BB4

VSS

BB5

VSS

BB6

VSS

BC12

VSS

BC13

VSS

BC14

VSS

BC33

VSS

BC34

VSS

BC6

VSS

BD10

VSS

BD11

VSS

BD12

VSS

BD37

VSS

BD6

VSS

BD7

VSS

BD8

VSS

BD9

VSS

BE1

VSS

BE2

VSS

BE29

VSS

BE3

VSS

BE30

VSS

BE4

VSS

BE5

VSS

BE6

VSS

BF12

VSS

BF33

VSS

BF34

VSS

BF6

VSS

BG12

VSS

BG13

VSS

BG14

VSS

BG37

VSS

BG38

VSS

BG6

VSS

BH1

VSS

BH10

VSS

BH11

VSS

BH12

VSS

BH14

VSS

BH2

VSS

BH3

VSS

BH4

VSS

BH5

VSS

BH6

VSS

BH7

VSS

BH8

VSS

BH9

VSS

T2

VSS

T3

VSS

T33

VSS

T34

VSS

T4

VSS

T5

VSS

T7

VSS

T8

VSS

T9

VSS

U37

VSS

U38

VSS

BJ12

VSS

BJ14

VSS

BJ15

VSS

BJ18

VSS

BJ22

VSS

BJ25

VSS

BJ29

VSS

BJ30

VSS

BJ31

VSS

BJ32

VSS

BJ33

VSS

BJ34

VSS

BJ35

VSS

BJ36

VSS

BK13

VSS

BK14

VSS

BK15

VSS

BK18

VSS

BK22

VSS

BK25

VSS

BK29

VSS

BK6

VSS

BL13

VSS

BL14

VSS

BL18

VSS

BL19

VSS

BL20

VSS

BL21

VSS

BL22

VSS

BL29

VSS

BL33

VSS

BL35

VSS

BL38

VSS

BL6

VSS

BM11

VSS

BM12

VSS

BM13

VSS

BM14

VSS

BM18

VSS

BM2

VSS

BM21

VSS

BM22

VSS

BM23

VSS

BM24

VSS

BM25

VSS

BM26

VSS

BM27

VSS

BM28

VSS

BM29

VSS

BM3

VSS

BM33

VSS

BM35

VSS

BM38

VSS

BM5

VSS

BM6

VSS

BM7

VSS

BM8

VSS

BM9

VSS

BN12

VSS

BN14

VSS

BN18

VSS

BN19

VSS

BN2

VSS

BN20

VSS

BN21

VSS

BN24

VSS

BN29

VSS

BN30

VSS

BN31

VSS

BN34

VSS

P38

VSS

P6

VSS

R12

VSS

R29

VSS

AY14

VSS

BD38

VSS

R30

VSS

T1

VSS

T10

VSS

T11

VSS

T12

VSS

T13

VSS

T14

TC46TP@

TC29TP@

TC52 TP@

TC31TP@

TC26TP@

TC30 TP@

TC57 TP@

TC43TP@

TC47 TP@

13OF13

CFL_H_SOC

UC1M

CFL-H_BGA1440

VSS_A37

A37

RSVD19

BR35

RSVD29

J3

RSVD18

BR31

RSVD9

BH30

RSVD28

J24

RSVD_TP5

E2

RSVD17

BR2

RSVD8

B38

RSVD27

H24

RSVD_TP4

E1

RSVD16

BP1

RSVD7

B30

RSVD26

G3

RSVD_TP3

D1

RSVD15

BN35

RSVD6

B2

RSVD25

G13

RSVD_TP2

BT2

RSVD14

BN33

RSVD5

AP29

RSVD24

F30

RSVD_TP1

BR1

RSVD13

BL34

RSVD4

AP14

RSVD23

E30

RSVD12

BL31

RSVD3

AJ8

RSVD22

C38

RSVD11

BK28

RSVD2

AE29

PROC_TRIGOUT

J23

RSVD21

C30

RSVD10

BJ28

RSVD1

AA14

RSVD31

R14

PROC_TRIGIN

H23

IST_TRIG

E3

RSVD20

C1

RSVD30

N29

VSS_A36

A36

RC6 0_0201_5%

1 2

TC38TP@

TC33TP@

TC41TP@

RC8 30_0402_5%

1 2

TC48 TP@

TC37TP@

TC28 TP@

TC49TP@

6OF13

CFL_H_SOC

UC1F

CFL-H_BGA1440

VSS

A10

VSS

A12

VSS

A16

VSS

A18

VSS

A20

VSS

A22

VSS

A24

VSS

A26

VSS

A28

VSS

A30

VSS

A6

VSS

A9

VSS

AA12

VSS

AA29

VSS

AA30

VSS

AB33

VSS

AB34

VSS

AB6

VSS

AC1

VSS

AC12

VSS

AC2

VSS

AC3

VSS

AC37

VSS

AC38

VSS

AC4

VSS

AC5

VSS

AC6

VSS

AD10

VSS

AD11

VSS

AD12

VSS

AD29

VSS

AD30

VSS

AD6

VSS

AD8

VSS

AD9

VSS

AE33

VSS

AE34

VSS

AE6

VSS

AF1

VSS

AF12

VSS

AF13

VSS

AF14

VSS

AF2

VSS

AF3

VSS

AF4

VSS

AG10

VSS

AG11

VSS

AG13

VSS

AG29

VSS

AG30

VSS

AG6

VSS

AG7

VSS

AG8

VSS

AH12

VSS

AH33

VSS

AH34

VSS

AH35

VSS

AH36

VSS

AH6

VSS

AJ1

VSS

AJ13

VSS

AJ2

VSS

AJ3

VSS

AJ37

VSS

AJ38

VSS

AJ4

VSS

AJ5

VSS

AJ6

VSS

W4

VSS

W5

VSS

Y10

VSS

Y11

VSS

Y13

VSS

Y14

VSS

Y37

VSS

Y38

VSS

Y7

VSS

Y8

VSS

Y9

VSS

AK29

VSS

AK30

VSS

AK4

VSS

AL10

VSS

AL12

VSS

AL14

VSS

AL33

VSS

AL34

VSS

AL4

VSS

AL7

VSS

AL8

VSS

AL9

VSS

AM1

VSS

AM12

VSS

AM2

VSS

AM3

VSS

AM37

VSS

AM38

VSS

AM4

VSS

AM5

VSS

AN12

VSS

AN29

VSS

AN30

VSS

AN5

VSS

AN6

VSS

AP10

VSS

AP11

VSS

AP12

VSS

AP33

VSS

AP34

VSS

AP8

VSS

AP9

VSS

AR1

VSS

AR13

VSS

AR14

VSS

AR2

VSS

AR29

VSS

AR3

VSS

AR30

VSS

AR31

VSS

AR32

VSS

AR33

VSS

AR34

VSS

AR35

VSS

AR36

VSS

AR37

VSS

AR38

VSS

AR4

VSS

AR5

VSS

AT29

VSS

AT30

VSS

AT6

VSS

AU10

VSS

AU11

VSS

AU12

VSS

AU33

VSS

AU34

VSS

AU6

VSS

AU7

VSS

AU8

VSS

AU9

VSS

AV37

VSS

AV38

VSS

AW1

VSS

AW12

VSS

AW2

VSS

AW29

VSS

AW3

VSS

AW30

VSS

AW4

VSS

U6

VSS

V12

VSS

V29

VSS

V30

VSS

A14

VSS

AD7

VSS

V6

VSS

W1

VSS

W12

VSS

W2

VSS

W3

VSS

W33

VSS

W34

TC40TP@

TC45 TP@

TC42TP@

TC59 TP@

TC32TP@

TC24TP@

TC53 TP@

TC51 TP@

TC44TP@

RC7 0_0201_5%

1 2

TC25TP@

8OF13

CFL_H_SOC

UC1H

CFL-H_BGA1440

VSS

BN4

VSS

BN7

VSS

BP12

VSS

BP14

VSS

BP18

VSS

BP21

VSS

BP24

VSS

BP25

VSS

BP26

VSS

BP29

VSS

BP33

VSS

BP34

VSS

BP7

VSS

BR12

VSS

BR14

VSS

BR18

VSS

BR21

VSS

BR24

VSS

BR25

VSS

BR26

VSS

BR29

VSS

BR34

VSS

BR36

VSS

BR7

VSS

BT12

VSS

BT14

VSS

BT18

VSS

BT21

VSS

BT24

VSS

BT26

VSS

BT29

VSS

BT32

VSS

BT5

VSS

C11

VSS

C13

VSS

C15

VSS

C17

VSS

C19

VSS

C21

VSS

C23

VSS

C25

VSS

C27

VSS

C29

VSS

C31

VSS

C37

VSS

C5

VSS

C8

VSS

C9

VSS

D10

VSS

D12

VSS

D14

VSS

D16

VSS

D18

VSS

D20

VSS

D22

VSS

D24

VSS

D26

VSS

D28

VSS

D3

VSS

D30

VSS

D33

VSS

D6

VSS

D9

VSS

E34

VSS

E35

VSS

E38

VSS

E4

VSS

E9

VSS

N3

VSS

N33

VSS

N34

VSS

N4

VSS

N5

VSS

N6

VSS

N7

VSS

N8

VSS

N9

VSS

P12

VSS

P37

VSS

M14

VSS

M6

VSS

N1

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F2

VSS

F21

VSS

F23

VSS

F25

VSS

F27

VSS

F29

VSS

F3

VSS

F31

VSS

F36

VSS

F4

VSS

F5

VSS

F8

VSS

F9

VSS

G10

VSS

G12

VSS

G14

VSS

G16

VSS

G18

VSS

G20

VSS

G22

VSS

G23

VSS

G24

VSS

G26

VSS

G28

VSS

G4

VSS

G5

VSS

G6

VSS

G8

VSS

G9

VSS

H11

VSS

H12

VSS

H18

VSS

H22

VSS

H25

VSS

H32

VSS

H35

VSS

J10

VSS

J18

VSS

J22

VSS

J25

VSS

J32

VSS

J33

VSS

J36

VSS

J4

VSS

J7

VSS

K1

VSS

K10

VSS

K11

VSS

K2

VSS

K3

VSS

K38

VSS

K4

VSS

K5

VSS

K7

VSS

K8

VSS

K9

VSS

L29

VSS

L30

VSS

L33

VSS

L34

VSS

M12

VSS

M13

VSS

N10

VSS

N11

VSS

N12

VSS

N2

VSS

BT8

VSS

BR9

VSS

BT35

VSS

BT36

VSS

BR38

VSS

B37

VSS

D38

VSS

C2

VSS

B3

VSS

A3

VSS

A4

VSS

A34

VSS

BT3

VSS

BT4

TC39TP@

TC27TP@

TC56TP@

For DELL review

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

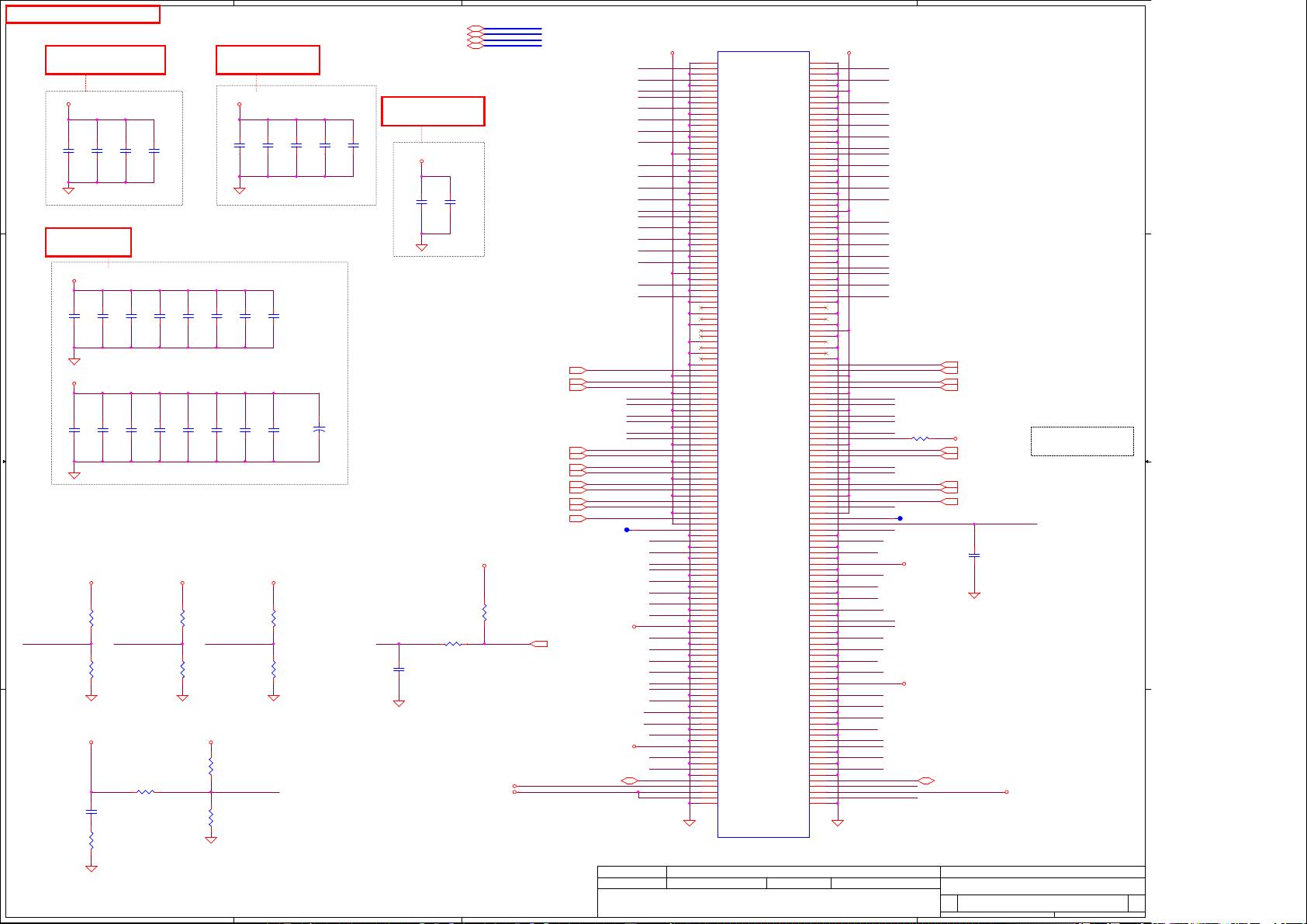

All VREF traces should

have 10 mil trace width

Layout Note:

Place near JDIMM1.257,259

Layout Note:

Place near JDIMM1.255

Layout Note:

Place near JDIMM1

Layout Note:

Place near JDIMM1.258

20mil

Main Func = DDR

+V_DDR_REFA

DDR_A_ODT0

DDR_A_ODT1

DDR_A_CS#0

PCH_SMBCLK

DDR_A_CS#1

DDR_A_MA14_WE#

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_MA1

DDR_A_MA3

DDR_A_MA8

DDR_A_MA9

DDR_A_MA12

DDR_A_BA1

DDR_A_MA6

DDR_A_CKE0

DDR_A_PAR

DDR_A_BG1

DDR_A_BG0

DDR_DRAMRST#DIMM_CHA_SA0 DIMM_CHA_SA1 DIMM_CHA_SA2

+V_DDR_REFA

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_D37

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_D43

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_D1

DDR_A_D5

DDR_A_D9

DDR_A_D8

DDR_A_D16

DDR_A_D17

DDR_A_D24

DDR_A_D29

DDR_A_D42

DDR_A_D48

DDR_A_D11

DDR_A_D10

DDR_A_D36

DDR_A_D34

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D55

DDR_A_D52

DDR_A_D56

DDR_A_D60

DDR_A_D3

DDR_A_D7

DDR_A_D18

DDR_A_D30

DDR_A_D61

DDR_A_D33

DDR_A_D19

DDR_A_DQS5

DDR_A_D62

DDR_A_D49

DDR_A_D38

DDR_A_D35

DDR_A_D15

DDR_A_D44

DDR_A_D45

DDR_A_D14

DDR_A_D27

DDR_A_DQS#3

DDR_A_D54

DDR_A_D51

DDR_A_DQS3

DDR_A_DQS#5

PCH_SMBDATA

DDR_A_CKE1

DDR_A_MA2

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_MA0

DDR_A_BA0

DDR_A_D32

DDR_DRAMRST#

DDR_A_MA5

DDR_A_MA15_CAS#

DDR_A_D46

DDR_A_D28

DDR_A_D21

DDR_A_MA10

DDR_A_ALERT#

DIMM_CHA_SA2

DDR_A_MA7

DDR_A_MA11

DDR_A_MA4

DDR_A_D13

DDR_A_D4

DDR_A_DQS#7

DDR_A_MA16_RAS#

DDR_A_MA13

DDR_A_DQS7

DDR_A_D63

DDR_A_D47

DDR_A_D25

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D6

DDR_A_D2

DIMM_CHA_SA0

DDR_A_D20

DDR_A_D0

DDR_A_D12

DIMM_CHA_SA1

DDR_A_D22

DDR_A_D23

DDR_A_D31 DDR_A_D26

DDR_A_D53

DDR_A_D50

DDR_A_D59

DDR_A_D58

DDR_A_D57

DDR_A_D[0..63]7

DDR_A_MA[0..13]7

DDR_A_DQS#[0..7]7

DDR_A_DQS[0..7]7

DDR_A_CKE07

DDR_A_BG17

DDR_A_BG07

DDR_A_CLK07

DDR_A_CLK#07

DDR_A_PAR7

DDR_A_BA17

DDR_A_CS#07

DDR_A_MA14_WE#7

DDR_A_ODT07

DDR_A_CS#17

H_DRAMRST# 18

DDR_A_ODT17

PCH_SMBCLK15,18,32

DDR_DRAMRST# 15

DDR_A_CKE1 7

DDR_A_ACT# 7

DDR_A_ALERT# 7

DDR_A_CLK1 7

DDR_A_CLK#1 7

DDR_A_BA0 7

DDR_A_MA16_RAS# 7

DDR_A_MA15_CAS# 7

PCH_SMBDATA 15,18,32

+0.6V_DDR_VTT+2.5V_MEM

+2.5V_MEM

+0.6V_DDR_VTT

+3VS

+1.2V_DDR

+V_DDR_REFA_R

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+3VS +3VS

+3VS

+3VS

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

14 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

DDR4 DIMMA_RVS

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

14 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

DDR4 DIMMA_RVS

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

14 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

DDR4 DIMMA_RVS

RD6

0_0402_5%

12

RD2

0_0402_5%

@

12

RD10

1K_0402_1%~D

12

CD30

0.022U_0402_25V7K

1

2

CD5

1U_0402_6.3V6K~D

1

2

LOTES_ADDR0206-P001A02~D

JDIMM1

DEREN_40-42271-26001RHF

CONN@

SP07001CY0L

VSS1

1

DQ5

3

VSS3

5

DQ1

7

VSS5

9

DQS0_c

11

DQS0_t

13

VSS8

15

DQ7

17

VSS10

19

DQ3

21

VSS12

23

DQ13

25

VSS14

27

DQ9

29

VSS16

31

DM1_n/DBI_n

33

VSS17

35

DQ15

37

VSS19

39

DQ10

41

VSS21

43

DQ21

45

VSS23

47

DQ17

49

VSS25

51

DQS2_c

53

DQS2_t

55

VSS28

57

DQ23

59

VSS30

61

DQ19

63

VSS32

65

DQ29

67

VSS34

69

DQ25

71

VSS36

73

DM3_n/DBI3_n

75

VSS37

77

DQ30

79

VSS39

81

DQ26

83

VSS41

85

CB5/NC

87

VSS43

89

CB1/NC

91

VSS45

93

DQS8_c

95

DQS8_t

97

VSS48

99

CB2/NC

101

VSS50

103

CB3/NC

105

VSS52

107

CKE0

109

VDD1

111

BG1

113

BG0

115

VDD3

117

A12

119

A9

121

VDD5

123

A8

125

A6

127

VDD7

129

A3

131

A1

133

VDD9

135

CK0_t

137

CK0_c

139

VDD11

141

PARITY

143

BA1

145

VDD13

147

CS0_n

149

WE_n/A14

151

VDD15

153

ODT0

155

CS1_n

157

VDD17

159

ODT1

161

VDD19

163

C1, CS3_n,NC

165

VSS53

167

DQ37

169

VSS55

171

DQ33

173

VSS57

175

DQS4_c

177

DQS4_t

179

VSS60

181

DQ38

183

VSS62

185

DQ34

187

VSS64

189

DQ44

191

VSS66

193

DQ40

195

VSS68

197

DM5_n/DBI5_n

199

VSS69

201

DQ46

203

VSS71

205

DQ42

207

VSS73

209

DQ52

211

VSS75

213

DQ49

215

VSS77

217

DQS6_c

219

DQS6_t

221

VSS80

223

DQ55

225

VSS82

227

DQ51

229

VSS84

231

DQ61

233

VSS86

235

DQ56

237

VSS88

239

DM7_n/DBI7_n

241

VSS89

243

DQ62

245

VSS91

247

DQ58

249

VSS93

251

SCL

253

VDDSPD

255

VPP1

257

VPP2

259

GND1

261

VSS2

2

DQ4

4

VSS4

6

DQ0

8

VSS6

10

DM0_n/DBI0_n

12

VSS7

14

DQ6

16

VSS9

18

DQ2

20

VSS11

22

DQ12

24

VSS13

26

DQ8

28

VSS15

30

DQS1_c

32

DQS1_t

34

VSS18

36

DQ14

38

VSS20

40

DQ11

42

VSS22

44

DQ20

46

VSS24

48

DQ16

50

VSS26

52

DM2_n/DBI2_n

54

VSS27

56

DQ22

58

VSS29

60

DQ18

62

VSS31

64

DQ28

66

VSS33

68

DQ24

70

VSS35

72

DQS3_c

74

DQS3_t

76

VSS38

78

DQ31

80

VSS40

82

DQ27

84

VSS42

86

CB4/NC

88

VSS44

90

CB0/NC

92

VSS46

94

DM8_n/DBI_n/NC

96

VSS47

98

CB6/NC

100

VSS49

102

CB7/NC

104

VSS51

106

RESET_n

108

CKE1

110

VDD2

112

ACT_n

114

ALERT_n

116

VDD4

118

A11

120

A7

122

VDD6

124

A5

126

A4

128

VDD8

130

A2

132

EVENT_n/NF

134

VDD10

136

CK1_t/NF

138

CK1_c/NF

140

VDD12

142

A0

144

A10/AP

146

VDD14

148

BA0

150

RAS_n/A16

152

VDD16

154

CAS_n/A15

156

A13

158

VDD18

160

C0/CS2_n/NC

162

VREFCA

164

SA2

166

VSS54

168

DQ36

170

VSS56

172

DQ32

174

VSS58

176

DM4_n/DBI4_n

178

VSS59

180

DQ39

182

VSS61

184

DQ35

186

VSS63

188

DQ45

190

VSS65

192

DQ41

194

VSS67

196

DQS5_c

198

DQS5_t

200

VSS70

202

DQ47

204

VSS72

206

DQ43

208

VSS74

210

DQ53

212

VSS76

214

DQ48

216

VSS78

218

DM6_n/DBI6_n

220

VSS79

222

DQ54

224

VSS81

226

DQ50

228

VSS83

230

DQ60

232

VSS85

234

DQ57

236

VSS87

238

DQS7_c

240

DQS7_t

242

VSS90

244

DQ63

246

VSS92

248

DQ59

250

VSS94

252

SDA

254

SA0

256

VTT

258

SA1

260

GND2

262

CD15

1U_0402_6.3V6K~D

1

2

CD20

10U_0603_6.3V6M~D

1

2

RD11

24.9_0402_1%

12

TP41

RD12

1K_0402_1%~D

12

RD8 0_0402_5%

12

CD6

10U_0603_6.3V6M~D

1

2

RD7

470_0402_1%

12

CD19

10U_0603_6.3V6M~D

1

2

CD7

10U_0603_6.3V6M~D

1

2

CD10

2.2U_0603_6.3V6K~D

1

2

RD23

240_0402_1%

12

CD17

1U_0402_6.3V6K~D

1

2

CD2

10U_0603_6.3V6M~D

1

2

CD1

10U_0603_6.3V6M~D

1

2

CD18

1U_0402_6.3V6K~D

1

2

CD28

0.1U_0402_16V7K~D

1

2

CD23

10U_0603_6.3V6M~D

1

2

CD29

0.1U_0402_16V7K~D

@

1

2

CD60

1U_0402_6.3V6K~D

1

2

RD3

0_0402_5%

@

12

CD61

1U_0402_6.3V6K~D

1

2

CD14

1U_0402_6.3V6K~D

1

2

CD25

10U_0603_6.3V6M~D

1

2

CD9

0.1U_0402_16V7K~D

1

2

+

CD27

330U_D2_2V_Y

MAIN@

1

2

CD24

10U_0603_6.3V6M~D

1

2

CD13

1U_0402_6.3V6K~D

1

2

CD16

1U_0402_6.3V6K~D

1

2

RD5

0_0402_5%

12

CD12

1U_0402_6.3V6K~D

1

2

RD4

0_0402_5%

12

TP40

CD3

1U_0402_6.3V6K~D

1

2

CD26

10U_0603_6.3V6M~D

1

2

RD1

0_0402_5%

@

12

CD22

10U_0603_6.3V6M~D

1

2

CD21

10U_0603_6.3V6M~D

1

2

CD11

1U_0402_6.3V6K~D

1

2

CD4

1U_0402_6.3V6K~D

1

2

RD9 2_0402_1%

1 2

For DELL review

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

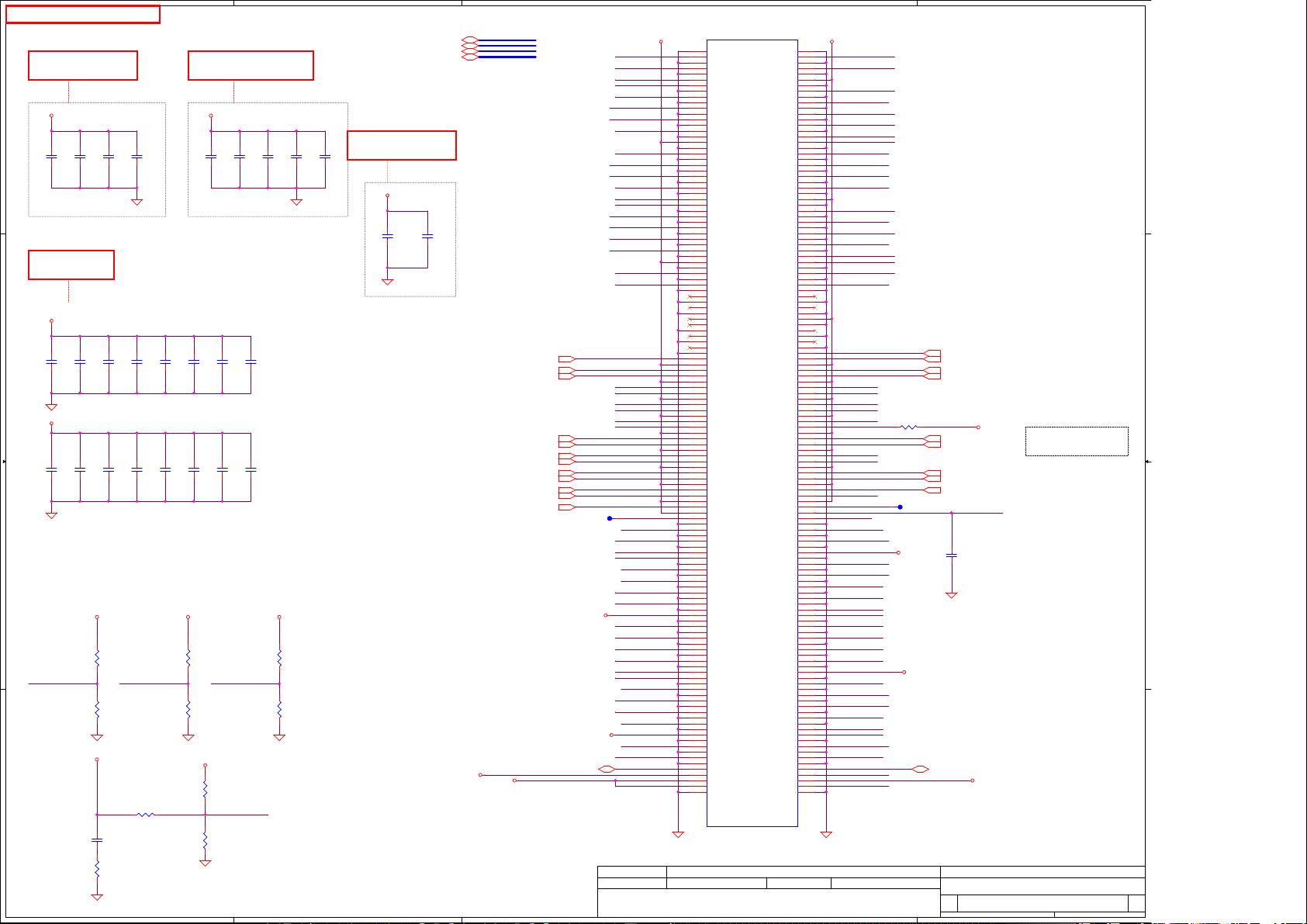

All VREF traces should

have 10 mil trace width

Layout Note:

Place near JDIMM2.257,259

Layout Note:

Place near JDIMM2.255

Layout Note:

Place near JDIMM2.258

Layout Note:

Place near JDIMM2

20mil

Main Func = DDR

DIMM_CHB_SA0 DIMM_CHB_SA1 DIMM_CHB_SA2

+V_DDR_REFB

DDR_B_DQS1

DDR_B_D47

DDR_B_DQS#2

DDR_B_DQS#1

DDR_B_D46

DDR_B_DQS2

DDR_B_BG1

DDR_B_CKE0

DDR_B_BG0

DDR_B_MA8

DDR_B_MA1

DDR_B_MA3

DDR_B_MA9

DDR_B_MA12

DDR_B_MA6

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_BA1

DDR_B_PAR

DDR_B_MA14_WE#

DDR_B_CS#0

DDR_B_ODT0

DDR_B_CS#1

DDR_B_ODT1

DDR_B_DQS#4

DDR_B_DQS6

DDR_B_DQS#6

PCH_SMBCLK

DDR_B_DQS3

DDR_B_DQS#3

DDR_DRAMRST#

DDR_B_CKE1

DDR_B_ALERT#

DDR_B_MA5

DDR_B_MA2

DDR_B_MA4

DDR_B_MA11

DDR_B_MA7

DDR_B_CLK1

DDR_B_CLK#1

DDR_B_MA10

DDR_B_MA0

DDR_B_MA16_RAS#

DDR_B_BA0

DDR_B_MA15_CAS#

DDR_B_MA13

+V_DDR_REFB

DIMM_CHB_SA2

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS7

DDR_B_DQS#7

PCH_SMBDATA

DIMM_CHB_SA0

DIMM_CHB_SA1

DDR_B_D40

DDR_B_D41

DDR_B_D43

DDR_B_D45

DDR_B_D44

DDR_B_D42

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS4

DDR_B_D15DDR_B_D11

DDR_B_D13 DDR_B_D12

DDR_B_D8

DDR_B_D14

DDR_B_D10

DDR_B_D9

DDR_B_D7

DDR_B_D2

DDR_B_D6

DDR_B_D3

DDR_B_D4

DDR_B_D1

DDR_B_D5

DDR_B_D0

DDR_B_D16DDR_B_D17

DDR_B_D18 DDR_B_D22

DDR_B_D23

DDR_B_D19

DDR_B_D21

DDR_B_D20

DDR_B_D25

DDR_B_D28

DDR_B_D27

DDR_B_D30

DDR_B_D31

DDR_B_D26

DDR_B_D29

DDR_B_D24

DDR_B_D34DDR_B_D35

DDR_B_D38 DDR_B_D39

DDR_B_D36

DDR_B_D37

DDR_B_D33

DDR_B_D32

DDR_B_D48DDR_B_D52

DDR_B_D51 DDR_B_D54

DDR_B_D55

DDR_B_D53

DDR_B_D50

DDR_B_D49

DDR_B_D57

DDR_B_D61

DDR_B_D62

DDR_B_D59

DDR_B_D58DDR_B_D63

DDR_B_D60 DDR_B_D56

DDR_B_D[0..63]8

DDR_B_MA[0..13]8

DDR_B_DQS#[0..7]8

DDR_B_DQS[0..7]8

DDR_B_CKE08

DDR_B_BG18

DDR_B_BG08

DDR_B_CLK08

DDR_B_CLK#08

DDR_B_PAR8

DDR_B_BA18

DDR_B_CS#08

DDR_B_MA14_WE#8

DDR_B_ODT08

DDR_B_CS#18

DDR_B_ODT18

PCH_SMBCLK14,18,32

DDR_DRAMRST# 14

DDR_B_CKE1 8

DDR_B_ACT# 8

DDR_B_ALERT# 8

DDR_B_MA15_CAS# 8

DDR_B_CLK1 8

DDR_B_CLK#1 8

DDR_B_BA0 8

DDR_B_MA16_RAS# 8

PCH_SMBDATA 14,18,32

+2.5V_MEM

+0.6V_DDR_VTT

+V_DDR_REFB_R

+2.5V_MEM +0.6V_DDR_VTT

+1.2V_DDR

+1.2V_DDR

+3VS

+1.2V_DDR

+3VS+3VS+3VS

+1.2V_DDR +1.2V_DDR

+3VS

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

+1.2V_DDR

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

15 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

DDR4 DIMMB_STD

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

15 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

DDR4 DIMMB_STD

Title

Size Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

15 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

DDR4 DIMMB_STD

RD24

240_0402_1%

12

CD33

10U_0603_6.3V6M~D

1

2

CD39

0.1U_0402_16V7K~D

1

2

CD44

1U_0402_6.3V6K~D

1

2

LOTES_ADDR0205-P001A02~D

JDIMM2

DEREN_40-42261-26001RHF

CONN@

SP07001HW0L

VSS1

1

DQ5

3

VSS3

5

DQ1

7

VSS5

9

DQS0_c

11

DQS0_t

13

VSS8

15

DQ7

17

VSS10

19

DQ3

21

VSS12

23

DQ13

25

VSS14

27

DQ9

29

VSS16

31

DM1_n/DBI_n

33

VSS17

35

DQ15

37

VSS19

39

DQ10

41

VSS21

43

DQ21

45

VSS23

47

DQ17

49

VSS25

51

DQS2_c

53

DQS2_t

55

VSS28

57

DQ23

59

VSS30

61

DQ19

63

VSS32

65

DQ29

67

VSS34

69

DQ25

71

VSS36

73

DM3_n/DBI3_n

75

VSS37

77

DQ30

79

VSS39

81

DQ26

83

VSS41

85

CB5/NC

87

VSS43

89

CB1/NC

91

VSS45

93

DQS8_c

95

DQS8_t

97

VSS48

99

CB2/NC

101

VSS50

103

CB3/NC

105

VSS52

107

CKE0

109

VDD1

111

BG1

113

BG0

115

VDD3

117

A12

119

A9

121

VDD5

123

A8

125

A6

127

VDD7

129

A3

131

A1

133

VDD9

135

CK0_t

137

CK0_c

139

VDD11

141

PARITY

143

BA1

145

VDD13

147

CS0_n

149

WE_n/A14

151

VDD15

153

ODT0

155

CS1_n

157

VDD17

159

ODT1

161

VDD19

163

C1, CS3_n,NC

165

VSS53

167

DQ37

169

VSS55

171

DQ33

173

VSS57

175

DQS4_c

177

DQS4_t

179

VSS60

181

DQ38

183

VSS62

185

DQ34

187

VSS64

189

DQ44

191

VSS66

193

DQ40

195

VSS68

197

DM5_n/DBI5_n

199

VSS69

201

DQ46

203

VSS71

205

DQ42

207

VSS73

209

DQ52

211

VSS75

213

DQ49

215

VSS77

217

DQS6_c

219

DQS6_t

221

VSS80

223

DQ55

225

VSS82

227

DQ51

229

VSS84

231

DQ61

233

VSS86

235

DQ56

237

VSS88

239

DM7_n/DBI7_n

241

VSS89

243

DQ62

245

VSS91

247

DQ58

249

VSS93

251

SCL

253

VDDSPD

255

VPP1

257

VPP2

259

GND1

261

VSS2

2

DQ4

4

VSS4

6

DQ0

8

VSS6

10

DM0_n/DBI0_n

12

VSS7

14

DQ6

16

VSS9

18

DQ2

20

VSS11

22

DQ12

24

VSS13

26

DQ8

28

VSS15

30

DQS1_c

32

DQS1_t

34

VSS18

36

DQ14

38

VSS20

40

DQ11

42

VSS22

44

DQ20

46

VSS24

48

DQ16

50

VSS26

52

DM2_n/DBI2_n

54

VSS27

56

DQ22

58

VSS29

60

DQ18

62

VSS31

64

DQ28

66

VSS33

68

DQ24

70

VSS35

72

DQS3_c

74

DQS3_t

76

VSS38

78

DQ31

80

VSS40

82

DQ27

84

VSS42

86

CB4/NC

88

VSS44

90

CB0/NC

92

VSS46

94

DM8_n/DBI_n/NC

96

VSS47

98

CB6/NC

100

VSS49

102

CB7/NC

104

VSS51

106

RESET_n

108

CKE1

110

VDD2

112

ACT_n

114

ALERT_n

116

VDD4

118

A11

120

A7

122

VDD6

124

A5

126

A4

128

VDD8

130

A2

132

EVENT_n/NF

134

VDD10

136

CK1_t/NF

138

CK1_c/NF

140

VDD12

142

A0

144

A10/AP

146

VDD14

148

BA0

150

RAS_n/A16

152

VDD16

154

CAS_n/A15

156

A13

158

VDD18

160

C0/CS2_n/NC

162

VREFCA

164

SA2

166

VSS54

168

DQ36

170

VSS56

172

DQ32

174

VSS58

176

DM4_n/DBI4_n

178

VSS59

180

DQ39

182

VSS61

184

DQ35

186

VSS63

188

DQ45

190

VSS65

192

DQ41

194

VSS67

196

DQS5_c

198

DQS5_t

200

VSS70

202

DQ47

204

VSS72

206

DQ43

208

VSS74

210

DQ53

212

VSS76

214

DQ48

216

VSS78

218

DM6_n/DBI6_n

220

VSS79

222

DQ54

224

VSS81

226

DQ50

228

VSS83

230

DQ60

232

VSS85

234

DQ57

236

VSS87

238

DQS7_c

240

DQS7_t

242

VSS90

244

DQ63

246

VSS92

248

DQ59

250

VSS94

252

SDA

254

SA0

256

VTT

258

SA1

260

GND2

262

CD49

10U_0603_6.3V6M~D

1

2

CD35

1U_0402_6.3V6K~D

1

2

CD58

0.1U_0402_16V7K~D

1

2

RD19 2_0402_1%

1 2

CD51

10U_0603_6.3V6M~D

1

2

RD16

0_0402_5%

12

RD20

1K_0402_1%~D

12

CD41

1U_0402_6.3V6K~D

1

2

RD17

0_0402_5%

@

12

CD42

1U_0402_6.3V6K~D

1

2

CD34

10U_0603_6.3V6M~D

1

2

CD53

10U_0603_6.3V6M~D

1

2

RD22

24.9_0402_1%

12

CD56

10U_0603_6.3V6M~D

1

2

RD21

1K_0402_1%~D

12

CD63

1U_0402_6.3V6K~D

1

2

RD15

0_0402_5%

@

12

CD46

1U_0402_6.3V6K~D

1

2

CD37

10U_0603_6.3V6M~D

1

2

CD36

1U_0402_6.3V6K~D

1

2

RD13

0_0402_5%

@

12

RD18

0_0402_5%

12

CD50

10U_0603_6.3V6M~D

1

2

CD45

1U_0402_6.3V6K~D

1

2

CD48

1U_0402_6.3V6K~D

1

2

CD54

10U_0603_6.3V6M~D

1

2

TP42

CD47

1U_0402_6.3V6K~D

1

2

CD62

1U_0402_6.3V6K~D

1

2

RD14

0_0402_5%

12

CD43

1U_0402_6.3V6K~D

1

2

CD32

10U_0603_6.3V6M~D

1

2

CD55

10U_0603_6.3V6M~D

1

2

CD59

0.022U_0402_25V7K

1

2

CD40

2.2U_0603_6.3V6K~D

1

2

CD31

1U_0402_6.3V6K~D

1

2

CD52

10U_0603_6.3V6M~D

1

2

TP43

For DELL review

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

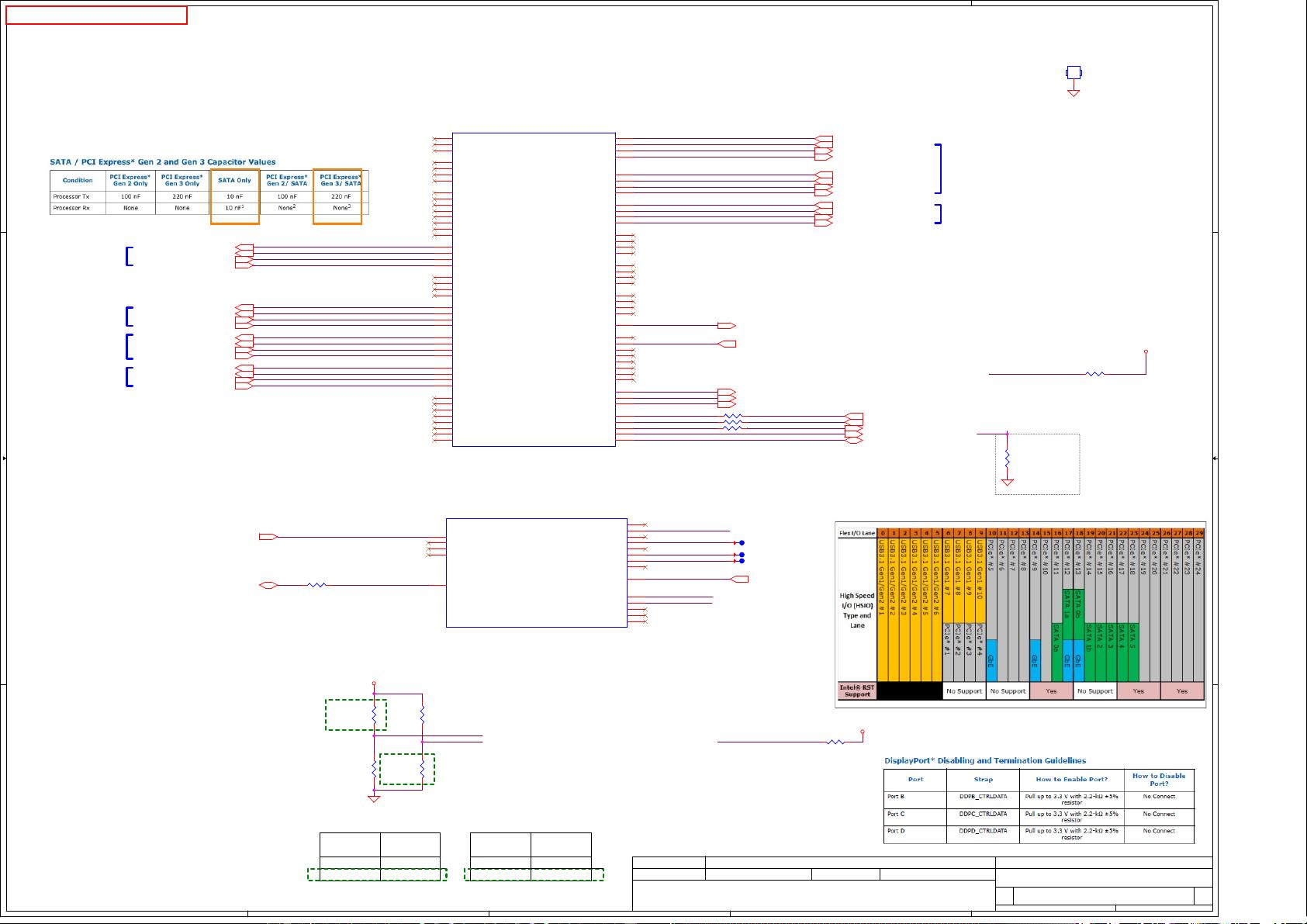

eDP_HPD pull down 100K

PCIE SSD

M.2 SSD/ NVMe/ Optane

PCIe / SATA

PCIE SSD

M.2 SSD/ NVMe/ Optane

PCIe

#571391_CFL_H_PDG_Rev0p5

12.2.10 PM_DOWN Topology

DDP[B..F]CTRLDATA

This signal has a weak internal Pull-down.

0 = Port B is not detected. (Default)

1 = Port B is detected.

Notes:

1. The internal Pull-down is disabled after

PCH_PWROK de-asserts.

2. This signal is in the primary well.

Non-TBT

TBT

PROJECT ID

(GPP_K22)

0

1

PROJECT ID1

TPM ID

SW TPM

HW TPM

(GPP_K23)

0

1

PROJECT ID2

SATA HDD --->

LAN

WLAN

PCIE SSD

M.2 SSD/ NVMe/ Optane

PCIe

Main Func = PCH

PCH Strap PIN

PCH_SATA_LED#

PCH_SATA_LED#

EDP_HPD_R

H_PM_DOWN

H_PLTRST_CPU#

PECI_PCH

H_THERMTRIP#H_THERMTRIP#_R

BKLT_IN_EC

L_BKLT_CTRL

H_PM_DOWN

PROJECT_ID2

PROJECT_ID1

PROJECT_ID1

PROJECT_ID2

H_PM_SYNC_PCH H_PM_SYNC_R

EDP_VDD_EN

PCIE_PRX_DTX_P11

PCIE_PRX_DTX_N11

PCIE_PTX_DRX_P11

PCIE_PTX_DRX_N11

SATA3_PRX_DTX_N0

SATA3_PRX_DTX_P0

SATA3_PTX_DRX_N0

SATA3_PTX_DRX_P0

PCIE_PRX_DTX_P12

PCIE_PRX_DTX_N12

PCIE_PTX_DRX_P12

PCIE_PTX_DRX_N12

PCIE_PRX_DTX_N14

PCIE_PTX_DRX_N14

PCIE_PRX_DTX_P14

PCIE_PTX_DRX_P14

PCIE_PRX_DTX_N9

PCIE_PTX_DRX_N9

PCIE_PRX_DTX_P9

PCIE_PTX_DRX_P9

PCIE_PRX_DTX_P15

PCIE_PTX_DRX_N15

PCIE_PRX_DTX_N15

PCIE_PTX_DRX_P15

PCIE_PRX_DTX_N10

PCIE_PTX_DRX_N10

PCIE_PRX_DTX_P10

PCIE_PTX_DRX_P10

CPU_DP1_CTRL_DATA

PROC_DETECT#

CPU_DP1_CTRL_DATA

CPU_DP1_HPD

M2_SSD_DETECT

PECI_EC 10,26

H_THERMTRIP# 10

H_PM_SYNC_R 10

H_PLTRST_CPU# 10

PCH_SATA_LED# 30,34

H_PM_DOWN 10

EDP_VDD_EN 29

EDP_HPD29

BKLT_IN_EC 26

L_BKLT_CTRL 29

PCIE_PRX_DTX_N1134

PCIE_PTX_DRX_N1134

PCIE_PRX_DTX_P1134

PCIE_PTX_DRX_P1134

SATA3_PRX_DTX_N032

SATA3_PTX_DRX_N032

SATA3_PTX_DRX_P032

SATA3_PRX_DTX_P032

PCIE_PRX_DTX_N1234

PCIE_PTX_DRX_N1234

PCIE_PRX_DTX_P1234

PCIE_PTX_DRX_P1234

PCIE_PRX_DTX_N1435

PCIE_PTX_DRX_P1435

PCIE_PTX_DRX_N1435

PCIE_PRX_DTX_P1435

PCIE_PTX_DRX_P9 34

PCIE_PTX_DRX_N9 34

PCIE_PRX_DTX_P9 34

PCIE_PRX_DTX_N9 34

PCIE_PRX_DTX_N15 33

PCIE_PRX_DTX_P15 33

PCIE_PTX_DRX_N15 33

PCIE_PTX_DRX_P15 33

PCIE_PTX_DRX_P10 34

PCIE_PTX_DRX_N10 34

PCIE_PRX_DTX_P10 34

PCIE_PRX_DTX_N10 34

CPU_DP1_HPD41

+3VS

+3VS

+3VS

PROC_DETECT# 10

M2_SSD_DETECT 34

Title

Size

Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

16 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

PCH (1/7) SATA,DDC,PCIE

Title

Size

Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

16 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

PCH (1/7) SATA,DDC,PCIE

Title

Size

Document Number R e v

Date: Sheet o f

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-F611P

0.3

16 78Thursday, March 22, 2018

2016/01/06 2017/01/06

Compal Electronics, Inc.

PCH (1/7) SATA,DDC,PCIE

RH14

13_0402_5%

@

1 2

RH557

10K_0201_5%

TBT@

12

T4942 TP@

RH73 13_0402_5%

1 2

RH33

2.2K_0402_5%

1 2

T4941 TP@

RH79 620_0402_5%

1 2

RH562

10K_0201_5%

NON_TPM@

12

T4943 TP@

RH681

10K_0201_5%

NON_TBT@

12

CLIP1

CLIP_15X3_VIUS1

EC0XQ000G00

RH656

0_0201_5%

1 2

3 OF 13

CNP-H

UH1C

CNP-H_BGA874

PCIE_15_SATA_2_TXN

B40

PECI

AF2

PM_SYNC

AF3

PM_DOWN

AE2

GPP_K3

U47

PCIE12_RXN/SATA1A_RXN

H42

PCIE20_TXP/SATA7_TXP

B44

PCIE16_TXN/SATA3_TXN

B41

GPP_K4

N48

PCIE13_RXP/SATA0B_RXP

C46

PCIE17_TXP/SATA4_TXP

B42

PCIE11_TXN/SATA0A_TXN

B36

GPP_F19/EDP_VDDEN

AV44

CL_RST#

AU4

GPP_K5

N47

PCIE19_TXP/SATA6_TXP

D43

PCIE18_TXN/SATA5_TXN

C42

GPP_E2/SATAXPCIE2/SATAGP2

AK47

GPP_E0/SATAXPCIE0/SATAGP0

AH41

GPP_K6

P47

PCIE15_RXP/SATA2_RXP

E45

PCIE14_RXP/SATA1B_RXP

C47

GPP_K7

R46

PCIE20_RXP/SATA7_RXP

R37

PCIE16_RXN/SATA3_RXN

L41

PCIE17_RXP/SATA4_RXP

K44

PCIE12_TXN/SATA1A_TXN

D38

PCIE13_TXP/SATA0B_TXP

C38

GPP_F12/SATA_SDATAOUT1

AU46

THRMTRIP#

AD3

GPP_K8

P48

GPP_F10/SATA_SCLOCK

AR42

GPP_K9

V47

PCIE18_RXN/SATA5_RXN

P41

PCIE19_RXP/SATA6_RXP

N42

PCIE10_RXN

K37

PCIE13_RXN/SATA0B_RXN

C45

GPP_F21/EDP_BKLTCTL

AU48

PCIE14_TXP/SATA1B_TXP

D39

GPP_F13/SATA_SDATAOUT0

AU47

GPP_F2/SATAXPCIE5/SATAGP5

AM43

PLTRST_CPU#

AG5

PCIE10_RXP

J37

PCIE16_TXP/SATA3_TXP

C41

PCIE10_TXN

C35

GPP_F4/SATAXPCIE7/SATAGP7

AM48

PCIE11_RXP/SATA0A_RXP

F39

PCIE14_RXN/SATA1B_RXN

D46

PCIE13_TXN/SATA0B_TXN

B38

GPP_F11/SATA_SLOAD

AR48

PCIE20_TXN/SATA7_TXN

A44

PCIE18_TXP/SATA5_TXP

D42

PCIE10_TXP

B35

GPP_F20/EDP_BKLTEN

AV46

CL_DATA

AT5

GPP_E8/SATA_LED#

AK48

GPP_E1/SATAXPCIE1/SATAGP1

AJ43

PCIE17_TXN/SATA4_TXN

A42

GPP_K10

V48

PCIE9_RXN

G36

PCIE19_TXN/SATA6_TXN

C44

GPP_K11

W47

PCIE16_RXP/SATA3_RXP

M40

PCIE15_RXN/SATA2_RXN

F44

PCIE14_TXN/SATA1B_TXN

C39

PCIE11_TXP/SATA0A_TXP

C36

PCIE20_RXN/SATA7_RXN

R35

PCIE17_RXN/SATA4_RXN

K43

PCIE12_RXP/SATA_1A_RXP

J41

PCIE9_RXP

F36

PCIE9_TXN

C34

PCIE18_RXP/SATA5_RXP

R40

GPP_K0

L47

PCIE11_RXN/SATA0A_RXN

G38

CL_CLK

AR2

GPP_F0/SATAXPCIE3/SATAGP_3

AN47

PCIE19_RXN/SATA6_RXN

M44

GPP_K1

L46

PCIE12_TXP/SATA1A_TXP

E37

PCIE9_TXP

D34

GPP_K2

U48

PCIE15_TXP/SATA2_TXP

C40

GPP_F3/SATAXPCIE6/SATAGP6

AM47

GPP_F1/SATAXPCIE4/SATAGP4

AM46

RH512 10K_0201_5%

1 2

5 OF 13

CNP-H

UH1E

CNP-H_BGA874

GPP_K22/IMGCLKOUT0

L48

GPP_F14/EXT_PWR_GATE#/PS_ON#

AP41

GPP_F22/DDPF_CTRLCLK

AT49

GPP_I1/DDPC_HPD1/DISP_MISC1

AN10

GPP_I10/DDPD_CTRLDATA

AR3

GPP_K23/IMGCLKOUT1

M45

GPP_I6/DDPB_CTRLDATA

AR8

GPP_I2/DPPD_HPD2/DISP_MISC2

AP9

GPP_I9/DDPD_CTRLCLK

AL9

GPP_I0/DDPB_HPD0/DISP_MISC0

AT6

GPP_I4/EDP_HPD/DISP_MISC4

AN6

GPP_F23/DDPF_CTRLDATA

AN40

GPP_I7/DDPC_CTRLCLK

AN13

GPP_K20

T46

GPP_I8/DDPC_CTRLDATA

AL10

GPP_K21

T45

GPP_I5/DDPB_CTRLCLK

AL13

GPP_H23/TIME_SYNC0

AJ47

GPP_I3/DPPE_HPD3/DISP_MISC3

AL15

RH13 30_0402_5%

1 2

RH561

10K_0201_5%

TPM@

12

剩余77页未读,继续阅读

点击了解资源详情

点击了解资源详情

244 浏览量

142 浏览量

2022-01-30 上传

2023-08-04 上传

106 浏览量

106 浏览量

2022-12-19 上传

qq_14854613

- 粉丝: 1

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功