FPGA实现SPI自动发送模块设计

104 浏览量

更新于2024-08-28

1

收藏 284KB PDF 举报

WR='0'结束本次传输

四、SPI接口详解:

SPI(Serial Peripheral Interface)是一种同步串行通信协议,常用于微控制器与外部设备间的数据交换。它由四个主要信号线组成:MOSI(Master Out, Slave In)、MISO(Master In, Slave Out)、SCK(Serial Clock)和SS(Slave Select)。在SPI通信中,主设备(通常为FPGA或MCU)控制时钟信号SCK,并通过MOSI向从设备发送数据,同时通过MISO接收从设备返回的数据。SS信号用于选择一个或多个从设备进行通信。

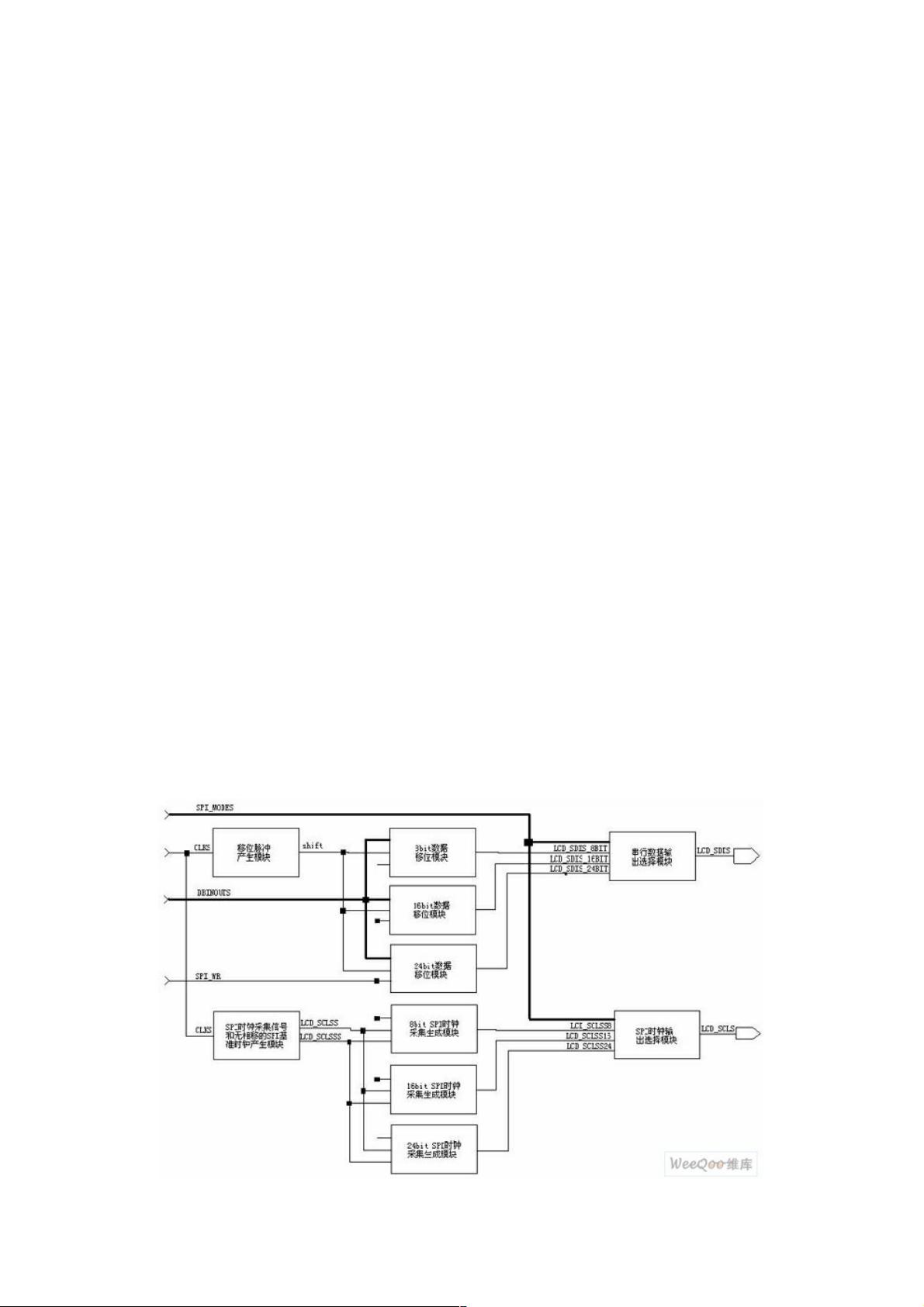

五、FPGA设计SPI发送模块的关键组件:

1. 串行数据输出选择模块:根据SPI_MODES的输入,确定数据的位宽,从而选择不同宽度的数据进行串行化。

2. 移位脉冲产生模块:生成移位脉冲,控制数据按照SPI协议的时序进行逐位移出。

3. SPI时钟采集信号:这个模块生成与SPI时钟同步的信号,确保数据传输的精确性。

4. 无相移的SPI基准时钟产生模块:提供稳定的SPI时钟源,确保时序的准确性,且不受系统时钟相位影响。

5. SPI时钟输出选择模块:根据SPI通信模式选择合适的时钟频率,支持不同速率的SPI设备。

6. SPI时钟采集生成模块:包括8bit、16bit和24bit三种,根据SPI_MODES选择对应的时钟采集单元,生成对应长度的时钟周期。

7. 数据移位模块:包括8bit、16bit和24bit三种,分别对应不同的数据传输模式,将并行数据转换为串行数据流。

六、设计实现:

使用VHDL语言进行硬件描述,定义各模块的接口和内部逻辑。在设计中,首先需要处理SPI_MODES信号,根据其值配置相应的数据移位模块和时钟采集模块。接着,当SPI_WR信号激活时,数据从DBINOUTS输入并开始移位,直至所有数据移位完成。最后,通过MOSI线将串行数据发送出去,并在每次传输结束后释放SS信号。

七、优势与应用场景:

使用FPGA设计SPI发送模块的优势在于灵活性高,可以自定义时序,适应各种SPI设备的需求。此外,由于硬件实现,相比于软件模拟,其速度更快,延迟更低。此技术适用于需要高速、高效率SPI通信的场合,如传感器接口、显示驱动、存储器扩展等。

八、测试与验证:

设计完成后,需要通过仿真工具进行功能验证,确保在不同模式下都能正确地发送数据。实际应用前,还需要在目标FPGA上进行硬件验证,确保在实际系统中的性能满足要求。

总结,FPGA设计的SPI自动发送模块技术结合了VHDL编程和可编程逻辑的优势,为SPI接口提供了灵活、高效的数据传输方案。通过模块化设计,可以适应不同数据宽度和传输速率的需求,广泛应用于需要定制SPI通信的嵌入式系统中。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-08-28 上传

2020-11-07 上传

点击了解资源详情

2020-10-20 上传

210 浏览量

2021-07-13 上传

weixin_38640168

- 粉丝: 6

- 资源: 958

最新资源

- Cree的管子模型CGH系列全套

- 测试ASP.NET应用程序

- Login,查看java源码,java数组

- TellkiAgent_OSXMemory

- Android *应用程序的性能评估

- love:爱心树表白网页原始码,jquery女神表白动画树特效

- 模块5解决方案

- kaguya-reread

- TESTSYM,java项目源码分享网,java运动

- algoritmos-caso3

- 法新社2

- ByWebView:WebView全方面使用,JS交互,进度条,上传图片,错误页面,视频全屏播放,唤起原生App,获取网页源代码,被作为第三方浏览器打开,DeepLink,[腾讯x5使用示例]

- Hibernate,java项目实例源码,javaweb大作业

- Soundloud - Soundcloud To Mp3-crx插件

- 大型高温浓硫酸液下泵的设计与使用.rar

- interesting-js:一些有趣的js