VHDL实现的HDB3编解码器设计与原理详解

需积分: 17 175 浏览量

更新于2024-08-02

3

收藏 7.28MB DOC 举报

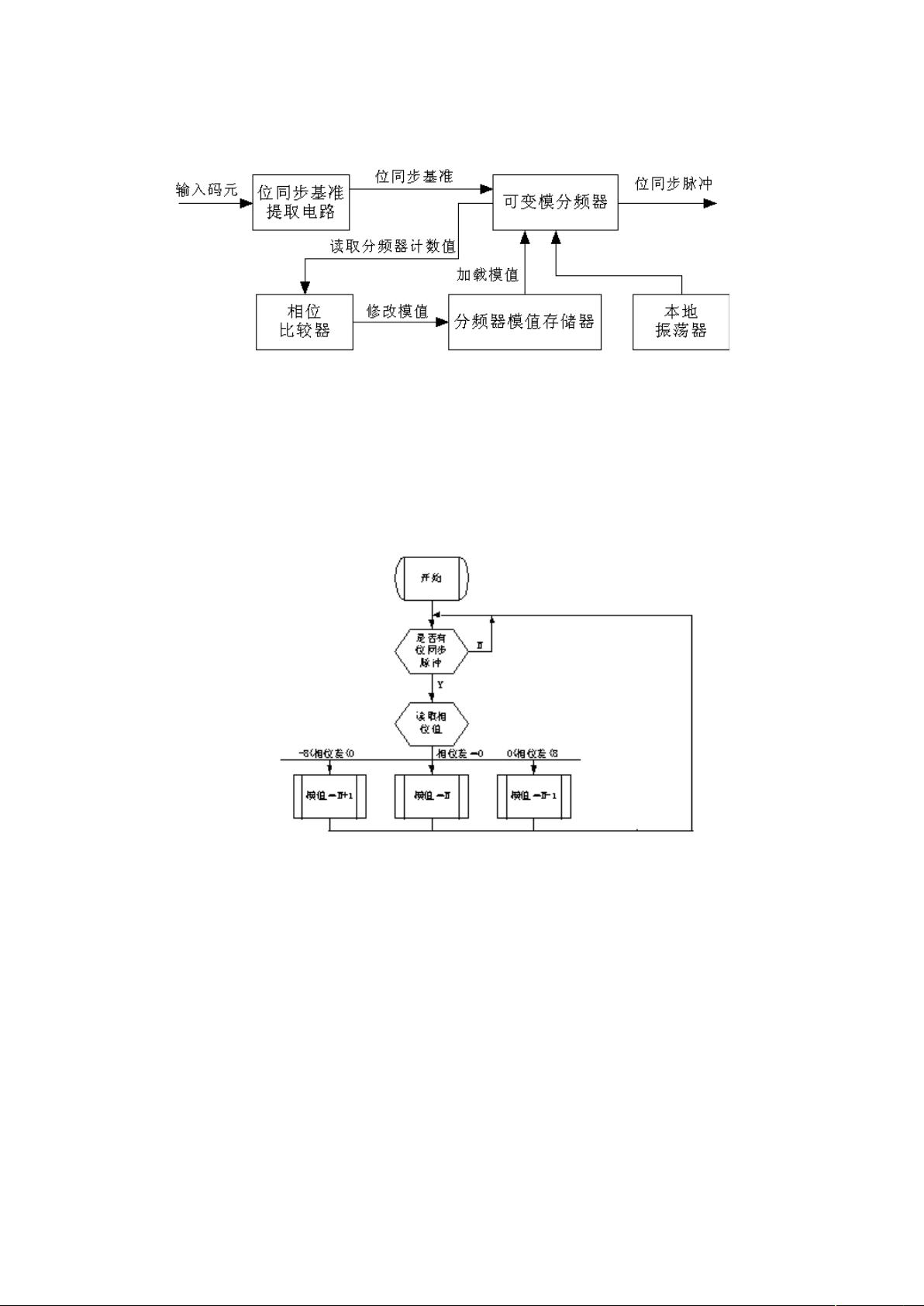

全数字HDB3编解码系统是一个专门用于处理数字信号传输的高效编码和解码技术,其核心原理是解决在通信过程中连续“0”码带来的同步问题。HDB3编码,全称为High Density Bipolar三阶高密度双极性码,是AMI码的一种改良,特别针对连“0”码过多导致的同步难题进行了优化。

实验目标涉及几个关键技能的实践:首先,学习和掌握HDB3编码的理论知识,包括编码规则和其在信号处理中的优势,如去除直流分量,提高检错能力,以及节省频带资源。编码规则分为三个部分:对于少于4个连“0”的情况,保持与AMI码一致;对于4个或更多连“0”,将它们分为四个“0”并插入一个V脉冲;当破坏点间“1”码数量为偶数时,插入B脉冲以确保奇数个“1”码,这有助于保持编码的正确性和同步。

其次,实验要求学生使用MAX+pluⅡ开发软件,这是一种流行的硬件描述语言(VHDL)环境,通过它来设计和实现HDB3编解码器。学生需要熟练运用M序列发生器生成信号源,并在实验箱上实际操作,观察编码和解码波形的差异,验证编码效果。

实验设备包括基础的电子测试工具,如MAX+plusⅡ开发系统、微机、示波器、稳压电源和万用表,以及实验箱,这些都是进行HDB3编解码系统设计和测试所必需的。

整个过程不仅涉及到硬件的设计和编程,还有模拟和实际测试,以便理解信号在编码和解码过程中的行为变化,以及错误检测和纠正的能力。通过这个项目,学生可以提升对数字信号处理的理解,锻炼使用VHDL编程的能力,以及对硬件电路的实际操作技巧。

总结来说,全数字HDB3编解码系统课程旨在提供一个全面的实践平台,让学生深入理解HDB3编码原理,掌握相关的软件工具和技术,并通过实际操作巩固理论知识,为未来的数字信号处理和通信系统设计打下坚实的基础。

535 浏览量

132 浏览量

208 浏览量

179 浏览量

2024-12-13 上传

286 浏览量

2022-09-24 上传

134 浏览量

153 浏览量

eelin_2008

- 粉丝: 1

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程