ModelsimSE10.0.c入门教程:Quartus11.0仿真配合使用

需积分: 34 41 浏览量

更新于2024-09-09

收藏 413KB PDF 举报

"modelsim初学者教程,适合与quartus结合使用,提供详细的图文教程,内含modelsimSE10.0.c入门内容,强调了quartus10之后版本不再自带仿真软件,需要使用如modelsim这样的第三方工具。教程以一个计数器程序为例,介绍了在quartus11.0中调用modelsim10.0c进行仿真以及testbench的编写方法。"

在电子设计自动化(EEDA)领域,Modelsim是一款广泛使用的硬件描述语言(HDL)仿真器,它支持VHDL和Verilog等语言,帮助工程师在实际硬件制作之前验证设计的功能正确性。对于初学者来说,了解如何将Modelsim与Altera的Quartus集成是至关重要的步骤。

首先,从Quartus 10版本开始,不再内置波形仿真软件,用户需要自行安装如Modelsim这样的第三方仿真工具。在本教程中,使用的是Modelsim SE 10.0c版本,它与Quartus 11.0配合使用。

创建一个新的工程时,需要选择相应的仿真软件和语言。在这个例子中,选择了Modelsim作为仿真器,并使用Verilog HDL作为设计语言。接着,编写一个简单的计数器程序——count128.v,该程序接收输入时钟clk和复位信号rst_n,输出分频后的时钟divclk和数据data。

计数器程序的核心部分是一个always块,它在时钟上升沿或复位负边沿触发,如果复位有效,数据被置为8'h00;否则,数据自增1,实现了对输入时钟的128分频。

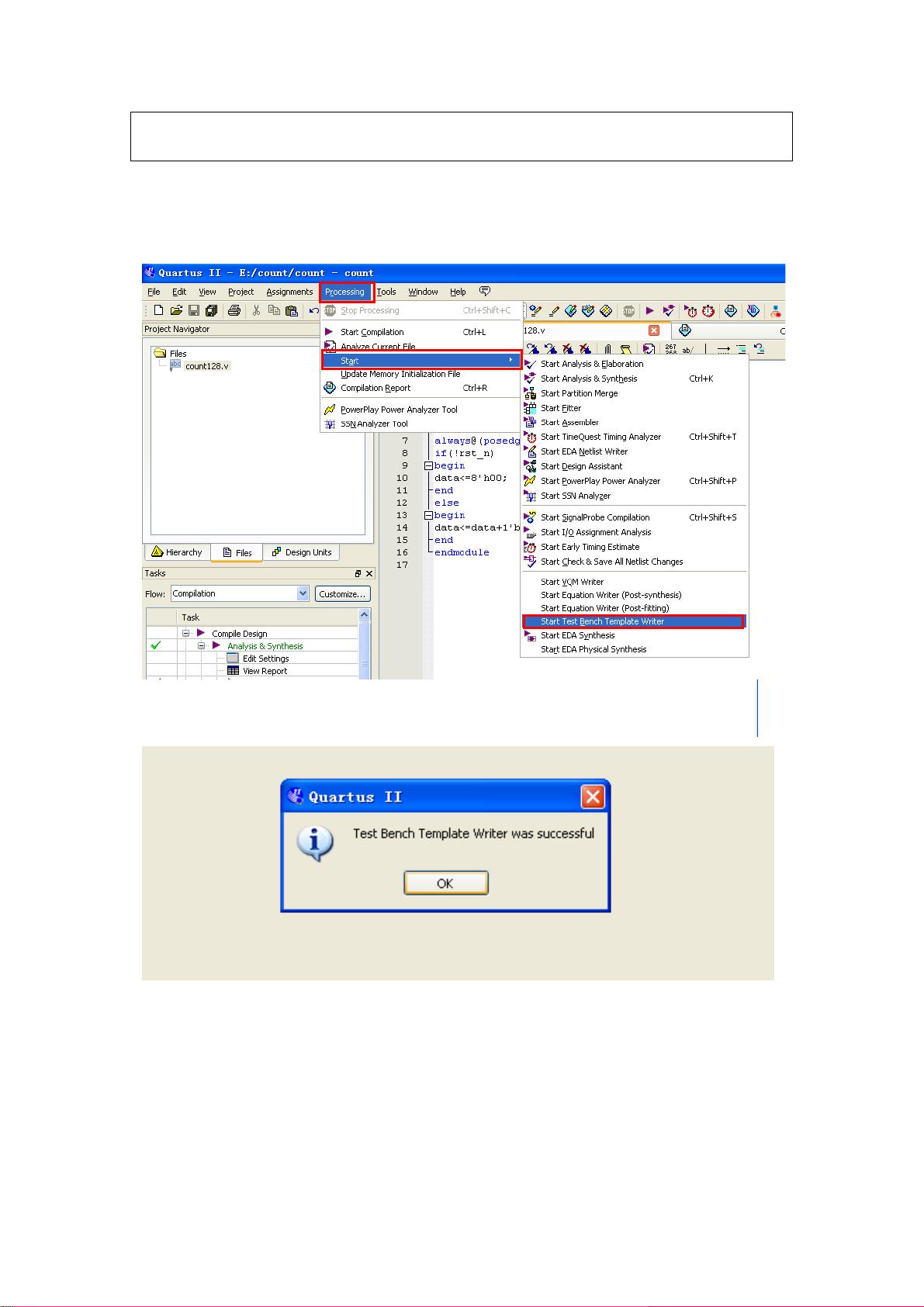

接下来,教程指导如何编写testbench。Testbench是用于测试设计功能的独立模块,它模拟真实环境中的输入信号,并捕获输出结果。在Quartus中,会生成一个默认的testbench模板,通常以.vt文件形式存在。用户需要根据设计的具体需求填充这个模板,定义输入信号、时钟和预期的输出。

在testbench中,`timescale指令用来设置时间单位和精度,这对于确保仿真结果的准确性至关重要。然后,声明并初始化各个寄存器和信号,模拟实际应用中的输入条件。在本例中,可能需要设定clk的周期,模拟复位操作,并设置data的初始值。

通过运行Modelsim,用户可以观察和分析仿真波形,验证计数器是否按照预期工作。这包括检查divclk是否每128个时钟周期翻转一次,data的值是否正确递增。

本教程为初学者提供了从建立工程到编写和仿真Verilog设计的基本步骤,帮助他们掌握如何在Quartus环境下利用Modelsim进行设计验证。通过这个过程,学习者能更好地理解和应用HDL语言,同时熟悉使用仿真工具来检验和调试数字电路设计。

795 浏览量

181 浏览量

125 浏览量

116 浏览量

125 浏览量

181 浏览量

322 浏览量

点击了解资源详情

点击了解资源详情

qq_41788198

- 粉丝: 0

最新资源

- Cisco Catalyst 2950/2955交换机配置指南

- 深入理解Apache Velocity

- Oracle JDeveloper 中的 Ajax 技术应用

- eBox-2300 Windows CE 6.0 开发指南:从零开始到实战应用

- C语言面试经典题解析:数据结构与算法实战

- 电脑发展史:从起源到新时代

- C/C++面试经典问题与技巧解析

- Oracle数据库函数详解

- IBM GPFS:高性能并行文件系统

- Progete教程:进阶操作与OWL数据库

- Protege新手入门:创建简单动物本体与基础用法教程

- 嵌入式开发:安全C/C++编码策略与实践

- 千万别用传统方式学英语:独特学习法揭秘

- 提升C语言上机调试效率的关键技巧

- 网上论坛BBS系统设计与功能详解

- SQL Server 2000:数据库开发与操作实践