NAND FLASH控制器磨损管理:芯片化硬实现策略

144 浏览量

更新于2024-08-28

收藏 513KB PDF 举报

"本文探讨了NAND FLASH控制器在应对NAND FLASH特性挑战时的磨损管理算法的芯片化硬实现,旨在提高存储性能和可靠性。"

在当前的存储技术中,NAND FLASH作为主流非易失性存储介质,广泛应用于eMMC、SATA SSD和PCIe SSD等控制器中。然而,NAND FLASH的固有特性使其容易遭受损耗,需要额外的管理机制来确保数据的持久性和系统稳定性。这些管理机制主要包括均衡磨损、坏块管理和逻辑地址到物理地址的映射。

均衡磨损管理是为了避免某些区块过度使用,导致提前失效。因为NAND FLASH的每个单元都有有限的擦写次数,如果某个区块被频繁写入,其寿命将远低于其他区块。通过算法,可以确保数据在多个区块间均匀分布,延长整个存储设备的使用寿命。

坏块管理是识别和隔离已经无法正常工作的区块。当NAND FLASH在写入或擦除过程中出现错误,该区块将被视为坏块,并需要将其从可用存储空间中剔除。控制器需要实时检测并维护坏块列表,以防止数据丢失。

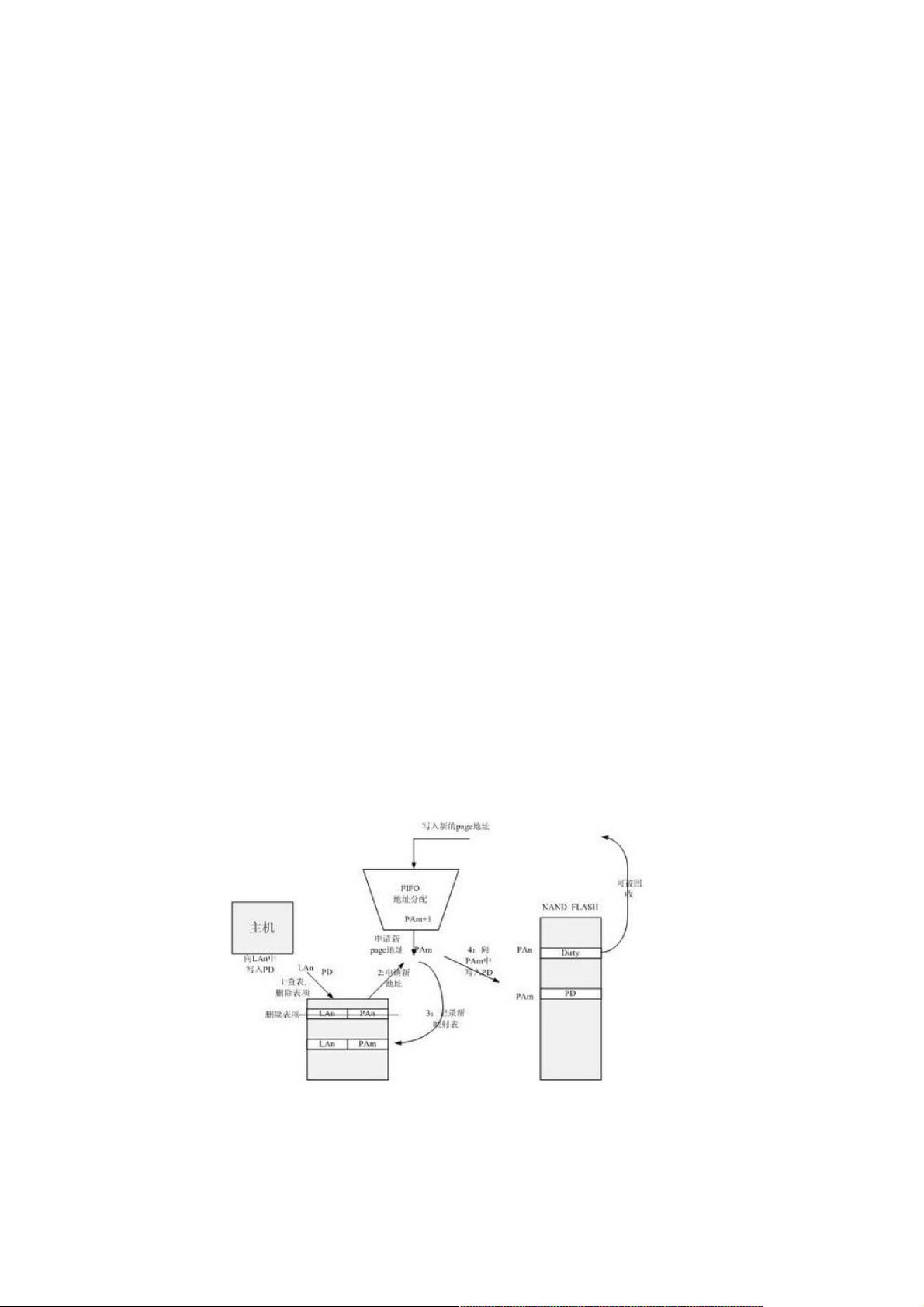

逻辑地址到物理地址的映射(通常称为FTL,Flash Translation Layer)是另一个关键功能。由于NAND FLASH的写入只能在未使用的页面进行,且一旦写入后不能直接覆盖,FTL负责跟踪这些映射关系,以便在需要时找到数据的正确位置。当一个页面被再次写入时,FTL会创建新的映射,旧的页面则需要被擦除。

传统的做法是在控制器中集成CPU,运行专门的软件(FTL固件)来执行这些任务。然而,随着存储速度的提升,对处理能力和响应时间的要求也随之增加,这可能需要更强大的CPU或多核处理器。为了解决这个问题,文章提出了将磨损管理算法硬件化,即芯片化硬实现。这种方案可以减少对高性能CPU的依赖,降低功耗,并提供更快的数据处理速度。

硬件实现的FTL可以通过专用电路和逻辑门来执行磨损均衡、坏块管理及地址映射,从而简化系统架构,优化性能。设计这样的硬件模块需要考虑到以下几点:

1. 必须能够快速找到可用的干净页面进行写入。

2. 需要内置错误检测和纠正机制,以应对NAND FLASH在写入和擦除时可能出现的错误。

3. 要能动态地更新和维护坏块列表,确保数据安全。

4. 逻辑地址与物理地址之间的映射表必须高效地存储和访问,以支持快速的数据查找和移动。

通过这样的硬件化设计,可以显著提高SSD的吞吐量和I/O延迟,同时降低整体系统的能耗,这对于高密集型应用和数据中心环境尤其重要。

总结来说,NAND FLASH控制器的磨损管理算法芯片化硬实现是一种创新策略,它通过硬件加速来解决软件FTL在高负荷场景下的性能瓶颈,以达到更高的存储效率和更低的能耗。这一方法对于推动存储技术的发展,尤其是在追求更高性能和更低功耗的现代存储解决方案中具有重要意义。

点击了解资源详情

223 浏览量

401 浏览量

123 浏览量

2021-08-24 上传

2021-10-25 上传

2024-11-24 上传

2024-11-25 上传

2022-03-20 上传

weixin_38725260

- 粉丝: 2

最新资源

- 支付宝订单监控免签工具:实时监控与信息通知

- 一键永久删除QQ空间说说的绿色软件

- Appleseeds训练营第4周JavaScript练习

- 免费HTML转CHM工具:将网页文档化简成章

- 奇热剧集站SEO优化模板下载

- Python xlrd库:实用指南与Excel文件读取

- Genegraph:通过GraphQL API使用Apache Jena展示RDF基因数据

- CRRedist2008与CRRedist2005压缩包文件对比分析

- SDB交流伺服驱动系统选型指南与性能解析

- Android平台简易PDF阅读器的实现与应用

- Mybatis实现数据库物理分页的插件源码解析

- Docker Swarm实例解析与操作指南

- iOS平台GTMBase64文件的使用及解密

- 实现jQuery自定义右键菜单的代码示例

- PDF处理必备:掌握pdfbox与fontbox jar包

- Java推箱子游戏完整源代码分享