74HC161与74HC163计数器设计与实验验证

需积分: 0 180 浏览量

更新于2024-07-01

收藏 1.7MB PDF 举报

本实验主要目标是通过实践操作来掌握常见的时序逻辑器件如74HC161和74HC163的逻辑功能、使用方法以及级联扩展技巧,进而学会用这些器件实现数字系统设计。实验内容主要包括两个部分:

1. 计数器设计:

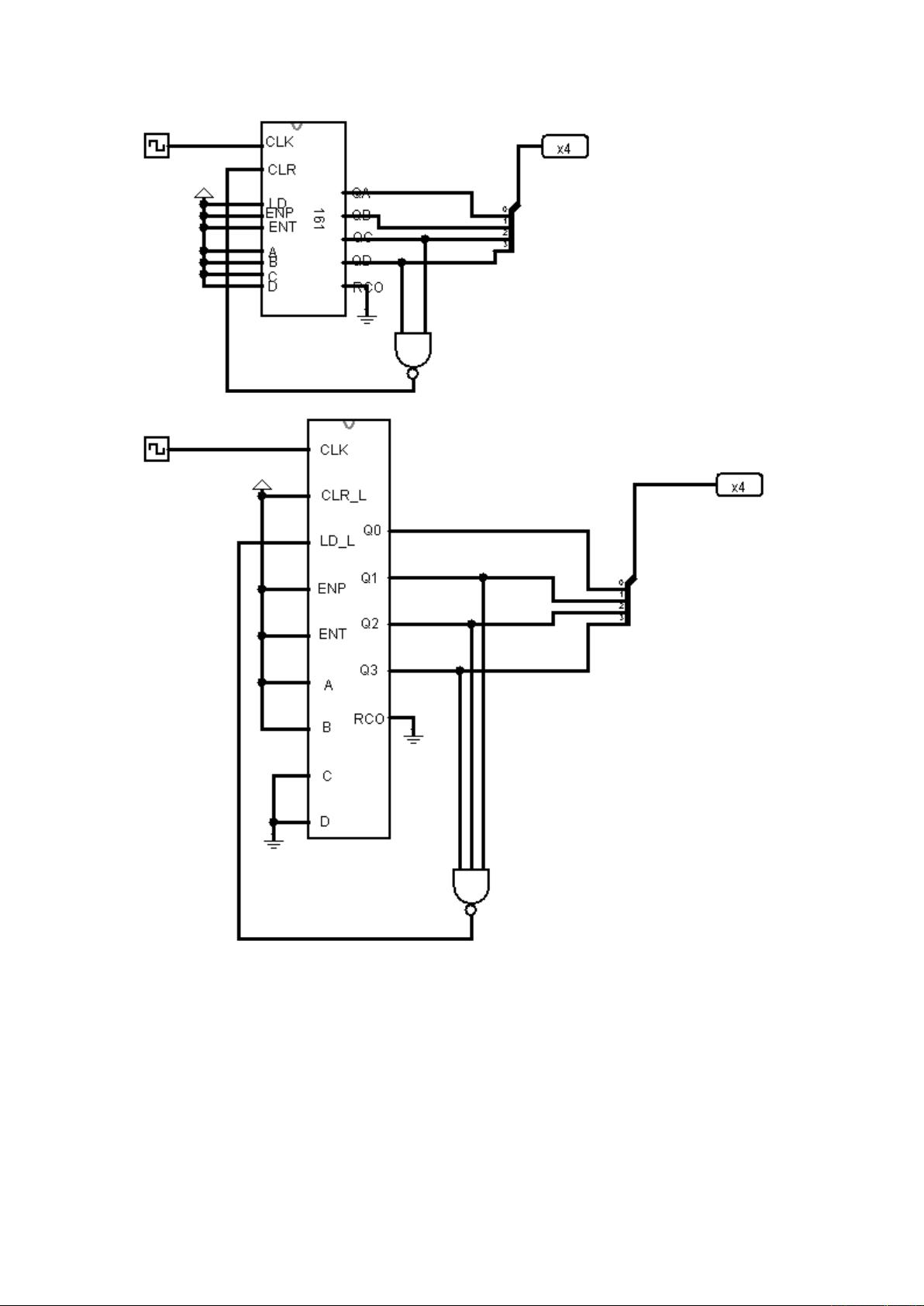

- 使用74HC161作为四位二进制异步清零计数器,设计0到11模12的计数器。该器件的特点在于可以通过清零端(Q3Q2Q1Q0)与非门的组合实现模数转换。实验者需根据74HC161的工作原理,构建状态转移表,确定逻辑表达式,并在Logisim软件中绘制电路图。实际操作中,要确保清零端的设置能够正确启动和终止计数过程。

- 同样使用74HC163,作为四位二进制同步清零计数器,设计3到14模12的计数器。这种方法需要预置初始值并通过置数端控制,将Q3Q2Q1接至三输入与非门,清零端的控制方式与74HC161不同,因为它是异步清零。

2. 数码管显示:

实现计数器输出到七段数码管的连接,观察计数值的变化。实验者需要理解如何将计数器的输出映射到数码管的各个段,确保计数器的输出能够正确驱动数码管显示相应的数字。

在整个实验过程中,学生会深入理解时序逻辑器件的工作原理,提升数字系统设计的实践能力,包括器件的选择、电路连接、逻辑分析和验证。同时,通过解决实际问题,如计数器的模数设定和同步异步的区别,增强了理论知识与实际操作的结合,有助于提高电子工程领域的专业技能。最后,通过实验照片和Logisim电路模拟,可以直观地展示实验结果和调试过程,进一步巩固学习成果。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-04 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

嗨了伐得了

- 粉丝: 26

- 资源: 290

最新资源

- R语言中workflows包的建模工作流程解析

- Vue统计工具项目配置与开发指南

- 基于Spearman相关性的协同过滤推荐引擎分析

- Git基础教程:掌握版本控制精髓

- RISCBoy: 探索开源便携游戏机的设计与实现

- iOS截图功能案例:TKImageView源码分析

- knowhow-shell: 基于脚本自动化作业的完整tty解释器

- 2011版Flash幻灯片管理系统:多格式图片支持

- Khuli-Hawa计划:城市空气质量与噪音水平记录

- D3-charts:轻松定制笛卡尔图表与动态更新功能

- 红酒品质数据集深度分析与应用

- BlueUtils: 经典蓝牙操作全流程封装库的介绍

- Typeout:简化文本到HTML的转换工具介绍与使用

- LeetCode动态规划面试题494解法精讲

- Android开发中RxJava与Retrofit的网络请求封装实践

- React-Webpack沙箱环境搭建与配置指南