构建存储器系统:练习题解析与地址译码

版权申诉

199 浏览量

更新于2024-08-25

收藏 842KB DOC 举报

"本文件是关于存储器的补充练习题答案,涵盖了存储器组织与设计的相关内容,包括地址译码、存储芯片的组合以及不同寻址空间的计算。"

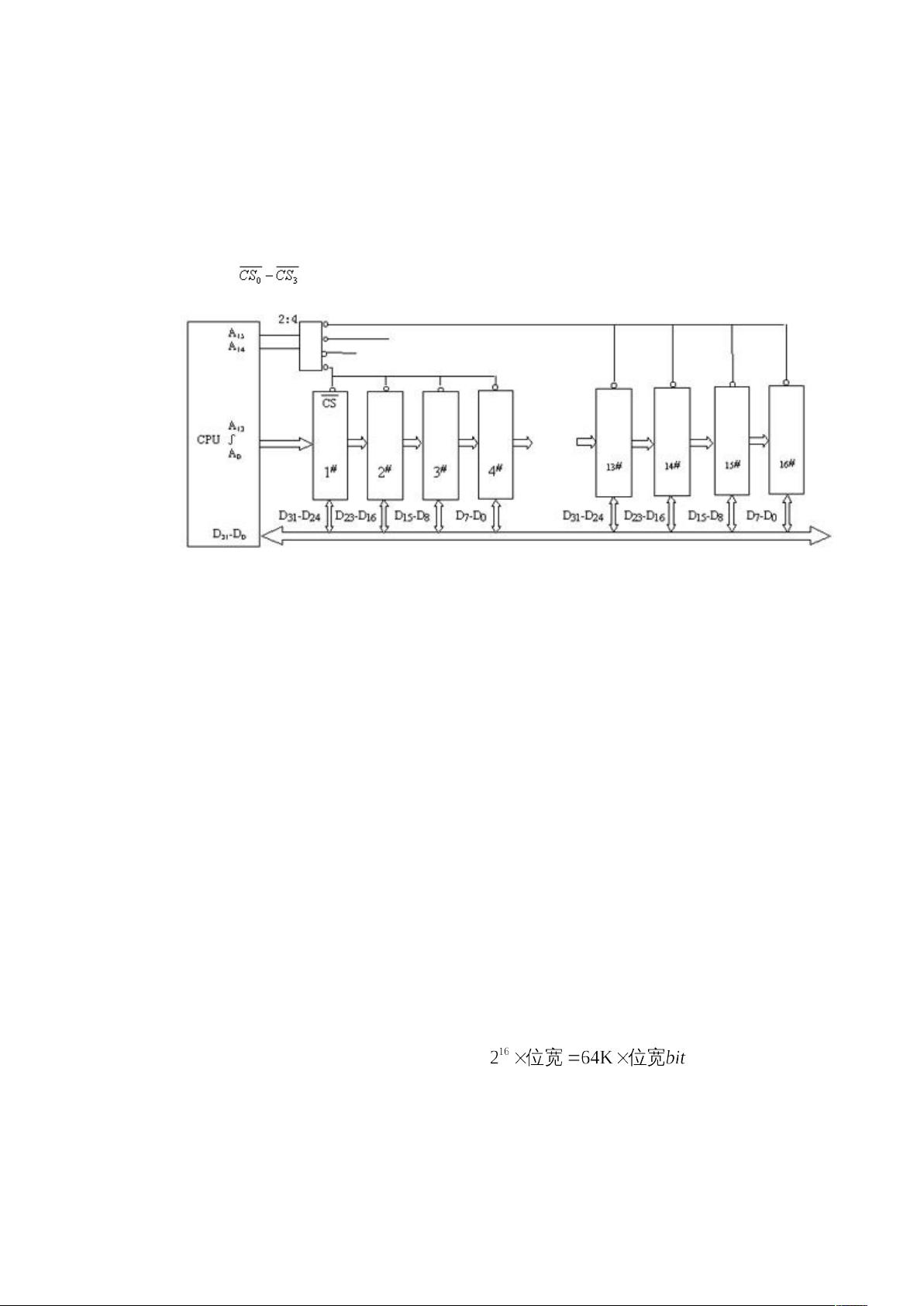

在计算机存储系统中,存储器的构建是一项关键任务,它涉及到地址线的使用、存储单元的组织以及地址译码器的设计。在题目5.10中,讨论了如何用16K×1位的DRAM芯片组成64K×8位的存储器。为了达到这个目标,我们需要计算所需芯片的数量。每8片16K×1位的DRAM芯片可以组成16K×8位的存储区。这意味着需要4组这样的8片组合,即总共32片DRAM芯片。地址线A13到A0用于在每片芯片内部寻址,而A15和A14则通过2:4译码器生成片选信号,以选择不同的存储芯片。

接着,5.11题考察了系统寻址空间的计算和存储器构建。在具有24条地址线的系统中,字长为8位,最大寻址空间为2^24 * 8 bit = 16M字节。如果使用SRAM2114(1K×4)芯片,由于每个芯片有1K个地址(10位地址线)且是4位宽,采用线选译码方式,10根地址线用于字选,剩下的14根地址线用于片选,因此需要28片SRAM2114芯片来构成存储系统。

在5.12题中,给出了三种不同情况下的存储器地址译码和连接图。在第一种情况中,系统有16根地址总线,采用8K×8位存储芯片构建64KB存储器,需要8片芯片,使用3根地址线进行片选。第二种情况是构建32KB存储器,同样使用8K×8位芯片,但只需要6片,因此使用2根地址线进行片选。第三种情况是构建16KB存储器,使用4K×8位芯片,需要4片,因此使用2根地址线进行片选。

在这些解题过程中,我们需要注意地址线的有效利用,避免地址不连续或重复,以优化存储器的设计并充分利用系统资源。例如,在5.16题的评论中,指出了一些潜在问题,如地址不连续可能导致驱动设计复杂,地址重复浪费地址空间,以及设计不易理解和实施。因此,在实际设计存储系统时,应充分考虑这些问题,确保地址译码方案的简洁和高效。

2010-03-20 上传

2024-07-18 上传

论文

论文

点击了解资源详情

论文

点击了解资源详情

2023-05-31 上传

2023-06-09 上传

等天晴i

- 粉丝: 5681

- 资源: 10万+

最新资源

- 十种常见电感线圈电感量计算公式详解

- 军用车辆:CAN总线的集成与优势

- CAN总线在汽车智能换档系统中的作用与实现

- CAN总线数据超载问题及解决策略

- 汽车车身系统CAN总线设计与应用

- SAP企业需求深度剖析:财务会计与供应链的关键流程与改进策略

- CAN总线在发动机电控系统中的通信设计实践

- Spring与iBATIS整合:快速开发与比较分析

- CAN总线驱动的整车管理系统硬件设计详解

- CAN总线通讯智能节点设计与实现

- DSP实现电动汽车CAN总线通讯技术

- CAN协议网关设计:自动位速率检测与互连

- Xcode免证书调试iPad程序开发指南

- 分布式数据库查询优化算法探讨

- Win7安装VC++6.0完全指南:解决兼容性与Office冲突

- MFC实现学生信息管理系统:登录与数据库操作