Vivado与ModelSim联合仿真教程:设置与常见问题

需积分: 49 33 浏览量

更新于2024-08-26

收藏 607KB DOCX 举报

"该文档详细阐述了如何在Vivado环境下与Modelsim进行联合仿真,以及如何解决在仿真过程中遇到的问题。"

在FPGA设计中,联合仿真是一种常用的方法,它能够结合Vivado的强大设计环境和Modelsim的优秀仿真功能。Modelsim是一款广泛使用的仿真工具,能够对硬件描述语言(如VHDL或Verilog)进行模拟和行为仿真。通过Vivado与Modelsim的联合仿真,用户可以更高效地验证设计的功能正确性。

首先,进行联合仿真的一个重要优势是自动化程度高。通过Vivado调用Modelsim进行仿真,用户可以避免手动编写Tcl命令,使得操作更为简便。此外,Vivado会自动分析并加载仿真所需的库,尤其在处理包含大量IP核和原语的复杂设计时,能有效减少手动配置可能出现的错误。

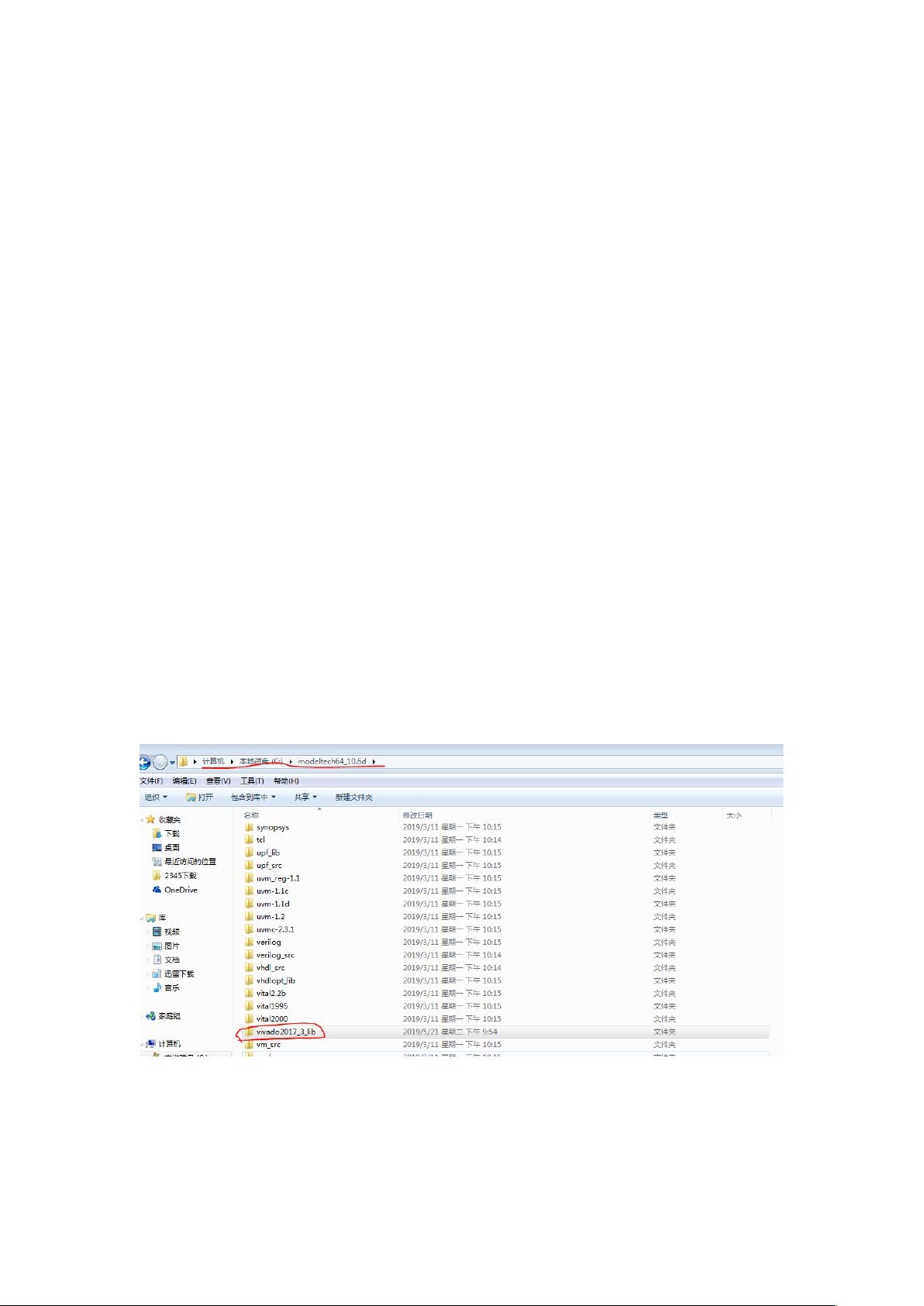

在进行联合仿真前,需要进行一些必要的设置。这包括在Vivado中编译Modelsim仿真所需的库,并将这些库存储在一个方便的位置,如Modelsim安装目录下的特定文件夹。同时,需要修改Modelsim的配置文件modelsim.ini,将编译的库添加到启动配置中。在Vivado中,还需要配置仿真库路径指向编译出的库文件,并指定Modelsim的启动程序路径。

仿真步骤通常包括以下几个环节:

1. 准备工程,确保所有仿真文件(如测试平台和激励模块)都已添加。

2. 选择要仿真的顶层文件,即测试用例。

3. 指定仿真内容,包括需要仿真的设计文件、测试激励(如时钟和复位信号)以及自定义数据类型(UDT)等。

4. 激活选定的测试用例,开始仿真过程。

在仿真过程中,可能会遇到一些常见问题。例如,如何保存和恢复观察信号的设置。若要保留当前仿真中的观察信号设置,可以在Modelsim中将其保存为do文件,最好使用与测试用例对应的名称,以避免混淆。当需要恢复上一次的仿真设置时,可以在下次启动Modelsim时,通过File—>Load do File加载先前保存的do文件。

Vivado与Modelsim的联合仿真提供了一种高效、便捷的设计验证手段,特别适合处理复杂的设计场景。通过合理设置和妥善管理仿真参数,用户可以更好地管理和重用仿真配置,提高工作效率。对于初学者和经验丰富的工程师来说,掌握这种联合仿真技术都是十分有益的。

2022-01-01 上传

2021-10-26 上传

2023-08-29 上传

2023-04-26 上传

2019-11-17 上传

2021-01-17 上传

2021-09-03 上传

2023-02-27 上传

2022-11-02 上传

meper

- 粉丝: 327

- 资源: 4

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目