5G与仪器仪表应用:ADI宽带接收器技术解析

需积分: 10 117 浏览量

更新于2024-08-11

收藏 803KB PDF 举报

"ADI-面向5G、仪器仪表和ADEF的宽带接收器-综合文档"

在无线通信领域,宽带接收器的设计与实现始终是技术的关键环节。随着5G、仪器仪表和航空航天与防御电子(ADEF)应用的发展,对宽带接收器的需求日益增长。这篇由ADI公司提供的文档深入探讨了这一主题,由Brad Brannon, Steve Dorn, 和 Vandita Pai Raikar撰写,旨在阐述如何克服传统接收器设计的局限,以满足现代通信系统对宽频带处理能力的迫切需求。

传统的无线电设计受限于带宽问题。早期的无线电先驱们因为检测器的限制,认为几百kHz以上的频率没有价值。然而,随着超级变频技术(super-heterodyning)的出现,由Armstrong和Levy等人完善,更高的频率得以利用,通过下变频技术将高频信号转换到检测器可以处理的较低频率。尽管如此,当时的带宽仍然是相对有限的。

直到最近几年,处理几十MHz以上的频率仍是一项挑战,通常需要昂贵的解决方案,这些方案往往依赖大规模并行的射频技术。设计者一直期望简化这一过程,实现能同时处理尽可能多带宽的方法。这种能力在过去几十年里逐渐发展,得益于半导体工艺的进步和集成技术的创新。

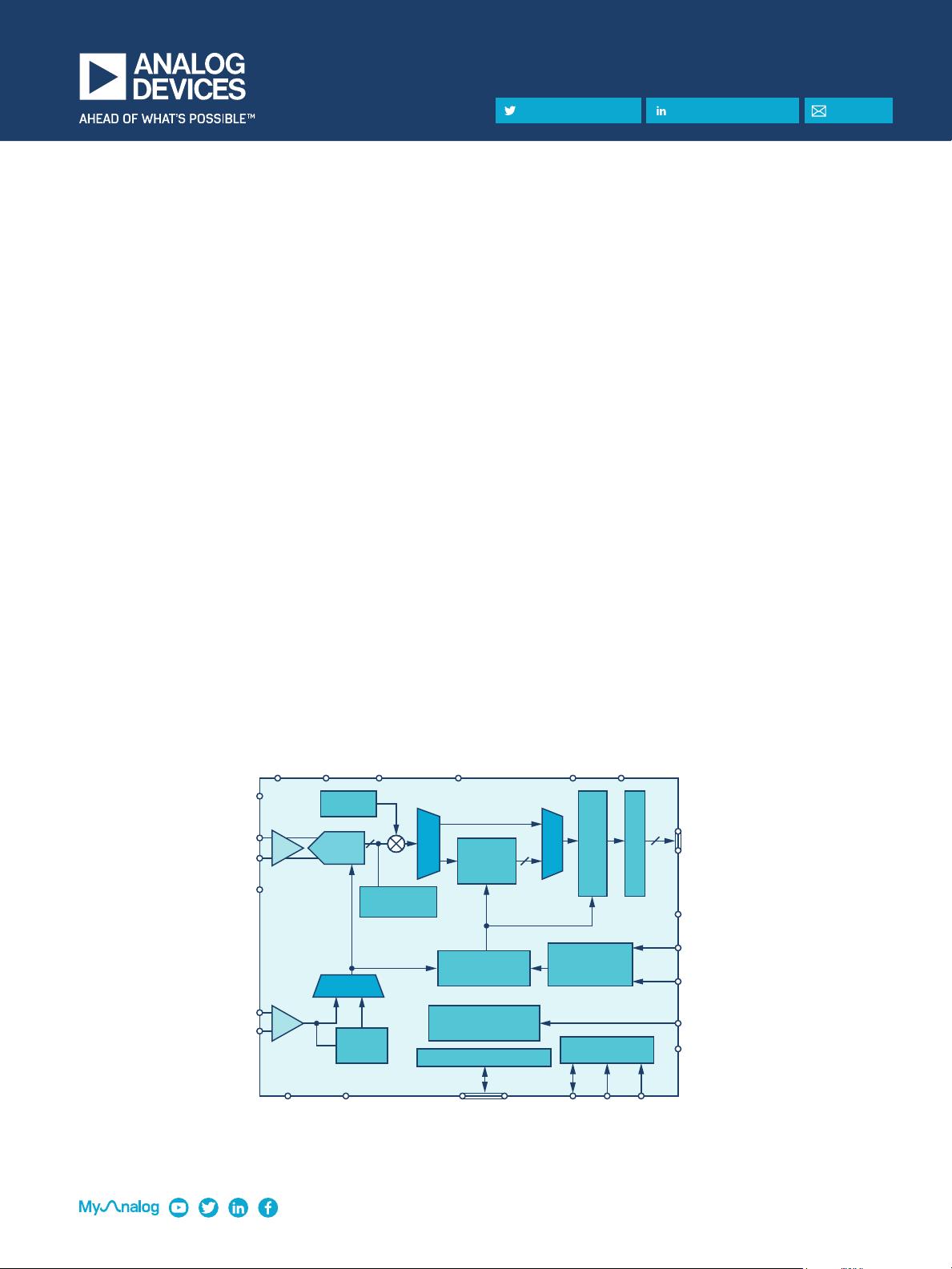

在5G通信中,高速数据传输和大量连接设备对接收器的带宽要求极高。为了支持多个频段、多种服务和高数据速率,宽带接收器必须具备高效能的信号处理能力,包括滤波、混频、放大和解调等。同样,在仪器仪表领域,高精度测量和宽动态范围也需要高性能的宽带接收器。而在ADEF应用中,接收器可能需要处理复杂的雷达和通信信号,对带宽和灵敏度有极高的要求。

文档可能会详细介绍ADI公司在宽带接收器设计上的最新技术和解决方案,如高性能的模拟前端(AFE)、数字信号处理(DSP)算法、以及如何利用先进的半导体工艺实现更高效的射频集成。此外,还可能涵盖如何优化接收器的噪声性能、选择合适的频率合成器、以及如何在保持低功耗的同时提升接收机的线性度和选择性。

这篇综合文档会提供一个全面的视角,深入讨论面向5G、仪器仪表和ADEF应用的宽带接收器设计的关键技术、挑战和未来发展趋势。对于从事相关领域的工程师和技术人员来说,这是一份极具价值的参考资料,有助于他们理解并解决实际工作中遇到的宽带接收器设计问题。

2021-09-25 上传

2019-08-13 上传

2021-10-11 上传

2023-06-08 上传

2023-05-20 上传

2023-05-25 上传

2023-03-29 上传

2023-04-24 上传

2023-03-28 上传

2023-06-13 上传

weixin_38720322

- 粉丝: 4

- 资源: 921

最新资源

- dc-portfolio-site

- liteBox-开源

- c10lp_refkit_zephyr:在C10LP RefKit FPGA板上的litex vexriscv内核上运行的演示Zephyr应用程序

- Tasky

- UpGuard Cyber Security Ratings-crx插件

- 算法:基本算法和数据结构实现

- JQuerygantt,jquery甘特图

- 参考资料-基于RS485和单片机的排队机控制系统设计.zip

- JRDropMenu:JRDropMenu可快速实现下拉菜单功能

- 源代码深度学习入门:基于Python的理论与实现

- HUPROG:一个包含HUPROG'17(Hacettepe大学编程竞赛)的问题和该问题的解决方案的回购

- Spotify-Data:扩展下载Spotify数据时提供的基本流历史记录数据

- 编码方式

- simple.rar_按钮控件_Borland_C++_

- lua-table:具有超能力的lua表

- bitwarden-menubar:macOS菜单栏中的Bitwarden