VHDL设计:八位十进制测频与数码管显示频率计

需积分: 13 180 浏览量

更新于2024-08-05

收藏 374KB DOC 举报

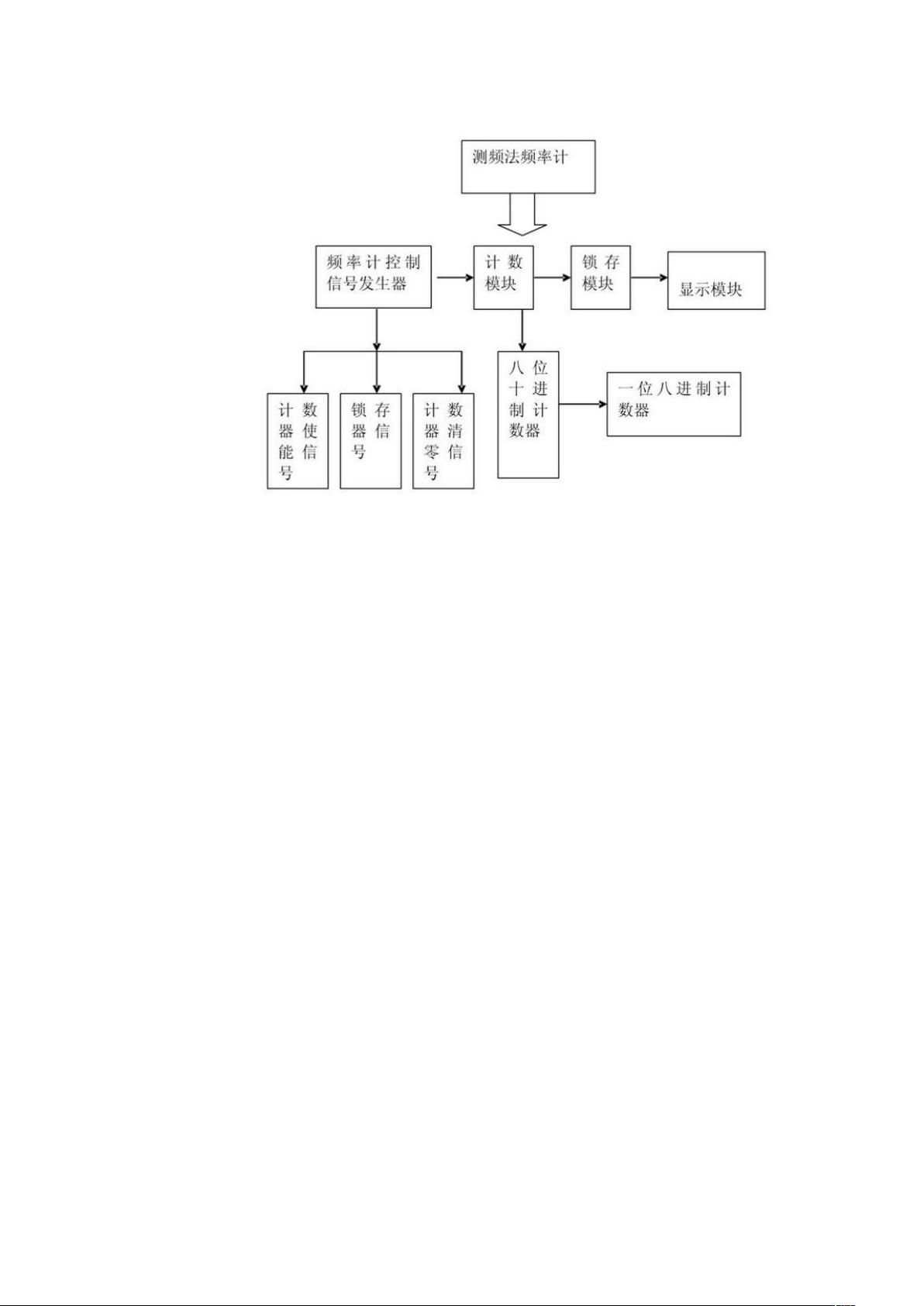

在这个八位十进制频率计数器的设计项目中,目标是构建一个能对方波信号进行频率测量并用数码管显示结果的系统。设计的核心组件包括测频控制信号发生器、计数模块以及所存模块。以下是对这些关键部分的详细阐述:

1. 题目分析:

设计的频率计是一种基于测频法的八位十进制计数器,它利用一个频率稳定的基准时钟来比较待测信号的频率。通过设置闸门时间,比如2秒,计算每秒内的脉冲数量来确定频率。闸门时间的选择影响精确度和刷新速度,长闸门时间提高精度但测量间隔长,短闸门时间则提供快速更新但可能牺牲精度。

2. 选择方案:

设计采用顶层原理图与底层VHDL语言相结合的方式,便于理解和实现,使整个设计结构清晰,易于维护。VHDL语言用于编写底层逻辑,确保了电路的灵活性和可编程性。

3. 细化框图:

- 测频控制信号发生器:负责产生一个1秒周期的计数使能信号EN,根据待测信号的频率同步计数。EN高电平期间计数,低电平则暂停并存储前一秒的计数值至锁存器,便于显示。

- 计数模块:由八个独立的一位十进制计数器组成,每个计数器都有时钟使能输入EN,仅在EN为高时计数。整个八位计数器通过VHDL编程实现,保证了计数的准确性。

- 所存模块:使用锁存器存储计数结果,防止因清零信号频繁出现导致显示的闪烁。当存储信号LOAD上升时,数据被存入锁存器,并通过译码器转换为数码管可以显示的数值。

4. 模块程序功能仿真:

对于测频控制和计数模块,分别进行了软件仿真,确保了信号的正确处理和计数的准确性。通过模拟不同频率输入,观察计数器的行为和数码管的显示效果,验证设计的正确性和性能。

这个项目不仅涉及数字逻辑设计,还涵盖了频率测量的基本概念,如闸门时间和频率稳定度的重要性,以及VHDL语言在硬件描述中的应用。通过实际操作,学生能够深入理解并掌握数字频率计的设计和实现过程。

2021-12-13 上传

2009-08-21 上传

2021-10-04 上传

2022-11-15 上传

2021-10-07 上传

2021-10-06 上传

2021-09-28 上传

2021-10-24 上传

2024-11-29 上传

小米饼干

- 粉丝: 3

- 资源: 5

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍