FPGA实现三相方波电源设计:Verilog接口详解

需积分: 0 112 浏览量

更新于2024-08-04

1

收藏 165KB DOCX 举报

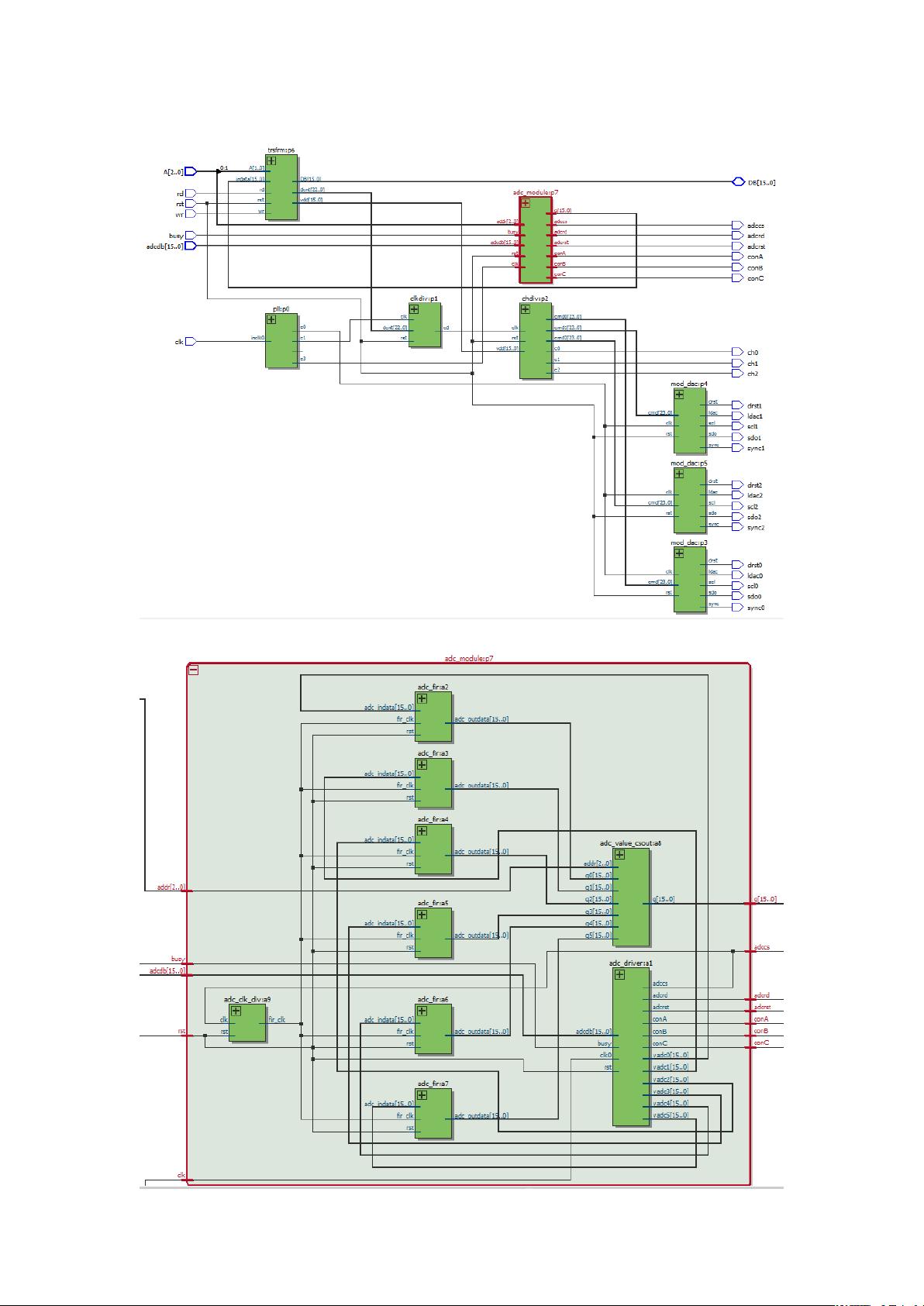

本文档主要探讨了基于FPGA的三相方波电源设计,重点介绍了Verilog代码实现的各个模块以及它们之间的接口信号。设计过程涉及多个关键组件,包括:

1. **整体RTL视图**:这个部分概述了整个FPGA设计的高级级描述语言(RTL)模型,它展示了各个模块如何在硬件级别相互连接。

2. **ADC模块RTL** 和 **DAC模块RTL**:这两部分详细介绍了用于模拟信号的模数转换器(ADC)和数字模拟转换器(DAC)的底层逻辑实现。它们通过输入/输出信号与上层模块进行通信,如ADC的数据总线(adcdb)和DAC的驱动信号(sync、scl、sdo、ldac、drst)。

3. **pro顶层实体模块**:这是设计的顶层模块,它负责集成ADC和DAC模块,并控制它们的工作。输入信号如clk、rst、wr、rd和FSMC总线用于数据传输和系统管理。输出信号如ch0、ch1、ch2、rstd*、ldac*、scl*、sdo*等是设计的核心功能,即三相方波信号的输出,以及与DAC时序相关的信号。

4. **锁相环模块**:该模块负责频率的合成和调整,将25MHz的晶振输入转化为50MHz DAC时钟(c0)、90MHz主时钟(c1)以及其他必要的时钟信号,如10MHz ADC时钟(c3)和100MHz逻辑分析仪时钟(c2)。

5. **clk_div模块** 和 **chdiv模块**:这两个模块分别用于对输入时钟进行分频,以适应不同模块的需求。clk_div模块接受时钟和复位信号,通过dcnt寄存器进行分频,产生cd时钟;chdiv模块则根据vdd电压设置输出的DAC命令(cmd0、cmd1、cmd2)以及相应的测试信号(c0、c1、c2)。

6. **mod_dac模块**:接收DAC命令(cmd),生成驱动信号(sync、scl、sdo、ldac、drst),以控制DAC的输出行为。

7. **dac_clk_src模块**:这部分专门负责提供DAC所需的时钟信号,与mod_dac模块紧密配合。

在设计过程中,还需要注意接口信号的同步、复位、读写控制,以及ADC转换忙时的处理。整个系统的设计旨在实现高效、精确的三相方波电源输出,并确保各个模块间的同步协调工作。Verilog代码的编写不仅要求对FPGA原理有深入理解,还要考虑到时序分析和资源优化,以满足实际应用中的性能需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-05-13 上传

2021-01-20 上传

2017-08-25 上传

2024-04-05 上传

2019-09-13 上传

点击了解资源详情

洪蛋蛋

- 粉丝: 31

- 资源: 334

最新资源

- Linux系统服务详解

- matlab实现游程编码

- ASP网上书店论文(毕业设计)

- ASP.NET程序中常用的三十三种代码

- java jdk命令 temp路径

- Developing Applications With OCAML

- INTRODUCTION OF MACHINE LEARNING OF Nilsson(Stanford Univ.)

- ssh的一本pdf电子书

- extjs实用开发指南.pdf

- Ajax开发详解诶-试读

- GCC 中文手册(gcc 使用)

- 湖南农业学校校园网络建设方案

- pv3d简单入门教程

- Ajax技术在Web Services应用中的安全研究

- 计算机专业数据库课程设计

- RS-232穿串行通信与单片机接口简介