基于FPGA的三相方波电源设计:Verilog接口与信号详解

需积分: 0 69 浏览量

更新于2024-08-05

收藏 319KB PDF 举报

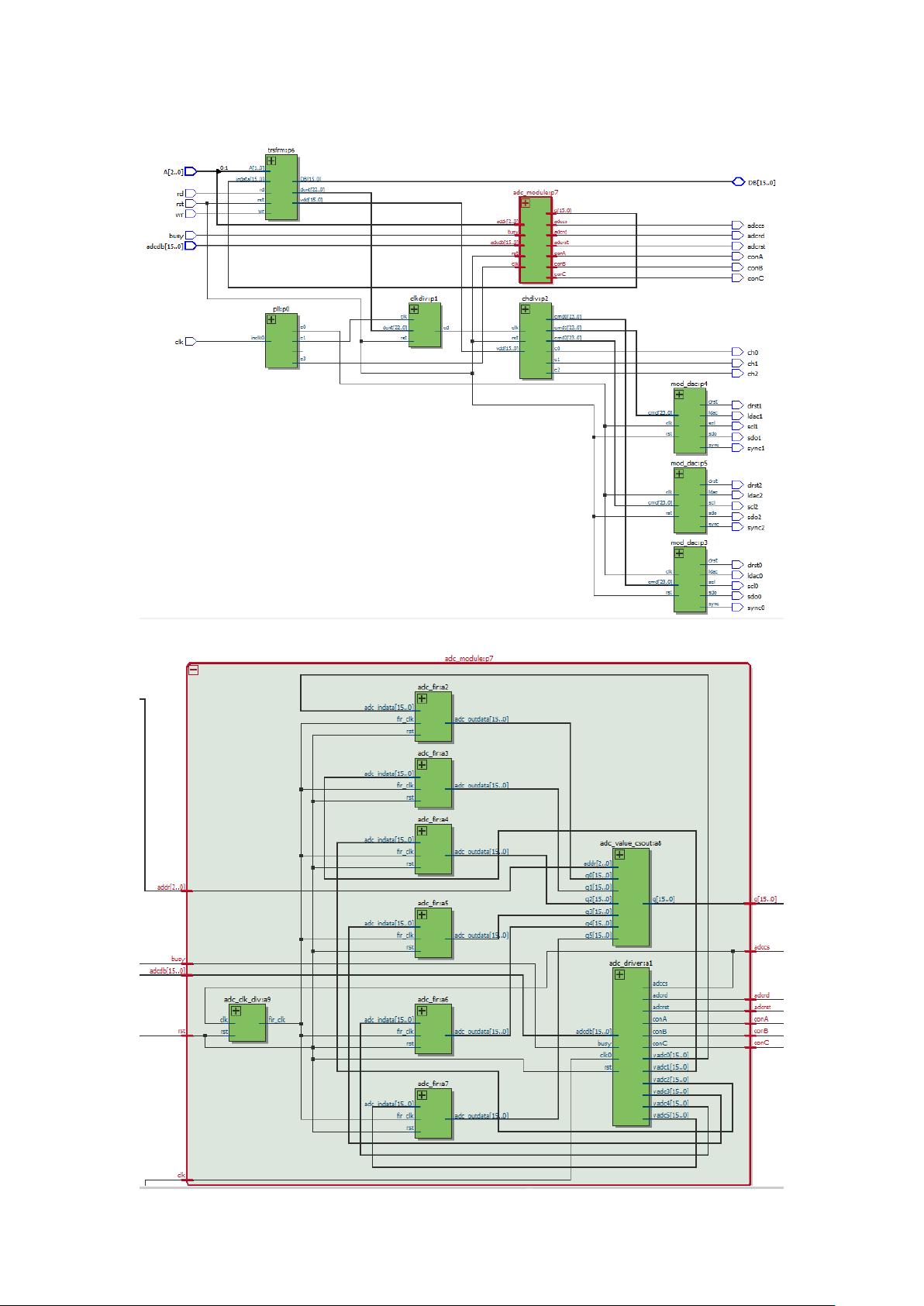

本篇文章主要介绍了基于FPGA的三相方波电源设计的详细实现,使用Verilog语言进行编程。设计的关键部分包括以下几个模块:

1. **顶层实体模块**:这个模块是整个设计的核心,它接收系统时钟(clk25MHz)和全局复位信号(rst),同时处理FSMC(Flexible Serial Memory Controller)的读写控制(wr, rd)、数据总线(DB)和地址总线(A)。此外,它还负责生成三相方波测试信号(ch0, ch1, ch2),以及与DAC(数字模拟转换器)时序产生相关的接口信号(rst0, ldac0, scl0, sdo0, sync0等)。

2. **ADC模块**:输入ADC的转换忙时信号(busy)和数据总线(adcdb),通过控制信号(conA, conB, conC)启动ADC的转换,并提供复位(adcrst)、片选(adccs)和读取(adcrd)信号。此外,它还连接到锁相环模块,用于处理ADC时钟的分频。

3. **锁相环模块**:接受25MHz晶振输入(clk0),生成50MHz DAC时序发生驱动时钟(c0)、90MHz分频主时钟(c1)、100MHz驱动逻辑分析仪时钟(c2),以及10MHz ADC模块驱动时钟(c3)。

4. **CLK 分频模块**(clk_div):通过输入时钟(clk)和复位信号(rst),配合分频系数(dcnt),产生分频后的时钟(cd)。

5. **CH 分频模块**(chdiv):根据全局复位(rst)和设定的电压(vdd),为每个相输出对应的DAC命令(cmd0, cmd1, cmd2),并提供三相方波测试信号(c0, c1, c2)。

6. **DAC 驱动模块**(mod_dac):接收DAC命令(cmd),生成同步信号(sync)、时钟信号(scl)、数据输出信号(sdo)、驱动信号(ldac)和驱动复位信号(drst)。

7. **DAC 时钟源模块**(dac_clk_src):为DAC模块提供时钟信号(clk),确保时序正确。

在整个设计过程中,作者详细地描述了各个模块之间的接口信号以及它们在硬件设计中的作用,这对于理解和实现FPGA中的多任务协同工作具有重要意义。设计者需要对Verilog编程有深入理解,以及对数字信号处理和FPGA硬件设计的最佳实践有清晰的认识。此外,这篇文章还涵盖了模拟数字转换器和时钟管理在实际应用中的关键细节,适合FPGA开发人员和相关领域研究者参考。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-05-13 上传

2021-01-20 上传

2017-08-25 上传

2024-04-05 上传

2019-09-13 上传

点击了解资源详情

小小二-yan

- 粉丝: 33

- 资源: 299