Quartus II 12.0 教程:Qsys, Nios II CPU及系统集成

"该教程详细介绍了如何使用Quartus II 12.0软件与Qsys系统集成工具来设计和配置Nios II嵌入式处理器系统。内容包括新建工程、Qsys中的组件添加与配置、时钟和复位网络的设定、元件之间的连接以及在Quartus II中对定制CPU的例化和管脚分配。"

在Quartus II 12.0版本中,Qsys是System Generator for SOPC(System on a Programmable Chip)的升级版,用于构建和配置复杂的SoC(System on Chip)设计。Nios II是一种可定制的软核处理器,适用于Altera的FPGA(Field-Programmable Gate Array)芯片。本教程的目标是教会用户如何使用Qsys和Nios II进行系统级的设计。

首先,教程讲解了如何新建一个工程,并启动Qsys。在Qsys环境中,用户可以选择不同的CPU类型,包括标准型Nios II处理器。CPU添加后,需要连接时钟和复位信号。在这个例子中,CPU的时钟(clk)被连接到系统时钟源clk_50,这通常是FPGA外部提供的50MHz时钟。

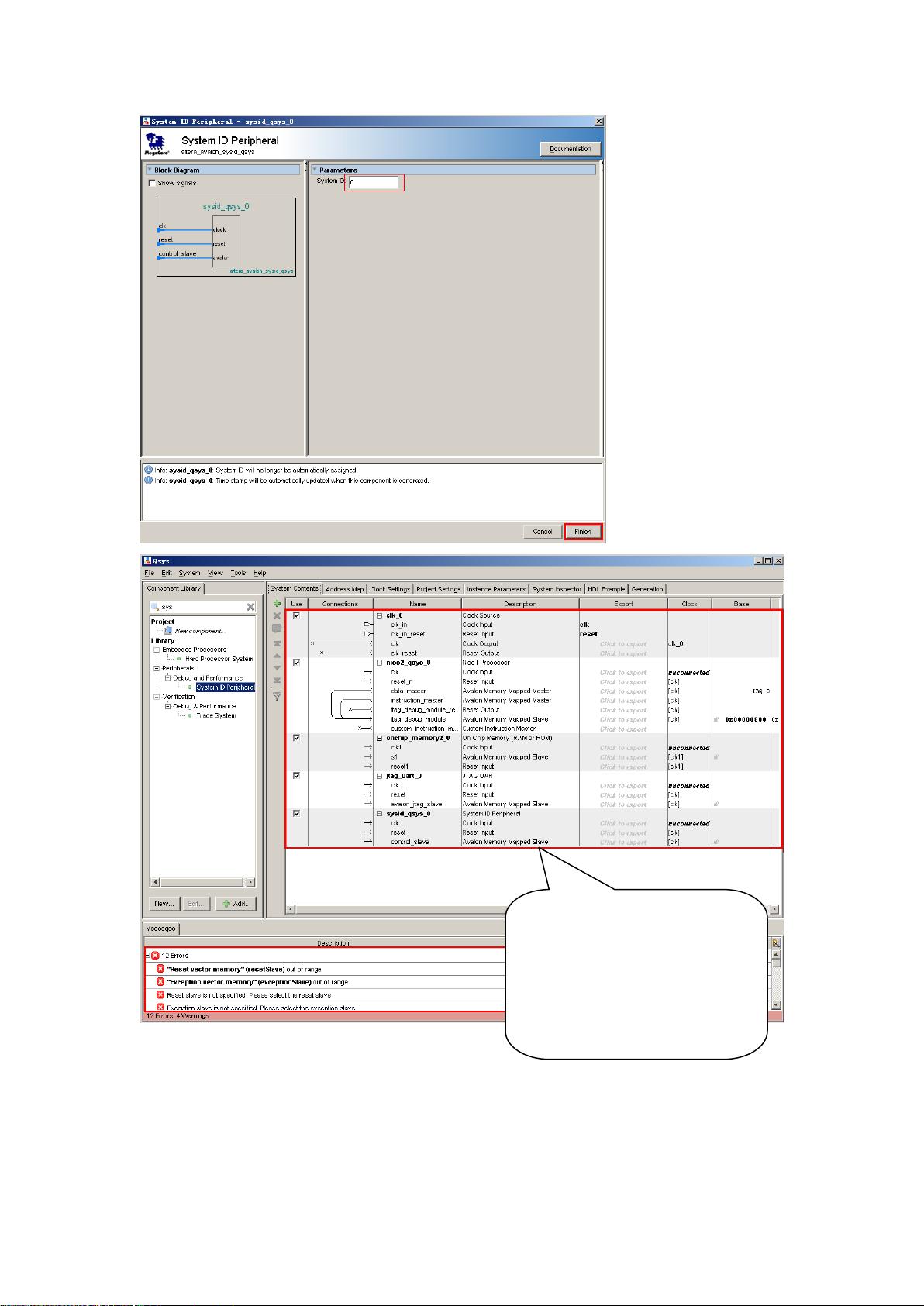

接下来,教程展示了如何添加片上内存(on-chip memory),并设置了它的大小为40KB。此外,还添加了JTAG UART用于调试和通信,以及System ID用于识别系统。每个组件的时钟都需要与系统时钟相连,这可以通过在组件属性中选择相应的时钟源实现。

在Qsys中,系统组件之间的连接是非常关键的步骤。例如,on-chip_memory的总线需要与CPU的数据和地址总线相连,以便CPU能够访问内存。同时,设置复位(reset_n)和异常(exception)信号,确保所有组件能正确响应复位操作,这里选择了onchip_mem作为复位和异常处理的位置。

当所有组件和连线设置完成后,需要保存Qsys设计并生成知识产权(IP)文件,通常是.qip文件。这个文件包含了Qsys配置的所有信息,可以被Quartus II项目引用。在Quartus II的顶层模块中,用户需要创建一个新的Verilog文件,然后例化之前定制的Nios CPU。这一步骤确保了CPU设计能够在FPGA逻辑中正确地实例化。

最后,教程指导用户进行管脚分配,这是将设计映射到具体FPGA芯片物理资源的过程。一旦完成,可以进行完全编译,查看RTL视图(Register Transfer Level),以验证硬件设计的逻辑正确性。这标志着硬件部分的设置完成。

本教程详尽地阐述了使用Quartus II 12.0和Qsys设计Nios II处理器系统的全过程,涵盖了从系统配置、组件连接到硬件实例化和管脚分配的各个环节,是学习和实践FPGA嵌入式系统设计的重要参考资料。

123 浏览量

786 浏览量

点击了解资源详情

211 浏览量

442 浏览量

123 浏览量

2014-12-16 上传

1131 浏览量

点击了解资源详情

hzj1028937670

- 粉丝: 0

- 资源: 7

最新资源

- Yolov5+Deepsort所需模型

- 【ssm项目源码】商户管理系统.zip

- vs2017+svn工具.rar

- ssm(spring+springMVC+mybatis)权限管理系统完整源码

- ProcessManager

- cabdriver:出租车的小帮手

- 教程:使用 MATLAB 进行并行和 GPU 计算(第 7 个,共 9 个):spmd:parfor 之外的并行代码:使用 MATLAB 进行并行和 GPU 计算的教程(第 7 个,共 9 个)-matlab开发

- MultiScreenDemo.7z

- 服装

- java面向对象 swing学生管理系统(完成)+报告.zip

- Akiyama:使用Aruppi API的动漫网站和移动应用程序

- oas2joi:根据开放API规范创建Joi模式

- festival:节日演讲综合系统

- QtModbus.rar

- springbootDemo.rar

- Markdown使用教程