可变带宽数字下变频FPGA设计:混频与抽取滤波详解

30 浏览量

更新于2024-08-31

收藏 422KB PDF 举报

本文主要探讨了可变带宽数字下变频的设计及其在FPGA平台上的实现。数字下变频作为一种关键的信号处理技术,在广播电视、移动通信和无线电监测等众多领域有着广泛应用。然而,传统数字下变频方案在带宽灵活性方面的不足,促使研究人员寻求新的解决方案。

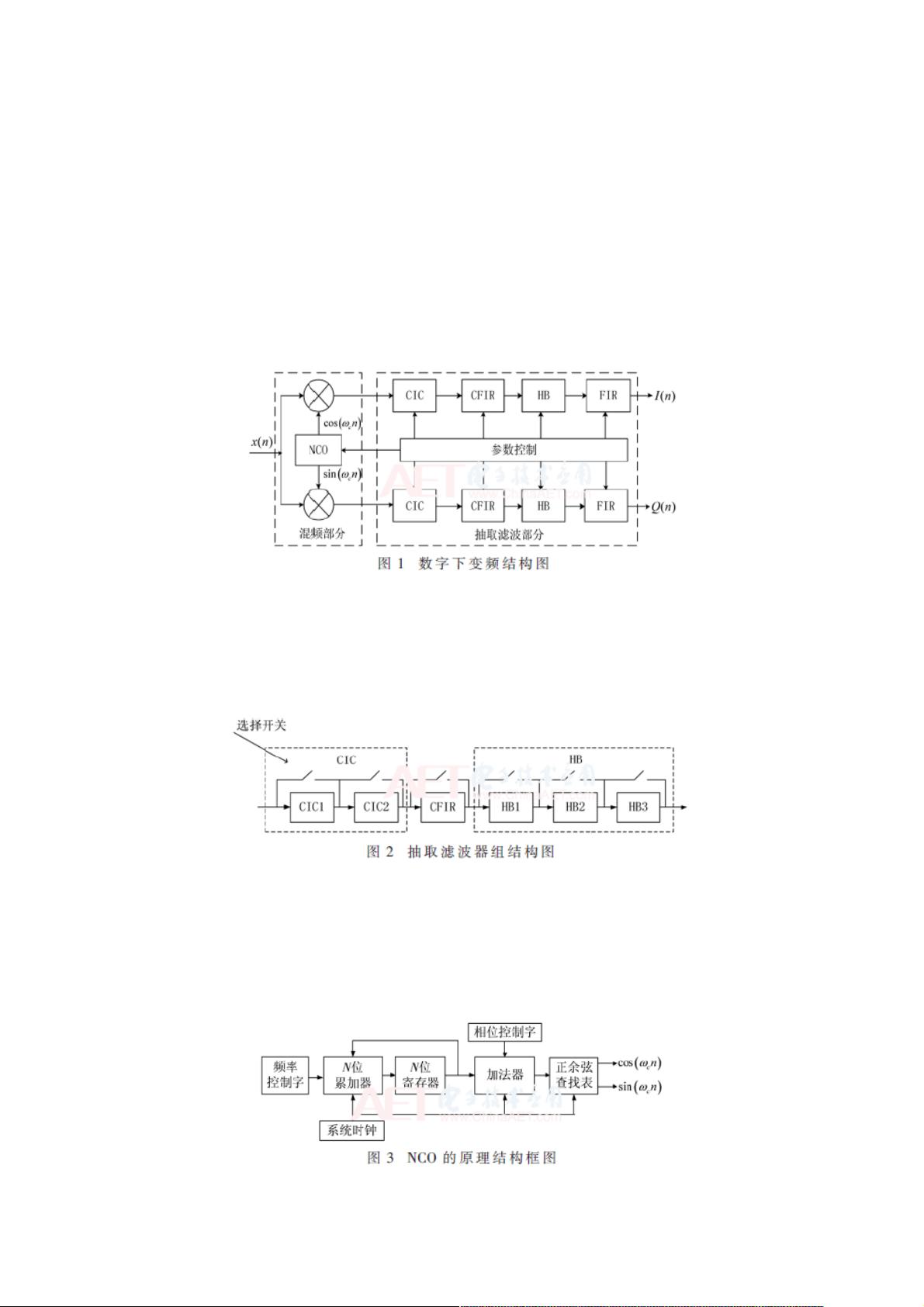

首先,文章详细介绍了数字下变频的基本结构,包括混频模块和抽取滤波模块。混频模块的核心是数字振荡器(NCO),它能够根据输入的频率控制字生成不同频率的正余弦本振信号,通过与基带信号相乘实现正交混频,将信号搬移到零中频位置。NCO的实现依赖于一个频率累加机制,通过调整频率控制字来改变输出信号的频率。

抽取滤波器组则是信号处理的关键环节,主要包括积分梳状滤波器(CIC)、补偿滤波器(CFIR)和半带滤波器(HB)。CIC滤波器以其简单的结构和高效性,利用抽取因子D进行信号抽样,仅包含加法运算。CFIR滤波器则提供更精确的滤波效果,而HB滤波器进一步优化了滤波性能。

为了验证这一设计方案的可行性,作者采用了Matlab作为仿真工具,利用其强大的数学计算能力和可视化功能,对不同带宽信号的下变频过程进行了模拟。同时,结合FPGA开发平台,通过硬件实现方式验证了方案的实际效能。FPGA的优势在于其并行处理能力,可以快速且灵活地执行复杂的数字信号处理任务,对于可变带宽需求的数字下变频而言,FPGA是一个理想的平台选择。

本文不仅深入剖析了数字下变频的原理和设计方法,还展示了如何利用FPGA技术来实现其在不同应用场景下的高效、灵活工作。实验结果表明,提出的可变带宽数字下变频方案在理论上和实践上都是可行的,对于提升通信系统的适应性和效率具有重要意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-10-26 上传

2020-11-05 上传

2020-10-17 上传

2010-05-09 上传

2018-01-07 上传

2012-02-19 上传

weixin_38679045

- 粉丝: 9

- 资源: 890

最新资源

- ember-scrud:通过实践学习 ember.js 和 ember-cli

- curve_fit_plus

- google-books-browser-react-native:教程摘自Manuel Kiessling的《使用React Native开始移动应用程序开发》

- meteor-feed:纯净Meteor代码构建的点餐系统

- 使用OpenCV-CNN在网络摄像头上进行人脸识别:该项目通过使用网络摄像头流式传输实时视频来检测带有或不带有面具的人脸

- Object-Oriented-Programming-Principles-and-Practice:面向对象的编程原理和实践-2018Spring

- 海浪音乐盒网站系统官方版 v3.5

- catalogue_panorama

- tadaaam:视口入口动画库

- MRSS:用于生成 mrss 饲料的样板

- 恒压供水PLC程序aa.rar

- redux-react-tutorial:在这个仓库中,我将通过在React.JS中使用它来教你Redux

- luluordrgen

- Read Body Language-crx插件

- angular-2-and-TypeScript-calculator

- learninggruntplugin-lieaqnes:学习设置 grunt 插件