MIPS32® 24KEc™ Processor Core Datasheet, Revision 01.02 11

Copyright © 2005 MIPS Technologies Inc. All rights reserved.

per-page granularity. The 24KEc implementation

allows a wide range of page sizes to be present

simultaneously.

2. Fixed Mapping Translation (FMT) -style MMU. The

FMT is much simpler and smaller than the TLB-style

MMU, and is a good choice when the full protection

and flexibility of the TLB is not needed.

Translation Lookaside Buffer (TLB)

The TLB consists of three address translation buffers:

• 16/32/64 dual-entry fully associative Joint TLB (JTLB)

• 4-entry fully associative Instruction Micro TLB (ITLB)

• 8-entry fully associative Data Micro TLB (DTLB)

When an instruction or data address is calculated, the

virtual address is compared to the contents of the

appropriate micro TLB (uTLB). If the address is not found

in the ITLB or DTLB, the JTLB is accessed. If the entry is

found in the JTLB, that entry is then written into the uTLB.

If the address is not found in the JTLB, a TLB exception is

taken.

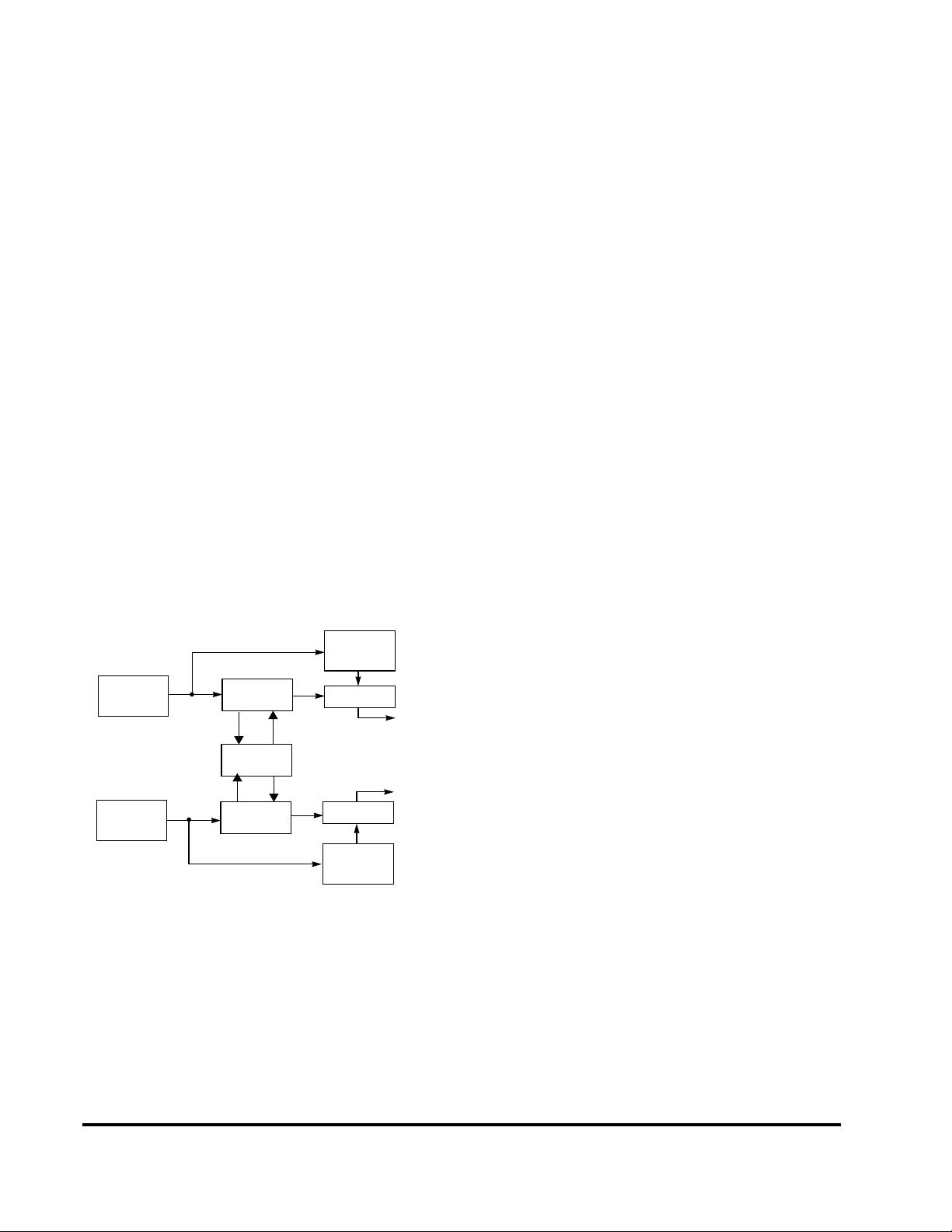

Figure 4 shows how the ITLB, DTLB, and JTLB are

implemented in the 24KEc core.

Figure 4 Address Translation During a Cache Access

Joint TLB (JTLB)

The 24KEc core implements a fully associative JTLB

containing 16, 32, or 64-dual-entries mapping up to 128

virtual pages to their corresponding physical addresses.

The purpose of the TLB is to translate virtual addresses and

their corresponding ASIDs into a physical memory

address. The translation is performed by comparing the

upper bits of the virtual address (along with the ASID)

against each of the entries in the tag portion of the joint

TLB structure.

The JTLB is organized as pairs of even and odd entries

containing pages that range in size from 4 KB to 256 MB,

in factors of four, into the 4 GB physical address space. The

JTLB is organized in page pairs to minimize the overall

size. Each tag entry corresponds to two data entries: an

even page entry and an odd page entry. The highest order

virtual address bit not participating in the tag comparison is

used to determine which of the data entries is used. Since

page size can vary on a page-pair basis, the determination

of which address bits participate in the comparison and

which bit is used to make the even-odd determination is

decided dynamically during the TLB look-up.

Instruction TLB (ITLB)

The ITLB is a small 4-entry, fully associative TLB

dedicated to performing translations for the instruction

stream. The ITLB only maps 4 KB or 1 MB pages/

subpages. For 4 KB or 1 MB pages, the entire page is

mapped in the ITLB. If the main TLB page size is between

4 KB and 1 MB, only the current 4 KB subpage is mapped.

Similarly, for page sizes larger than 1 MB, the current 1

MB subpage is mapped.

The ITLB is managed by hardware and is transparent to

software. The larger JTLB is used as a backing structure for

the ITLB. If a fetch address cannot be translated by the

ITLB, the JTLB is used to attempt to translate it in the

following clock cycle, or when available. If successful, the

translation information is copied into the ITLB for future

use. There is a minimum two cycle ITLB miss penalty.

Data TLB (DTLB)

The DTLB is a small 8-entry, fully associative TLB

dedicated to performing translations for loads and stores.

Similar to the ITLB, the DTLB only maps either 4 KB or 1

MB pages/subpages.

The DTLB is managed by hardware and is transparent to

software. The larger JTLB is used as a backing structure for

the DTLB. If a load/store address cannot be translated by

the DTLB, a lookup is done in the JTLB. If the JTLB

translation is successful, the translation information is

copied into the DTLB for future use. The DTLB miss

penalty is also two cycles.

Instruction

Address

Calculator

ITLB

DTLB

Data

Address

Calculator

Comparator

Comparator

Instruction

Cache

Tag RAM

Data

Cache

TagRAM

Virtual Address

Virtual Address

Instruction

Hit/Miss

Data

Hit/Miss

JTLB

IVA

Entry

Entry

DVA