小体积高功率密度电源管理解决方案在RF系统与FPGA中的应用

55 浏览量

更新于2024-09-01

收藏 630KB PDF 举报

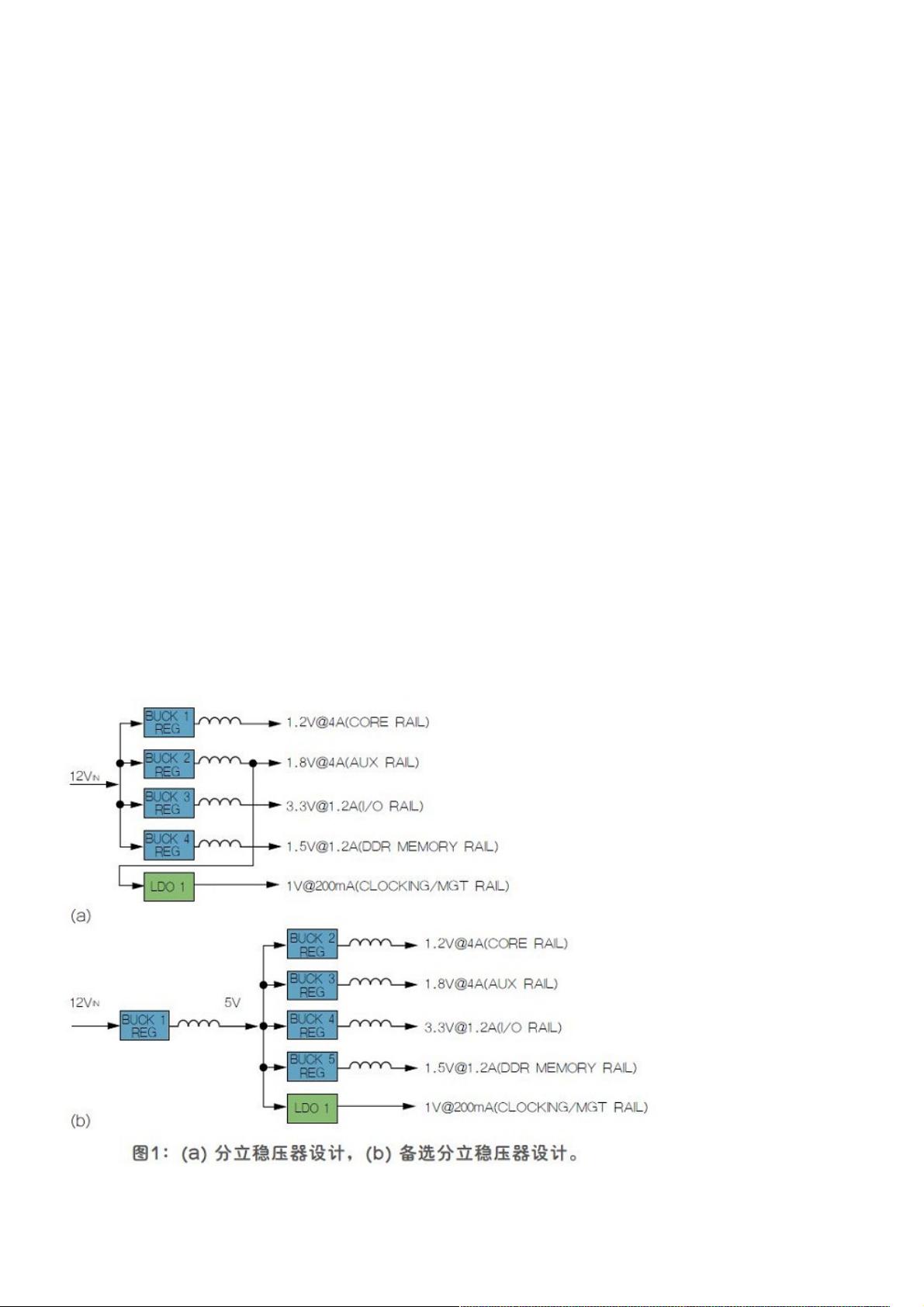

"本文探讨了高度集成的电源管理解决方案,主要关注它们在RF系统、FPGA和处理器供电中的应用,以及如何通过先进的设计工具帮助工程师迅速实现创新设计。随着通信基础设施的发展,小蜂窝系统对电源管理提出更高要求,需要在有限空间内提供高功率密度。同时,医疗和仪器设备的微型化趋势也对电源效率和FPGA、处理器的供电方式提出挑战。文章列举了典型的设计规格,并对比了两种不同的电源管理方案。"

在当前的技术环境中,电源管理解决方案正变得越来越集成和高效。针对RF系统,这些新解决方案需要处理复杂的供电需求,比如为RF收发器和功率放大器提供高密度电源,同时确保低噪声以保持RF性能不受影响。例如,采用同步开关稳压器以避免开关频率干扰关键RF频段,并利用LDO为敏感部件如AD9361RF捷变收发器供电。此外,电源时序控制是至关重要的,确保RF收发器在数字基带启动并运行之后才被启用,防止潜在的损坏。

对于FPGA和处理器供电,尤其是医疗和便携式设备中的应用,电源管理需要在小面积上提供快速瞬变响应和大电流,同时满足低噪声要求,以支持内部模拟电路如锁相环(PLL)。电源时序控制是确保FPGA在存储器启动前上电的关键,而精确的使能输入和电源良好输出则有助于监控和故障检测。设计的灵活性允许电源IC的电流限值可调,从而实现设计重用,加速产品上市进程。

文章中列举了一个FPGA多轨电源管理的实例,包括1.2V、1.8V、3.3V、1.5V和1.0V的电轨,分别对应内核、辅助、I/O、DDR存储器和时钟供电。两种常见的设计方案分别是使用多个开关稳压器直接连接到12V输入,或者通过一个稳压器先将12V降至5V中间轨,再进行后续调节。每种方案都有其优点和适用场景,例如预调节LDO可以降低功耗,而中间轨方法则简化了电源路径。

总结来说,高度集成的电源管理解决方案在应对通信基础设施、医疗设备和仪器的小型化挑战中发挥着核心作用。通过高效的电源分配、低噪声设计、电源时序控制以及故障监控,这些解决方案不仅提高了系统的性能,还缩短了产品开发周期,为工程师提供了强大的设计工具。

2021-01-13 上传

2020-10-20 上传

2021-01-12 上传

2021-05-23 上传

2020-12-01 上传

2020-10-16 上传

2020-11-29 上传

2020-12-03 上传

2020-11-26 上传

weixin_38545517

- 粉丝: 2

- 资源: 957

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目