FPGA PCIe接口设计解析:协议分析与事务层核心

版权申诉

PCIE(Peripheral Component Interconnect Express)协议是一种高速、低延迟的总线标准,主要用于连接计算机内部的处理器、内存、存储设备和其他扩展卡。该文档深入探讨了PCIE协议的基本概念以及在FPGA(Field-Programmable Gate Array)中的应用设计。

PCIE协议的核心组件包括根复合体(Root Complex),它是整个系统的关键,负责初始化和管理PCIE连接,它能够启动PCI-E事务,并与CPU和主内存进行交互。交换器(Switch)作为多设备间的通信中枢,通过ID路由、地址路由或隐式路由技术,确保数据流在复杂的系统架构中高效地传递。

Endpoint(端点)是PCIE协议中的基本实体,可以是请求者(发起数据传输的设备)或完成者(接收数据的设备),在FPGA设计中,需要实现这些角色以支持数据的发送和接收。Port是设备与PCIE链路之间的接口,而Bridge则用于兼容不同标准的设备间通信,如PCI-E到PCI/PCI-X的转换。

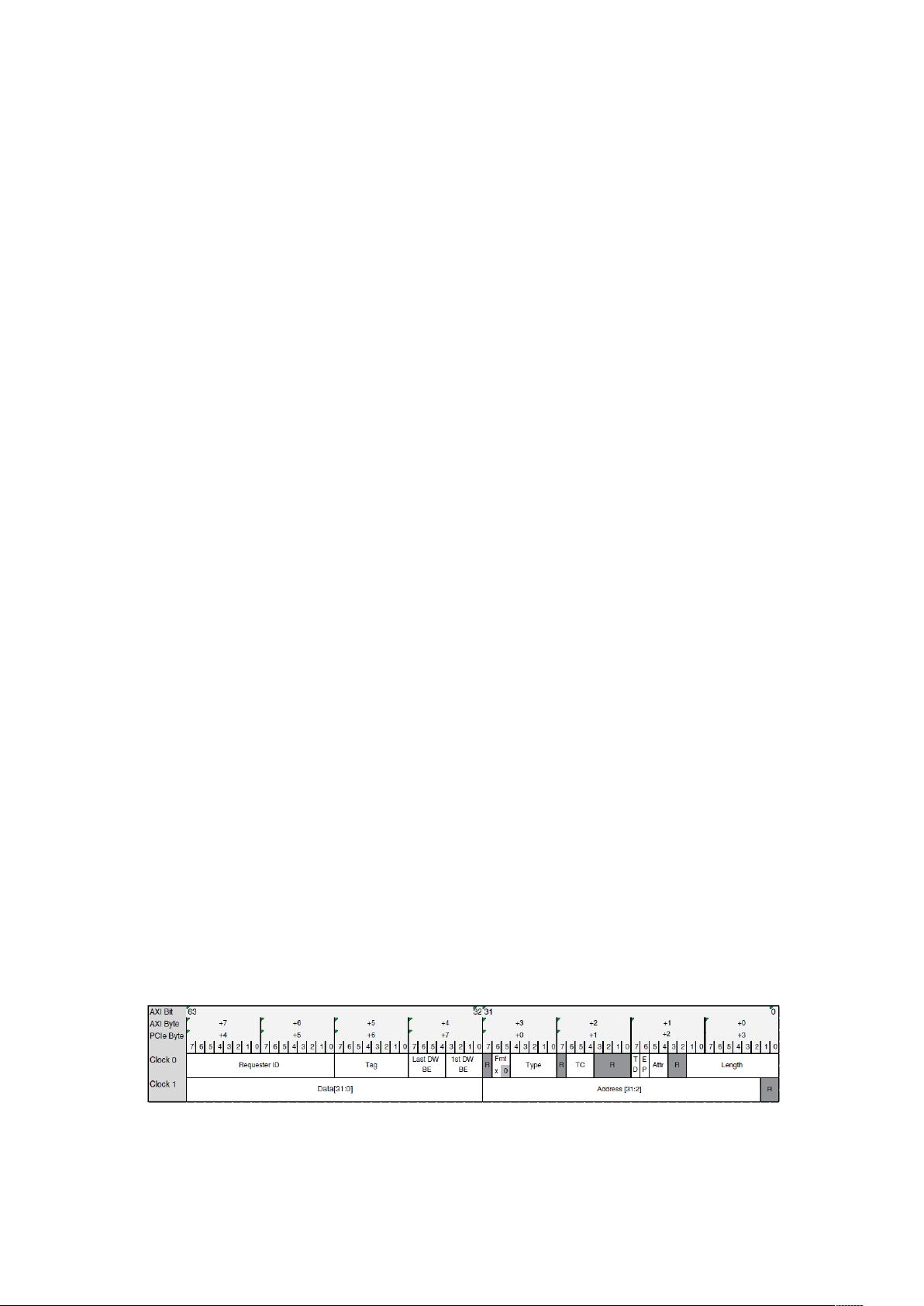

PCIE协议采用分层结构,包括事务层、数据链路层和物理层。事务层负责处理高层应用的请求,生成TLP(Transaction Layer Protocol)并管理信用机制,支持配置、I/O、存储和消息事务。在数据链路层,DLLP(Data Link Layer Protocol)负责错误检测和确认,而在物理层,PLP(Physical Layer Protocol)负责信号的编码和解码,确保数据在电或光介质上的可靠传输。

在FPGA设计中,主要关注的是事务层的处理,因为这涉及到与外部设备的直接交互。CPU作为系统控制中心,发出所有数据请求,这些请求通过MMIO(Memory-Mapped Input/Output)接口操作存储器映射区域。RootComplex负责响应这些请求,并通过生成包含地址、字节使能和寄存器内数据的TLP包,驱动数据向下游移动。

文档详细讲解了PCIE协议的各个组成部分及其在FPGA中的具体实现,强调了CPU的主导作用以及各层协议包的生成、传输和处理过程。理解并掌握这些知识对于开发高性能的FPGA PCIe接口至关重要,能帮助工程师设计出高效、兼容性强的硬件系统。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-06-20 上传

2022-11-27 上传

2022-07-02 上传

2022-07-02 上传

2021-11-18 上传

纯阳之道

- 粉丝: 5

- 资源: 16

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程