Cadence版图设计入门:Virtuoso编辑与inverter制作

需积分: 11 95 浏览量

更新于2024-07-29

收藏 853KB PDF 举报

Cadence是一款广泛应用于电子设计自动化(EDA)领域的软件套件,其中的版图设计工具Virtuoso是核心组件之一。本文主要介绍了如何在Cadence环境中进行基本的文件操作和创建一个简单的非门版图实例,以帮助用户熟悉Virtuoso编辑器的工作流程。

首先,章节2.1讲解了如何建立版图文件。用户需要使用Library Manager创建一个新的库myLib,与之前介绍的cdsSpice有所不同,因为版图设计涉及到技术文件的编译,所以选择"compile a new techfile"或"attach to an existing techfile"。在这个例子中,我们选择新建技术文件。用户需要输入ASCⅡ技术文件名(如csmc1o0.tf),然后创建名为inv的单元格。为了完整起见,建议用户同时建立schematic view、symbol view,定义PMOS和NMOS的尺寸(如长度和宽度),并选用合适的模型(如hj3p和hj3n)。

接下来,2.2节讲述了绘制inverter掩膜版图的准备工作。在Library Manager中打开inv的layout view,启动Virtuoso编辑器,用户将看到一个包含Iconmenu(图标菜单)、menubanner(菜单栏)和status banner(状态栏)的版图视窗。Iconmenu提供常用命令的图标,通过悬停鼠标可显示对应指令。menubanner则组织了一系列编辑版图的命令,如Zoom In(放大)、Zoom out by 2(缩小2倍)以及Save等快捷键。

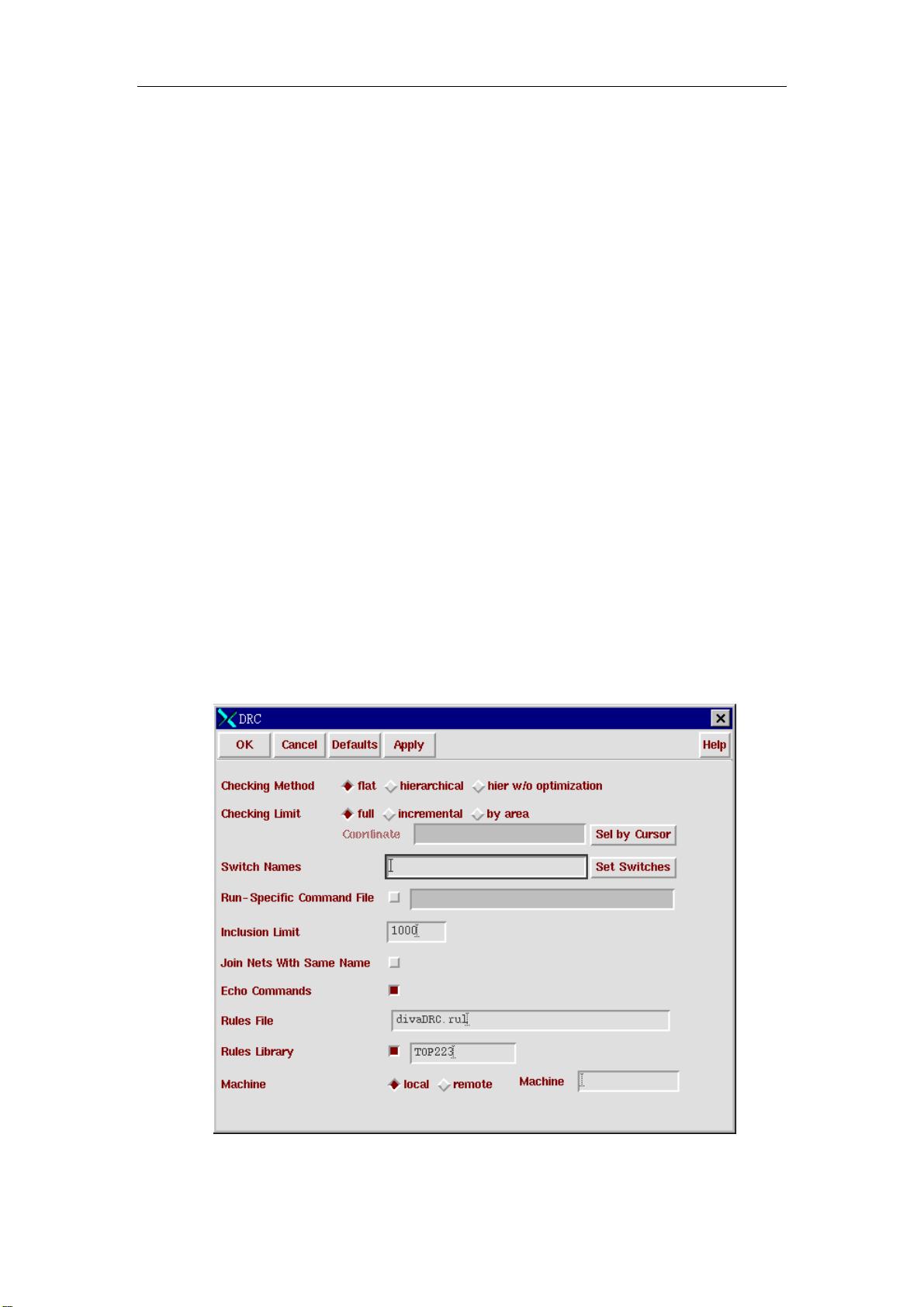

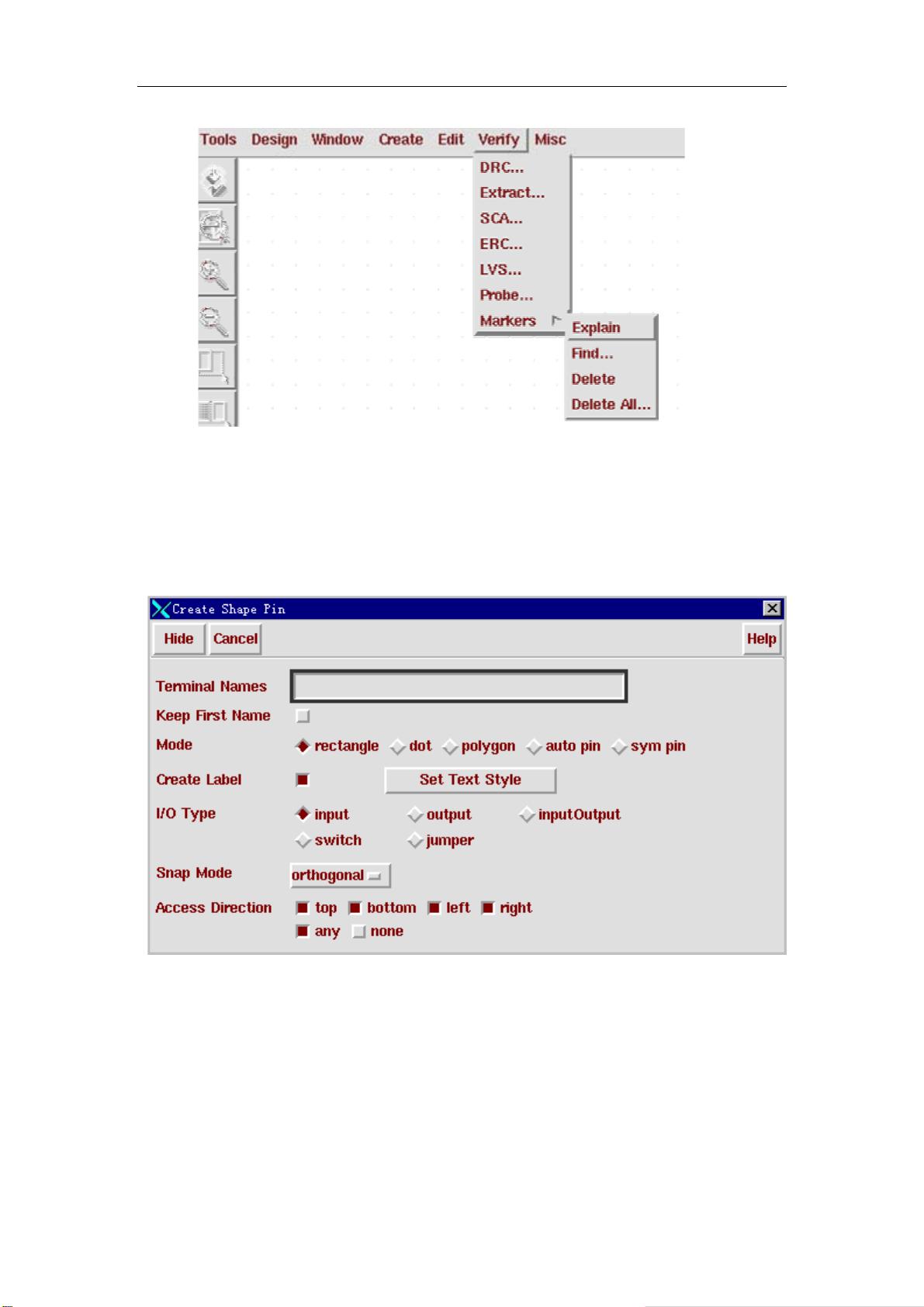

在实际操作中,用户会通过Iconmenu或menubanner来执行各种编辑任务,如绘制几何形状、添加导线、设置层属性等。绘制inverter掩膜版图的具体步骤包括定位元件、调整尺寸、连接引脚和线条,以及使用布局工具进行精细调整。这个过程可能涉及栅格对齐、DRC检查(Design Rule Checking,设计规则检查)和LVS(Layout Versus Schematic,版图与原理图一致性检查)等关键步骤,确保设计符合设计规则且功能正确。

Cadence版图设计通过Virtuoso提供的直观界面和丰富的功能,让设计师能够高效地创建、编辑和验证集成电路的物理实现。理解并掌握这些基础操作对于电子设计工程师来说至关重要,它涵盖了从设计概念到制造流程的各个环节。通过实际操作和反复练习,用户可以逐渐提升自己的版图设计技能。

2009-01-08 上传

332 浏览量

1064 浏览量

2308 浏览量

138 浏览量

477 浏览量