RISC-V指令集手册:特权架构详解

需积分: 0 72 浏览量

更新于2024-06-30

收藏 463KB PDF 举报

"这篇文档是RISC-V指令集手册的第二卷,专注于特权架构,版本1.7。由Andrew Waterman、Yunsup Lee、Rimas Avizienis、David A. Patterson和Krste Asanović等人撰写,来自加州大学伯克利分校的电气工程与计算机科学系。这份技术报告详细介绍了RISC-V架构中的机器中断寄存器(mip和mie)以及机器计时器寄存器。尽管这是一个草案,可能会在成为标准之前有所变化,但仍然提供了关于RISC-V架构的重要信息。"

在RISC-V架构中,机器中断寄存器(mip和mie)和机器计时器寄存器是特权模式下的关键组件,用于处理和管理系统的中断事件。这些组件对于构建高效、可靠的嵌入式和服务器系统至关重要。

1. **机器中断寄存器(mip和mie)**

- **mip**(Machine Interrupt Pending)寄存器:它存储了当前挂起的中断请求。每个位对应一个特定类型的中断,如果该位被设置,表示有对应的中断等待处理器响应。mip寄存器让处理器知道哪些中断源正在尝试引起中断,但并不决定是否允许它们发生。

- **mie**(Machine Interrupt Enable)寄存器:这个寄存器控制哪些中断被允许通过。当mie中的相应位置1时,对应的中断类型就被启用,如果同时mip中的对应位也被设置,则中断将被触发。反之,如果mie中的位为0,即使mip中有相应的中断请求,中断也不会被处理。

2. **机器计时器寄存器**

- RISC-V架构通常包含多个计时器,包括机器级计时器。这些计时器用于执行周期性任务,如定时唤醒、超时检测或者性能监控。机器计时器寄存器可能包括启动计时器、停止计时器或设置中断阈值的机制。

- 当机器计时器达到预设的计数值时,它们会向mip寄存器的相应位置发出中断请求。处理器通过检查mie寄存器来决定是否应对此中断。

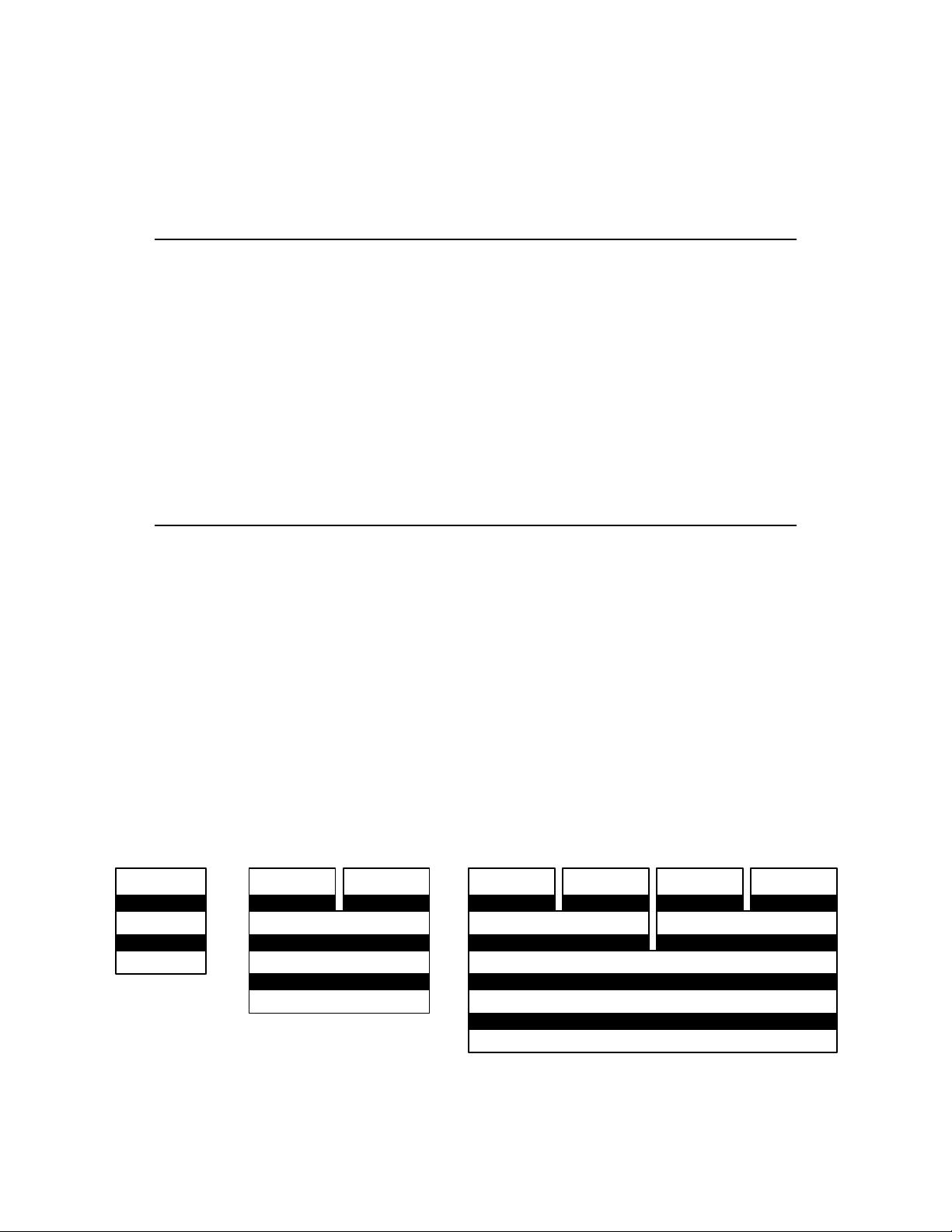

3. **特权级别和中断处理**

RISC-V架构支持多个特权级别,如Machine(M),Supervisor(S),User(U)等。在M级别,处理器可以访问和管理所有中断寄存器,控制整个系统的中断处理流程。在其他级别,中断处理受到更严格的限制,以确保系统的安全性和稳定性。

4. **中断处理流程**

- 中断发生时,处理器保存当前状态,如程序计数器和通用寄存器,然后切换到适当的中断处理程序地址。

- 处理器根据mie寄存器确定如何处理中断,如果允许,中断处理程序会被执行。

- 在处理完中断后,状态会被恢复,处理器返回到被打断的点继续执行原来的程序。

这个手册详细阐述了这些机制,对于理解和实现RISC-V处理器的中断系统以及系统级软件开发至关重要。由于这是草案版本,开发者需要注意未来可能出现的变更,以确保其设计与最终标准兼容。

2021-04-21 上传

2018-10-28 上传

2014-08-30 上传

2023-04-01 上传

2023-05-25 上传

2023-09-06 上传

2024-01-06 上传

2023-07-15 上传

2023-07-09 上传

df595420469

- 粉丝: 31

- 资源: 310

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析