SystemVerilog深度解析:功能验证实战指南

"SystemVerilog与功能验证.pdf"

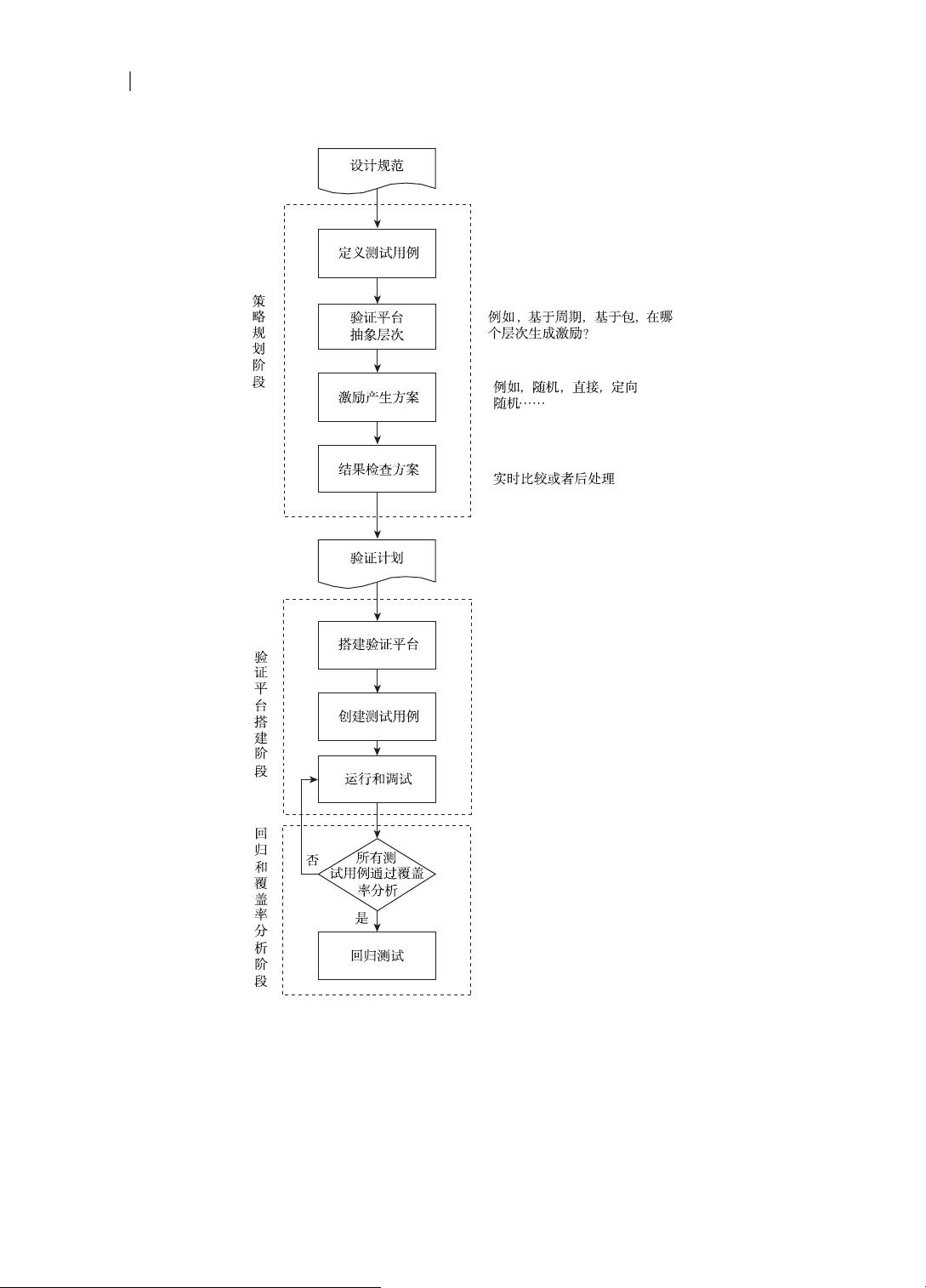

SystemVerilog是一种高级的硬件设计和验证语言,被广泛用于集成电路(IC)设计中的功能验证。这本书《SystemVerilog与功能验证》由钟文枫编著,深入浅出地介绍了SystemVerilog的基础语法以及它在功能验证中的应用。书中以功能验证为主线,探讨了验证流程、高级验证技术以及验证方法学。

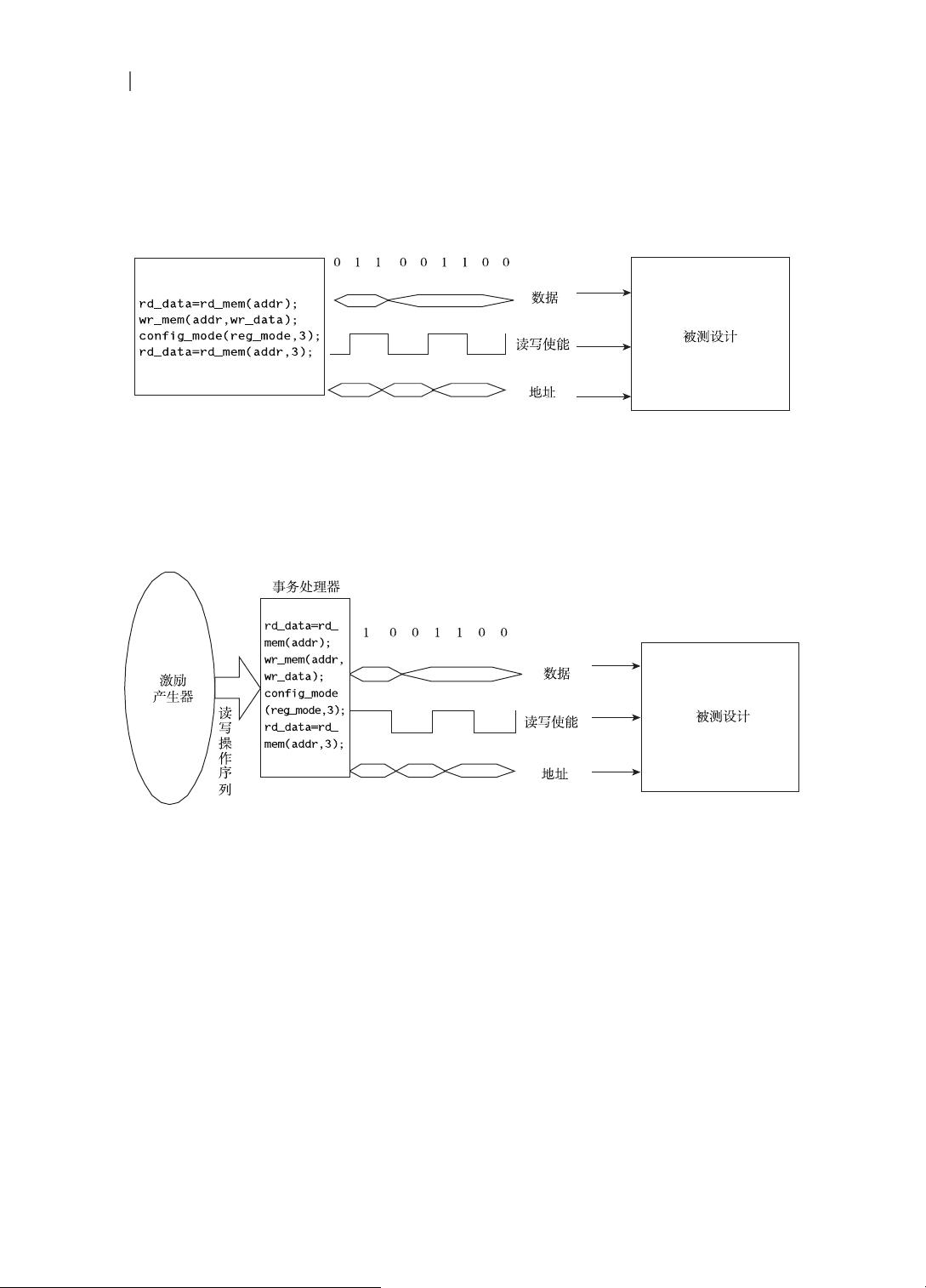

作者通过实例,如石头、剪刀、布的游戏,展示了如何利用SystemVerilog实现随机激励生成、功能覆盖率驱动验证和断言验证等高级验证技术。这些技术对于确保硬件设计的正确性和完整性至关重要。随机激励生成允许测试向量的自动生成,以覆盖各种可能的输入组合;功能覆盖率驱动验证则关注设计的各个功能区域是否得到充分测试;而断言验证则是通过声明预期的行为来确保设计满足预定规范。

此外,书中还涵盖了开放式验证方法学(OVM),这是一个基于SystemVerilog的验证框架,旨在提高验证环境的重用性和模块化。OVM允许开发者构建可扩展且高效的验证平台,从而提高验证效率和质量。

书中详细讨论了SystemVerilog的语法结构,包括类、接口、任务、函数、事件、队列等特性,这些都是在进行复杂功能验证时的关键工具。通过学习这些内容,读者能够理解和构建自己的验证环境,并有效地验证硬件设计。

该书特别适合电子工程、计算机科学以及集成电路设计领域的工程师和学生阅读。无论是对于初次接触SystemVerilog的初学者,还是寻求深入理解验证技术的专业人士,都能从中获得宝贵的知识和实践经验。

《SystemVerilog与功能验证》是一本全面介绍SystemVerilog验证技术的书籍,它涵盖了从基础到高级的主题,为读者提供了全面理解并掌握这一关键验证工具的路径。通过阅读此书,读者将能够更高效、更准确地验证他们的硬件设计,确保产品在实际应用中的可靠性。

3996 浏览量

2024-05-11 上传

817 浏览量

1007 浏览量

236 浏览量

410 浏览量