Vivado时序分析初学者指南

需积分: 50 87 浏览量

更新于2024-07-18

4

收藏 3.3MB PDF 举报

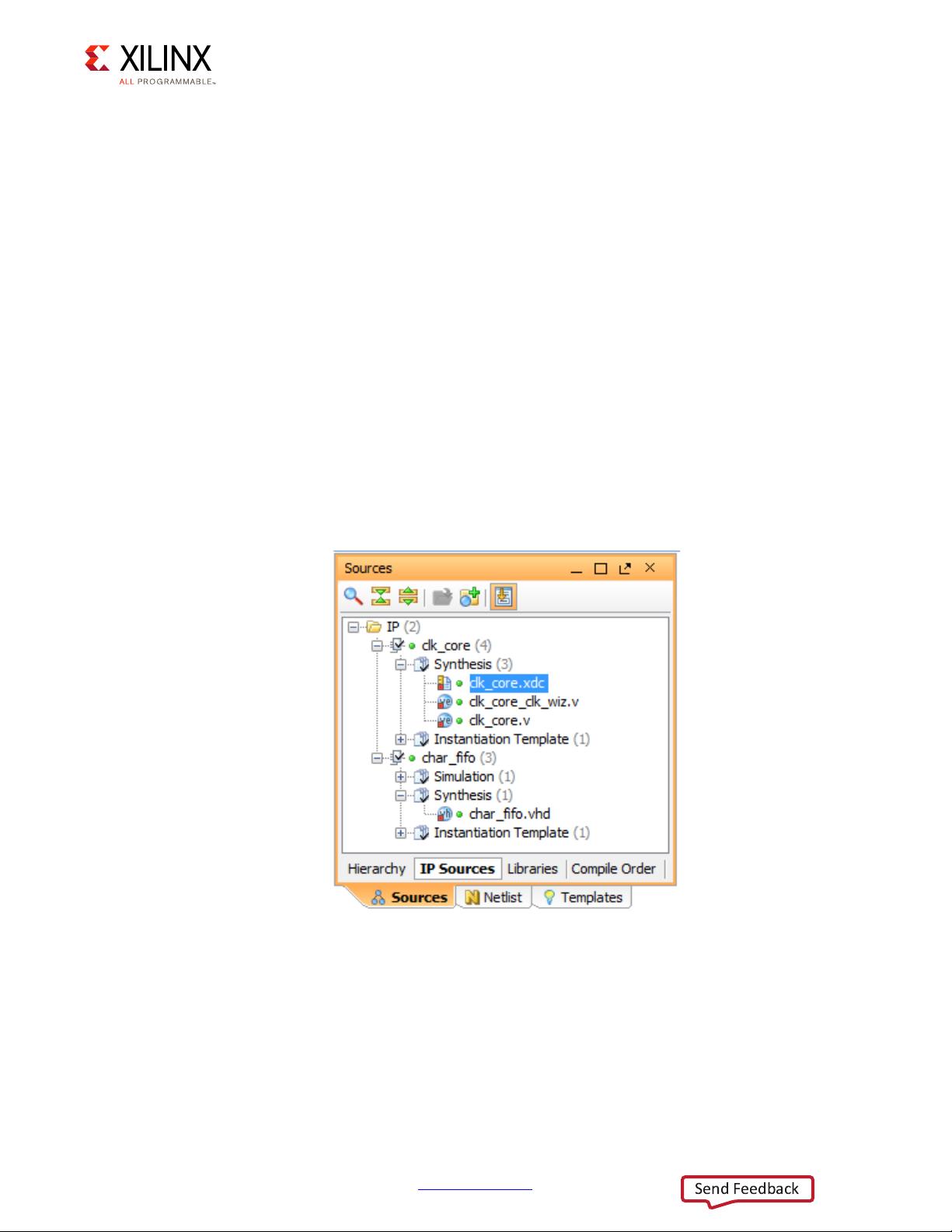

"Vivado时序菜鸟学习,涵盖了Vivado Design Suite 2014.3和2014.4版本的时序分析基础知识,适合初学者入门。文档包含修订历史,内容提要以及相关章节索引,旨在帮助工程师理解和应用时序约束。

在Vivado工具中,时序分析是FPGA设计的关键环节,它涉及到如何确保设计满足预定的性能目标,如最大时钟频率、最小延迟等。Vivado Design Suite提供了一套全面的工具和方法来管理和优化设计的时序。

时序分析主要关注以下几个方面:

1. **时钟约束**:定义设计中的时钟网络,包括时钟源、时钟路径和时钟域。时钟约束用于指定时钟信号的周期、偏移和关系,这对于计算逻辑单元的延迟至关重要。

2. **路径约束**:指定设计中关键路径的延迟限制,以确保设计能在规定的时间内完成操作。这可以是数据路径、控制路径或特定功能模块的路径。

3. **IO约束**:设定输入输出接口的电气特性,如摆率、电压电平和时序参数,以保证与外部设备的正确通信。

4. **同步化约束**:定义数据传输和信号同步的规则,防止数据竞争和 metastability问题。

5. **功耗约束**:通过设定功耗预算和电压水平来优化设计的功耗性能。

在Vivado 2014.3版本中,文档新增了关于禁用时序弧(Disabling Timing Arcs)的指导,这可能涉及到去除某些不需考虑的时序路径,以简化分析或优化特定区域的性能。此外,还添加了培训资源,提供进一步的学习材料。

文档的修订历史还提及在2014.1版本中加入了自动派生时钟限制的信息,这对理解工具如何处理自动生成的时钟约束非常重要。同时,更新了通过选项的节点列表,这有助于用户更精确地控制时序分析过程。

学习Vivado时序分析,工程师将能够有效地进行时序优化,确保设计的时序闭合,并提升整体设计的可靠性。这不仅对初学者有价值,也是经验丰富的开发者持续改进设计效率的重要参考。"

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-10-05 上传

2020-08-04 上传

2024-11-01 上传

点击了解资源详情

2024-12-28 上传

2024-12-28 上传

weixin_42169065

- 粉丝: 0

- 资源: 1

最新资源

- Accuinsight-1.0.4-py2.py3-none-any.whl.zip

- yama:Yama的编译器,一种面向对象的微控制器语言,例如ARM Cortex-M和AVR

- ap-event-lib:事件框架库

- 队列分析

- docker-compose2.172下载后拷贝到/usr/local/bin下

- webstore

- Employee-Summary

- media-source-demo:媒体源演示

- 家:普拉特姆学院

- LilSteve:第175章

- tilde-world

- Accuinsight-1.0.25-py2.py3-none-any.whl.zip

- 标题栏随着RecyclerView滚动背景渐变

- 浏览器自定义查看pdf文件.rar

- 直接序列扩频(DS SS):这是直接序列扩频的代码。-matlab开发

- flutter_dylinkios_sample:使用Dart的示例项目