Synopsys PCIe IP Core详细指南:架构与寄存器详解

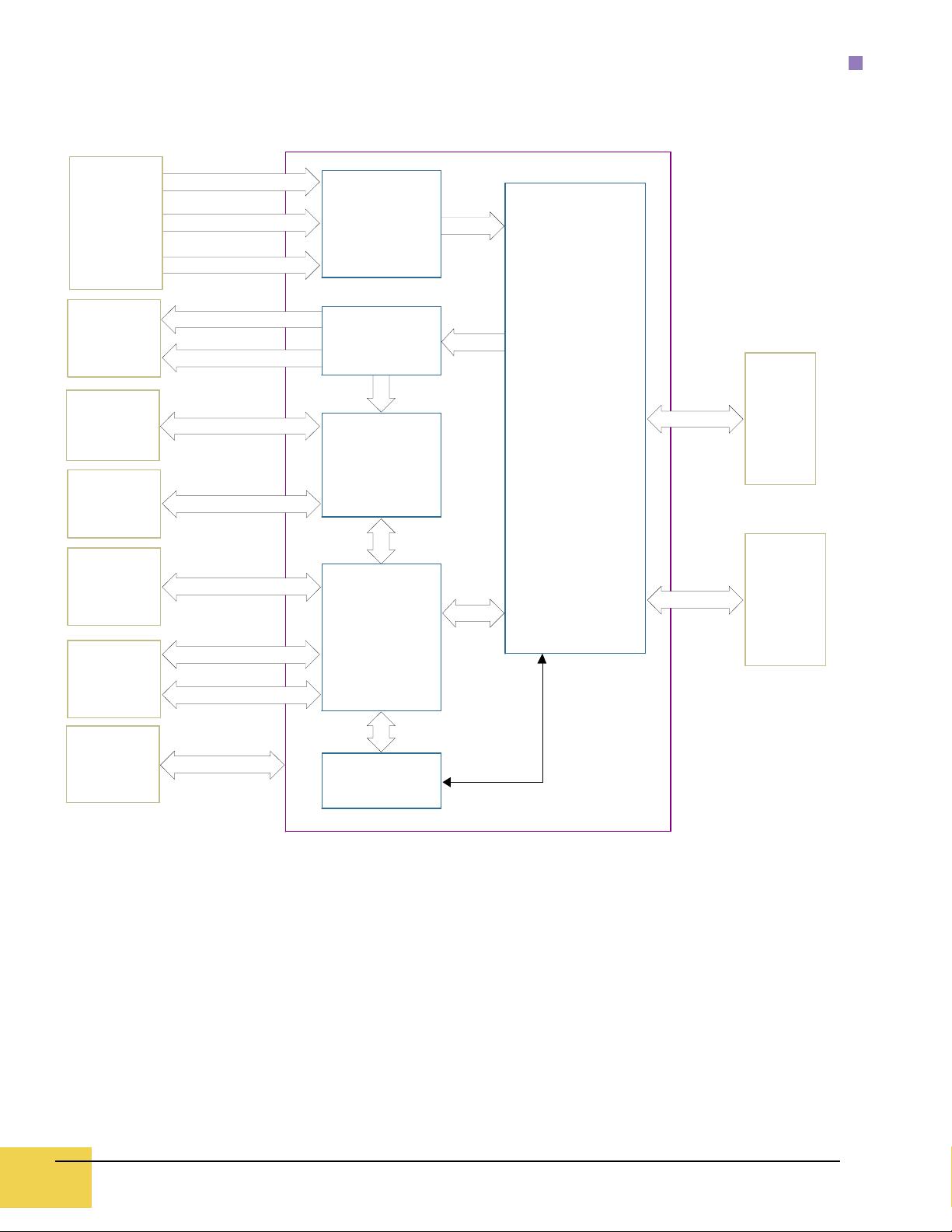

本篇文档是Synopsys公司关于PCIe IP Core(Peripheral Component Interconnect Express)的使用手册,适用于PCIe 3.00a版本的DesignWare Cores。文档详细介绍了PCIe技术中的四个核心组件:双模式(DM)核心、根复杂体(RC)核心、端点(EP)核心以及交换(SW)核心。这些IP核是设计者在高速串行接口标准PCIe中实现系统互连的关键组件。

1. **IP核组织**:

PCIe IP Core由这四个独立但协同工作的部分组成,每个核心负责不同的PCIe功能。DM Core处理PCIe的两种工作模式:Gen1和Gen2,而RC Core作为系统中的控制器,管理数据传输和配置,包括时序和同步控制。EP Core主要作为设备端的连接点,支持数据发送和接收,以及完成(Completion)处理。SW Core则作为桥接核心,用于内部数据包转发和外部端口间的通信。

2. **寄存器分配**:

文档中提及的"寄存器的分配"部分可能涉及各核心内部的不同寄存器,如状态机寄存器、配置寄存器等,它们用来控制和监控核心的工作状态、设置参数以及错误检测。这些寄存器的清晰定义和合理使用对于确保PCIe通信的正确性和效率至关重要。

3. **功能描述**:

- DM Core允许灵活切换PCIe Gen1和Gen2工作模式,满足不同应用场景的需求。

- RC Core提供初始化、配置管理和数据传输控制,通过配置命令来调整数据速率、错误校验和其他功能。

- EP Core负责接收和发送数据,执行事务,并与物理层进行交互,处理中断和完成信号。

- SW Core作为交换器,处理多个端口之间的数据交换,确保数据流的高效传输。

4. **版权和保密信息**:

该手册受版权保护,所有内容都受Synopsys公司拥有。未经授权,用户不得复制、传播或翻译文档内容,除非符合许可协议的条款。此外,还提到了美国出口管制法律,强调了技术数据的保密性和合规性要求。

5. **许可证协议**:

用户必须遵守Synopsys提供的许可证协议,才能合法地使用这些PCIe IP Core,这可能涉及到对软件和文档的使用限制、复制条件以及可能的额外服务和支持。

总结来说,这篇使用手册为设计者提供了PCIe IP Core的深入理解,包括其架构、功能细节以及使用过程中需要注意的版权和法规问题。它在指导工程师如何有效地集成这些IP核以构建高性能、兼容的PCIe系统方面扮演了关键角色。

484 浏览量

241 浏览量

163 浏览量

989 浏览量

912 浏览量

2504 浏览量

203 浏览量

2504 浏览量

zzg207

- 粉丝: 1

- 资源: 7

最新资源

- college-app:大学应用

- Jekyll静态站点生成器 v3.4.4

- -UofTSCS_DA_BC_2020_21_PyBer_Analysis:忽略此错误名称数据Bootcamp模块5使用Matplotlib进行PyBer分析

- 2016年东华理工大学各学科考研试题真题.rar

- Multi Class SVM:使用二进制svm分类开发的多类SVM-matlab开发

- Projects

- dgist-artiv.github.io:ARTIV技术博客-源码

- 51单片机c源码交通灯测试51单片机c源码交通灯测试

- 玻璃储物瓶3D模型

- ionic HTML5 移动应用框架 v3.4.2

- easywaiter-admin :(管理员和管理员)Aplicação网站,EasyWaiter项目,Desenvolvida com Angular para o Trabalho deConclusãode Curso

- UnityAnnotation:Unity与Android交互接口自动管理工具

- YandexTransportWebdriverAPI-Python:用于 Yandex Transport 的 Python“某种 API”,可与 YandexTransportProxy 一起使用

- ljudlabyrinten

- Molyx论坛 初恋夏天

- 密码可变的键盘门锁-项目开发