内部时钟驱动的差分延迟线ADC在DC/DC变换器中的应用

25 浏览量

更新于2024-09-04

收藏 203KB PDF 举报

"一种DC/DC变换器中差分延迟线ADC的实现"

本文主要探讨了一种创新的差分延迟线ADC(Analog-to-Digital Converter)设计,该设计特别适用于DC/DC变换器的数字控制领域。这种ADC的独特之处在于其无需外部时钟,能自我生成控制信号,同时具备高速转换率和低功耗特性,这使得它在高频数字DC/DC控制芯片的应用中显得尤为适用。

在传统的DC/DC变换器中,通常采用模拟控制方式,虽然这种方式在体积和功耗上具有优势,但容易受到噪声的干扰。数字控制的DC/DC变换器则克服了这一缺点,对工艺参数和环境变化不敏感,可以通过编程实现控制算法,更易于集成,并且可以缩短产品开发周期。

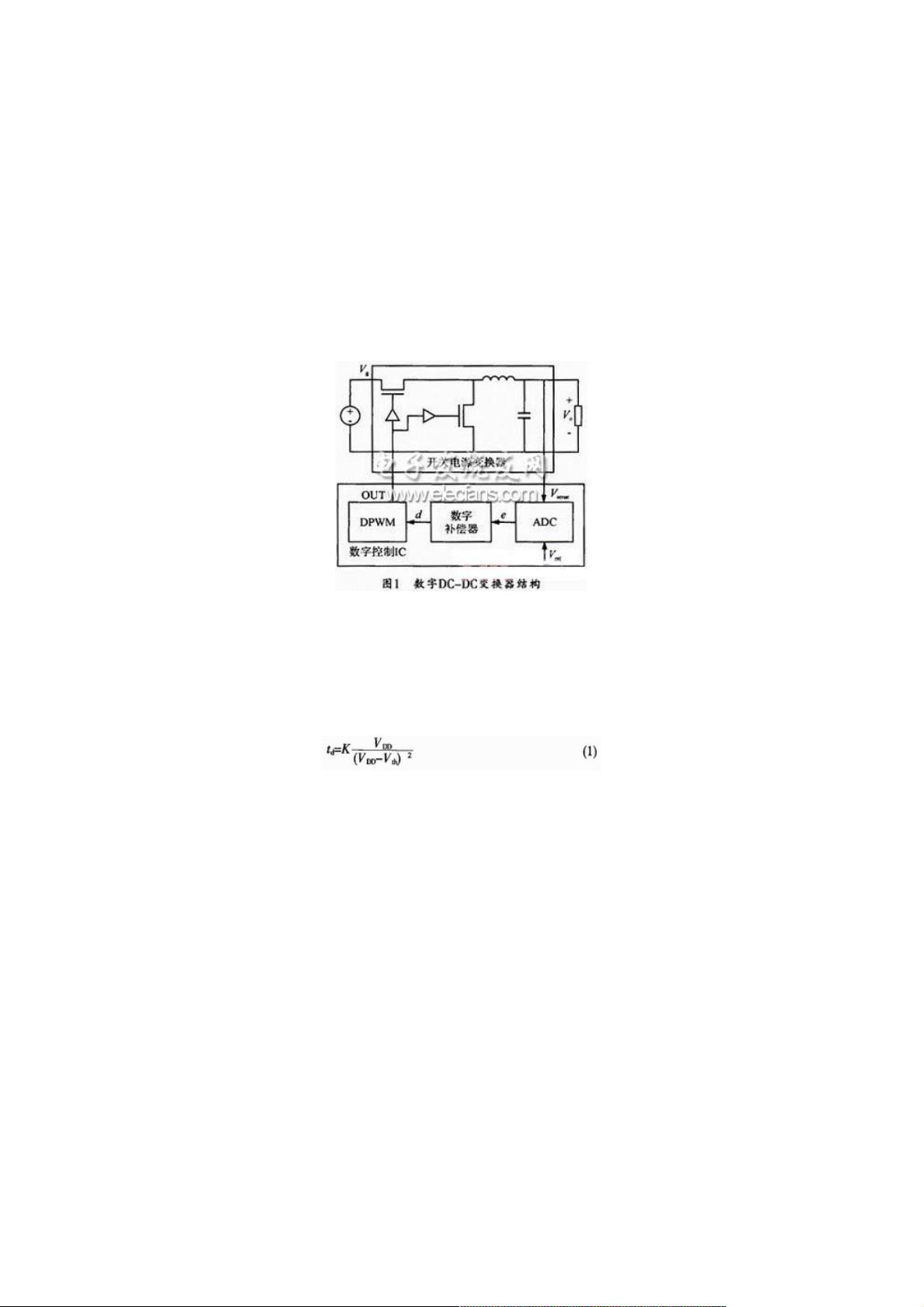

DC/DC变换器的数字控制系统由ADC、数字补偿器和数字脉冲宽度调制器(DPWM)组成。ADC负责将主电路的输出电压与基准电压进行比较并转化为数字误差信号;数字补偿器依据误差信号进行补偿,产生给定的数字信号;DPWM将这个数字信号转化为控制主电路开关通断的时间信号。

延迟线ADC是这种数字控制器的关键组件,由延迟链、寄存器组和译码电路构成。延迟链由一系列延迟单元串联,每个延迟单元由反相器和或非门组成。延迟时间td与电源电压VDD呈反比,这在标准CMOS工艺中是通过逻辑门延迟td = K/VDD - Vth来体现的,其中K和Vth分别为工艺相关的常数和MOS器件的阈值电压。

差分延迟线ADC的设计进一步优化了基本延迟线ADC,通过引入差分结构,可以抵消部分工艺偏差,提高ADC的稳定性和精度。在采样过程中,延迟时间td的长短对应于输入电压的大小,通过译码电路将延迟链的输出转换为二进制码,从而确定输入电压的数值。

在0.13微米CMOS工艺下进行的仿真结果显示,该差分延迟线ADC在0.7至1.5伏的采样电压范围内,输出无明显偏移,线性度表现良好,这证明了其在实际应用中的高效性和可靠性。

这种差分延迟线ADC的实现为DC/DC变换器的数字控制提供了一个高效、低功耗的解决方案,有助于提升变换器的性能,降低对外部环境因素的敏感性,同时简化了系统设计,增加了系统的鲁棒性。

486 浏览量

108 浏览量

点击了解资源详情

2020-10-21 上传

129 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38675341

- 粉丝: 8

- 资源: 998