SystemVerilog基础与组合逻辑电路设计

下载需积分: 0 | PDF格式 | 4.19MB |

更新于2024-07-01

| 198 浏览量 | 举报

"本章主要探讨了基于硬件描述语言(HDL)的组合逻辑电路模块设计,特别是使用SystemVerilog进行数字逻辑电路建模的方法。内容涵盖了数字逻辑电路设计的传统方法,现代设计方法的演进,以及电子设计自动化工具(EDA)在优化电路设计中的作用。章节还详细介绍了SystemVerilog的基础知识,包括其起源、综合与仿真的过程、程序基本结构和语法要素。此外,还特别提到了使用SystemVerilog设计常见组合逻辑电路模块和逻辑阵列的实践应用。"

在数字逻辑电路设计中,传统的设计方法主要包括真值表化简、布尔代数和卡诺图等手工方法。这些方法虽然在小规模电路设计中可行,但面临效率低下、容易出错且不适应大规模集成电路(如VLSI)设计的挑战。随着科技的进步,现代数字电路设计转向了更抽象的描述方式,结合计算机辅助设计(CAD)工具,实现自动化优化,这就是硬件描述语言(HDL)和电子设计自动化工具(EDA)的应用。

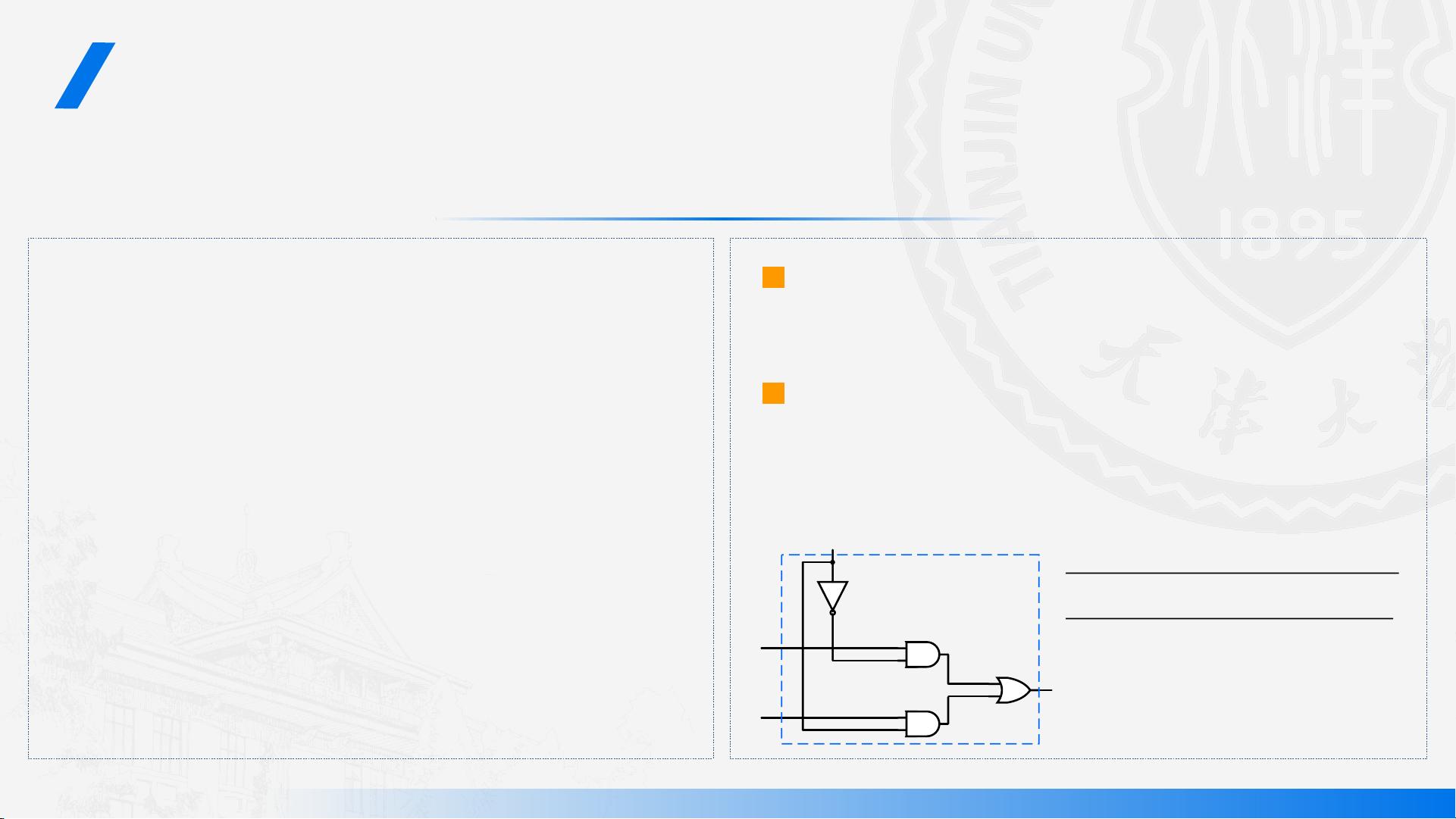

SystemVerilog是当前广泛使用的HDL之一,它为硬件设计提供了强大的表达能力和灵活性。SystemVerilog的基础包括理解其作为高级编程语言的特性,如如何描述硬件的结构和行为,以及如何进行综合和仿真以验证设计的正确性。综合是将高级语言描述转换为门级网表的过程,而仿真则是通过模拟电路行为来检查设计功能的正确性。

SystemVerilog的程序基本结构通常包含模块定义、接口、类、任务和函数等元素,而其语法要素则涵盖数据类型、运算符、控制结构和并发语句等。学习和掌握这些基础知识对于进行高效、可靠的数字逻辑电路设计至关重要。

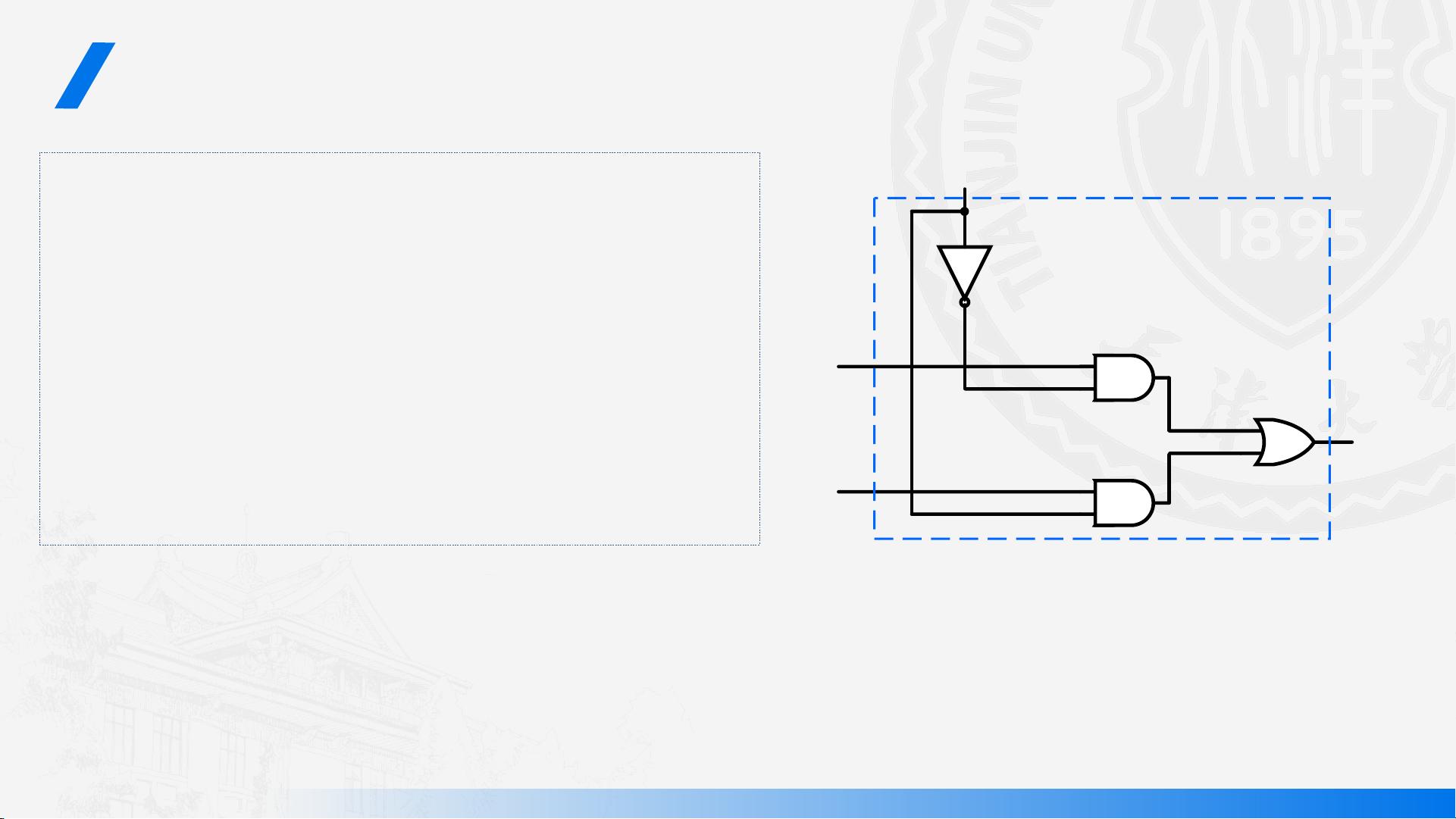

在实际应用中,使用SystemVerilog可以设计各种常见的组合逻辑电路模块,如加法器、编码器、译码器和多路选择器等。逻辑阵列,如查找表(LUT)和可编程逻辑阵列(PLA),也是通过SystemVerilog进行描述和实现的重要组成部分。

本章内容深入浅出地介绍了基于硬件描述语言的数字逻辑电路设计方法,旨在帮助读者理解和掌握使用SystemVerilog进行现代数字系统设计的关键技术和实践步骤。通过学习这些知识,工程师们能够更加高效、准确地设计复杂的数字逻辑电路,同时利用自动化工具减少错误和提高设计质量。

相关推荐

FloritaScarlett

- 粉丝: 28

最新资源

- Java平台下的MySQL数据库连接器使用指南

- Android开发:IconEditText实现图标与输入框结合

- Node.js结合TI Sensortag通过socket.io发布数据到HTML

- Flutter入门指南:MDC-100系列代码实验室

- MyBatisPlus生成器使用教程与文件解压指南

- 深入浅出BaseAdapter的传统实现方法

- C语言学习资料包:编程代码与实践指南

- Android图片处理SDK核心功能及工具类介绍

- Pebble平台上的同步番茄钟应用开发

- Elan Smart Pad驱动卸载指南及触摸板问题解决

- Activiti流程演示Demo:独立Web应用的实践指南

- 快速飞行动效设计:彩带跟随与购物车动画

- 高校收费管理系统:全面管理学生收费情况

- Toucan库:定义和检索Clojure应用程序模型

- ActiveAndroid ORM框架在Android中的实践演示

- rjs-jade:将Jade整合至RequireJS环境的插件