华为同步电路设计规范:提升FPGA稳定性与分析策略

需积分: 9 199 浏览量

更新于2024-08-01

收藏 437KB PDF 举报

华为同步电路设计规范强调了在可编程逻辑器件(如FPGA)设计中采用同步电路的重要性,以提高电路工作的稳定性和可靠性。该规范涵盖了以下几个关键知识点:

1. 设计可靠性:明确指出,为增强电路稳定性,设计者应遵循严格的同步电路设计规范,尽可能避免异步电路的使用。对于保留的异步电路,必须提供充分的理由,并对其工作可靠性进行详尽分析,包括检查时钟信号质量(如无毛刺)、建立-保持时间是否达到标准,确保满足性能指标。

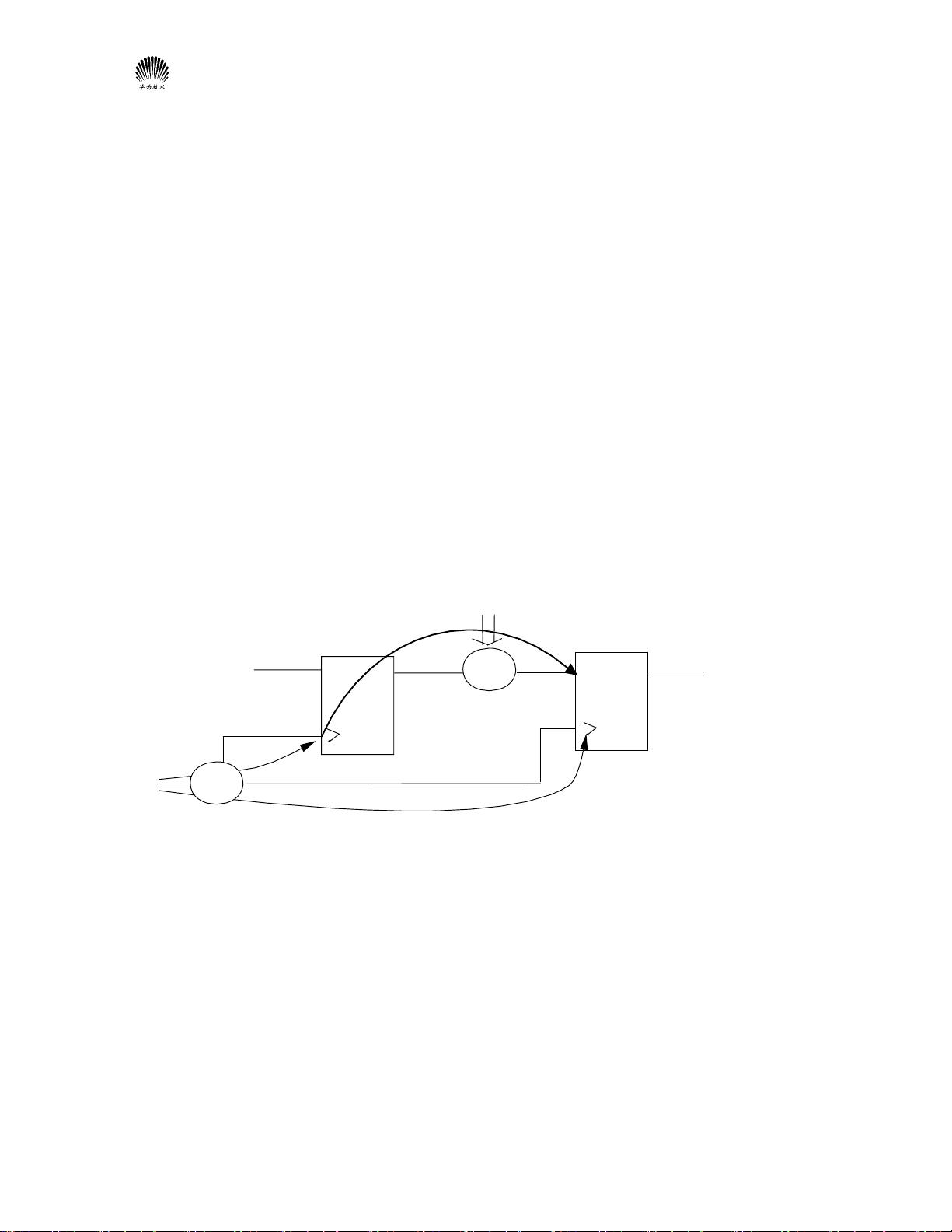

2. 时序分析基础:时序设计是电路设计的核心挑战,涉及触发器的建立时间和保持时间满足。例如,图1.1展示了两个触发器REG1和REG2之间的逻辑关系,通过计算不同路径(如路径①和②)的时间延迟(T1和T2),确保信号在规定时间内正确传递。

3. 同步电路设计规则:同步电路设计具有优越性,如更好的定时、同步控制和易于调试。设计规则可能包括时钟树优化、数据同步机制、以及信号线布局策略等。

4. 异步设计问题与解决:针对异步设计中可能出现的问题,如时钟抖动、竞争冒险等,给出了相应的解决策略,帮助设计师避免潜在的不稳定因素。

5. SET和RESET信号处理:这些控制信号的正确处理对同步电路至关重要,规范可能规定了如何确保它们的正确分配和有效同步。

6. 时延电路处理:针对电路中的延迟元件,如何减小时延并保证信号完整性和正确性是重要内容。

7. 全局信号处理:处理那些影响整个电路行为的全局信号,要求精确控制和管理,以维护整体系统的时序一致性。

8. 时序设计保障措施:提供了确保时序可靠性的具体方法,可能包括设计约束设置、仿真验证和实际测试。

9. ALTERA参考设计准则:可能引用了ALTERA这类厂商的官方设计指南,作为设计同步电路的参考,以充分利用硬件平台特性。

华为同步电路设计规范是一份实用的指南,为FPGA工程师提供了一套系统的方法来提升电路设计的质量和稳定性,通过遵循规范,可以有效避免设计错误,提高设计效率和产品的可靠性。

209 浏览量

153 浏览量

点击了解资源详情

点击了解资源详情

134 浏览量

106 浏览量

131 浏览量

openmp_hn

- 粉丝: 2

- 资源: 1

最新资源

- PJBlog2 qihh

- TodoRestApi:待办事项其余应用程序的服务器端

- spread:SPREAD 移动前景中的所有图形并尝试以愉快的方式排列它们。-matlab开发

- SeleniumDemo:Selenium自动化框架模板

- For-While

- kaggle dataset: publicassistance-数据集

- PHPWind论坛 prettyshow

- multitranslator

- 使用CNN的OCR韩语辅助应用程序

- SwiftUI仿表格效果完成代码

- Impermalink:用于创建缩短的,即将到期的链接的工具

- anime-sync

- Arduino-基于Web的MP3播放器-项目开发

- 预算跟踪器:使用503020方法的简单预算跟踪器

- TITUNI:Tituni - 标题程序。 还在测试中。-matlab开发

- BBSxp论坛 蓝语风格