UHF RFID基带接收端电路设计提升性能

115 浏览量

更新于2024-08-30

收藏 643KB PDF 举报

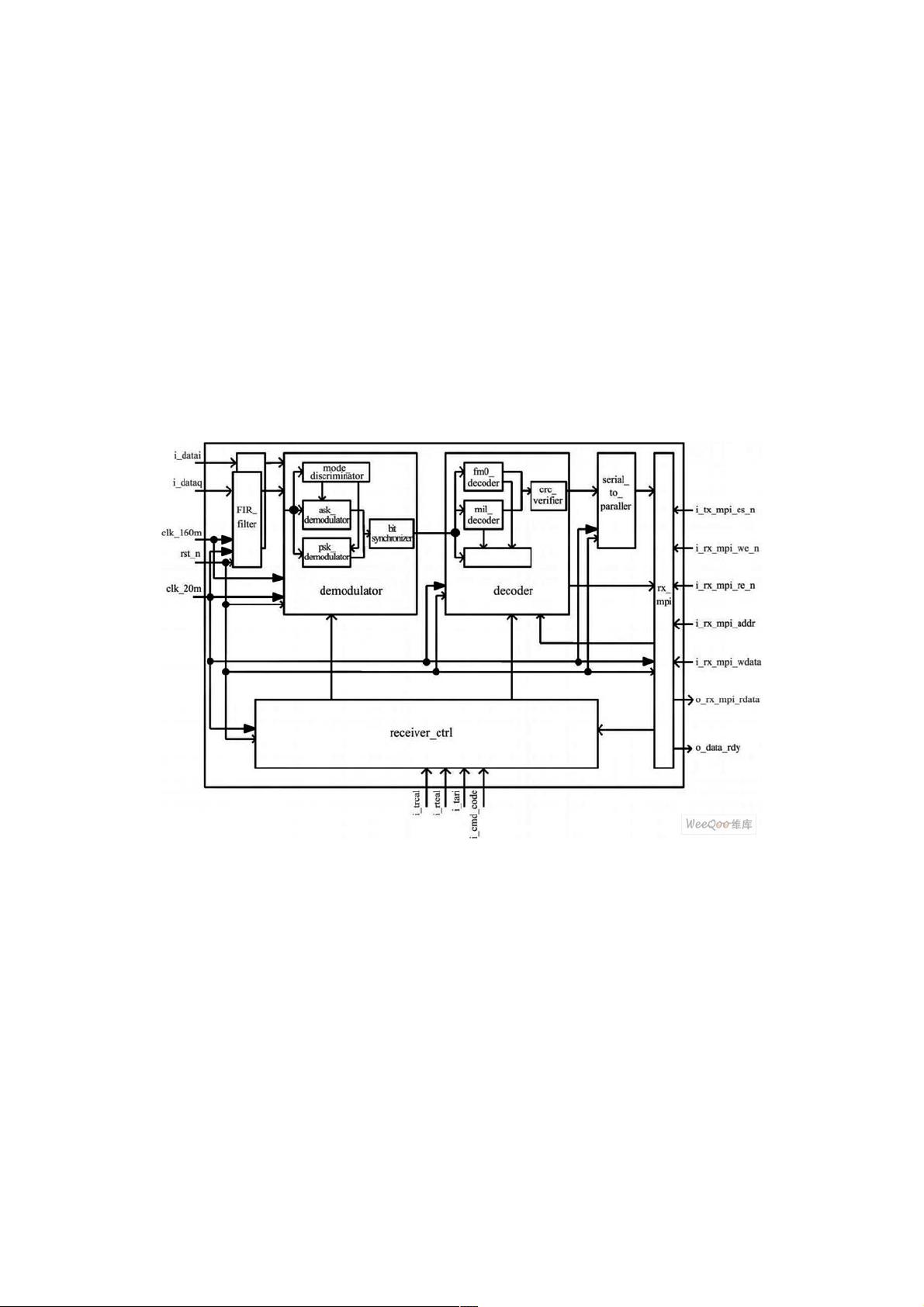

UHF RFID阅读器基带处理接收端电路的设计是一篇深入研究的文章,主要探讨了在UHF (Ultra High Frequency) RFID系统中,如何利用IQ两路正交调制解调的零中频技术来优化基带信号处理。文章的核心内容围绕以下几个关键部分展开:

1. **电路设计背景**:

UHF RFID技术因其广泛应用性,如物流管理、资产追踪等,对阅读器的可靠性和效率有极高的要求。基带处理芯片作为阅读器的核心组件,它负责接收来自电子标签的信号,并进行解调和解码,提供信号处理解决方案。

2. **电路结构与模块**:

设计者构建了包含输入基带低通滤波器、解调器(如混频器和解相器)、解码器、串并转换模块、信息传递接口(MPI)以及接收机控制模块的完整接收端电路。其中,低通滤波器用于清除噪声,确保后续环节能准确处理信号;解调器则负责从射频信号中提取出IQ调制的基带信息。

3. **关键技术改进**:

文章强调了在物理层数据编码和调制方式上的改进,这直接关系到信号的抗干扰能力和数据传输速率。通过优化这些技术,设计者成功提升了接收端电路的性能。

4. **IQ正交调制与零中频**:

IQ两路正交调制解调技术的应用使得信号处理更为高效,零中频方案有助于减少信号失真和噪声影响,从而增强系统的整体性能。

5. **射频前端与接收流程**:

射频前端负责信号的上变频和功率放大,电子标签回应的信号经过接收、放大、滤波和下变频后,被送入基带处理芯片,进一步解析和处理。

6. **集成与应用**:

该电路设计考虑了与基带处理发送端和CPU的集成,以实现整个基带处理芯片的功能,满足UHF RFID系统的需求,并符合ISO/IEC18000-6C协议的要求。

这篇文章详细介绍了UHF RFID阅读器基带处理接收端电路的结构、工作原理及其在实际应用中的改进策略,对于理解RFID技术的信号处理流程和芯片设计具有重要参考价值。

141 浏览量

点击了解资源详情

233 浏览量

141 浏览量

2021-05-09 上传

189 浏览量

2020-07-31 上传

177 浏览量

点击了解资源详情

夏影影

- 粉丝: 317

最新资源

- 深入解析JavaWeb中Servlet、Jsp与JDBC技术

- 粒子滤波在视频目标跟踪中的应用与MATLAB实现

- ISTQB ISEB基础级认证考试BH0-010题库解析

- 深入探讨HTML技术在hundeakademie中的应用

- Delphi实现EXE/DLL文件PE头修改技术

- 光线追踪:探索反射与折射模型的奥秘

- 构建http接口以返回json格式,使用SpringMVC+MyBatis+Oracle

- 文件驱动程序示例:实现缓存区读写操作

- JavaScript顶盒技术开发与应用

- 掌握PLSQL: 从语法到数据库对象的全面解析

- MP4v2在iOS平台上的应用与编译指南

- 探索Chrome与Google Cardboard的WebGL基础VR实验

- Windows平台下的IOMeter性能测试工具使用指南

- 激光切割板材表面质量研究综述

- 西门子200编程电缆PPI驱动程序下载及使用指南

- Pablo的编程笔记与机器学习项目探索