UHF RFID阅读器基带处理接收端电路的创新设计与优化

151 浏览量

更新于2024-09-01

收藏 470KB PDF 举报

模拟技术中的UHF RFID阅读器基带处理接收端电路的设计是一项关键的技术,它针对UHF (Ultra High Frequency) RFID系统的需求,特别是在高频RFID应用中,如库存管理、物流追踪和门禁控制等。这项设计的核心目标是提高接收端的性能和可靠性,以确保高效的数据通信。

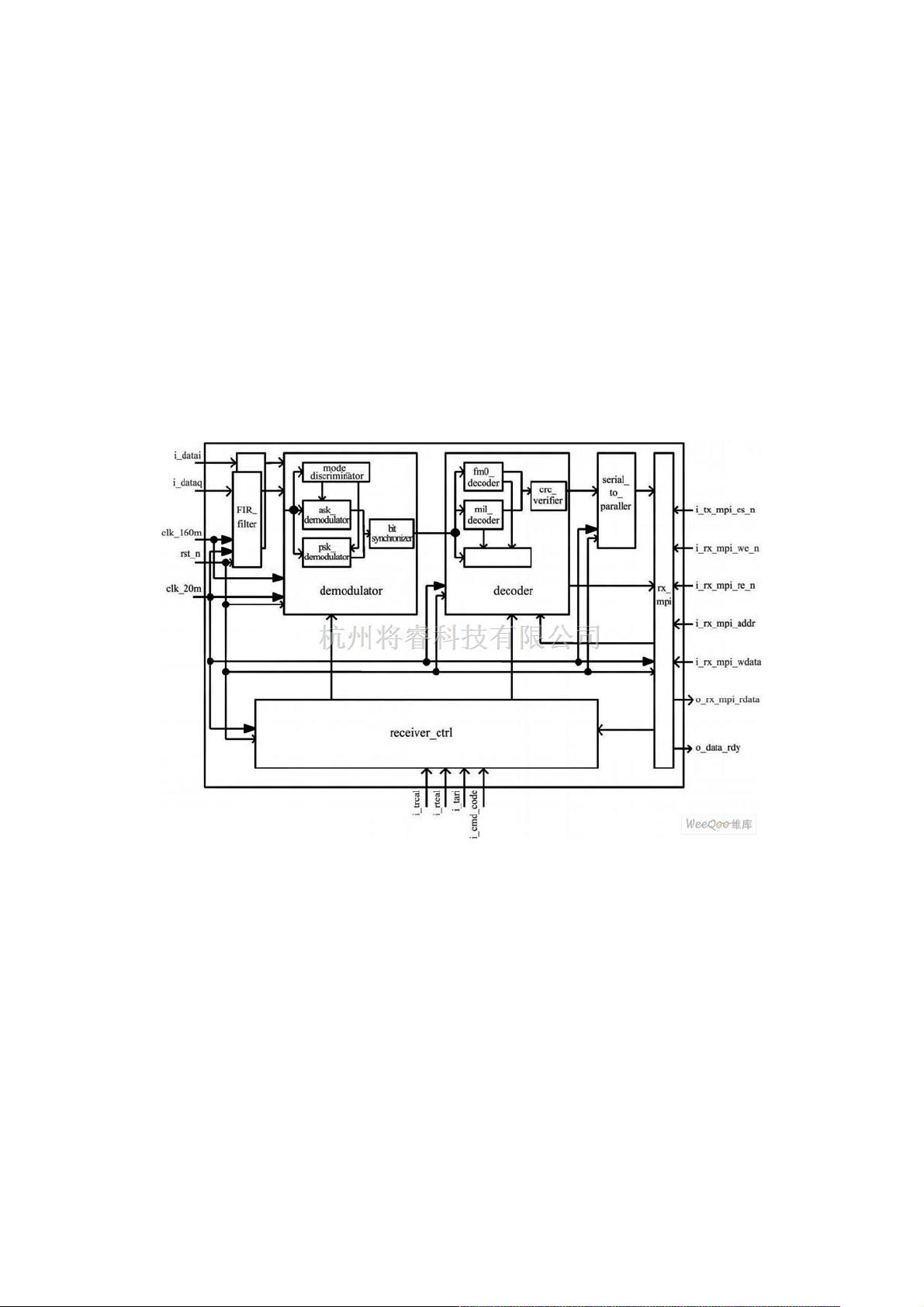

该设计采用IQ两路正交调制解调的零中频方案,这是一种高效的数据传输技术,能够减少噪声干扰并提高信号质量。在电路实现上,主要包括以下几个关键模块:

1. 电路总体结构:电路由射频前端和基带处理两大部分组成。射频前端负责将基带信号上变频并进行功率放大,确保信号可以有效地发送到电子标签。电子标签接收后,基带信号再通过下变频和滤波,将信号传输回接收端。

2. 解调器与解码器:解调器是接收端的核心组件,它接收返回的调制信号,并将其转换回原始的基带信号。解码器则进一步处理这些信号,去除可能的错误或噪声,以便CPU能准确解读。

3. 数据串并转换模块:将接收到的并行数据转换为CPU可处理的串行形式,简化了后续的数据处理流程。

4. 信息传递接口(MPI):这个模块负责数据的交换和控制信号的传输,确保基带处理芯片与外部系统之间的顺畅通信。

5. 接收机控制模块:负责整个接收过程的控制,包括启动、停止和调整接收参数,以适应不同环境和应用场景。

设计过程中,对物理层数据编码、调制方式进行了优化,以提升系统的抗干扰能力和传输效率。通过RTL设计( Register Transfer Level,即门级描述)和FPGA原型验证,确保了电路的正确性和性能指标。

UHF RFID阅读器基带处理接收端电路的设计是一项系统性工作,涉及多个关键技术环节的集成和优化。它的成功实现对于推动UHF RFID技术在工业、物流、零售等多个领域的广泛应用具有重要意义。随着技术的发展,未来的基带处理芯片可能会更加集成化和高效,以满足日益增长的物联网需求。

172 浏览量

145 浏览量

2021-05-09 上传

145 浏览量

点击了解资源详情

178 浏览量

2020-07-31 上传

点击了解资源详情

376 浏览量

2025-01-13 上传

weixin_38688855

- 粉丝: 0

最新资源

- 3D大数据轮播界面设计与特效实现

- 钢制材料计算工具:Swift版的应用开发

- 粘性标头库简短版本介绍与应用

- React项目开发指南:从启动到部署

- MATLAB实现准循环LDPC码编码快速算法

- 数据库技术与应用实践

- 前端大师Brian Holt讲授的计算机科学完整入门课程

- Minitab中文版: 统计分析与机器学习软件介绍

- 披萨查找神器:通过pizza-finder-js筛选披萨菜单

- 基于51单片机的LED自动调光系统实现

- 前端源码:仿360浮动小插件效果实现与多领域资源分享

- MATLAB开发工具DCTOOL:分布式计算网络状态监控

- trash-cleaner:利用关键字和标签过滤技术有效清除垃圾邮件

- 重现Scratch插件分号错误-crxt文件分析

- Swift实现弹性过渡视图动画源码分享

- 开放式图表网站解析器:从内容到URL全面解析