FPGA开发板PLL配置全解析

"PLL配置详细指南,适用于SF-EP1C FPGA开发板,通过Quartus II软件进行配置,旨在帮助初学者理解如何创建和设置PLL以产生所需时钟频率。"

PLL(Phase-Locked Loop)是一种电子系统,广泛应用于数字电路中,用于频率合成、倍频、分频以及时钟恢复等任务。在FPGA设计中,PLL是不可或缺的一部分,因为它可以生成不同频率的时钟信号,满足不同模块的时序需求。

在SF-EP1C FPGA开发板上配置PLL,首先需要确保有一个新工程,并明确PLL的需求。例如,本例中要求输入时钟为25MHz的晶振,期望得到50MHz的系统时钟,这相当于2倍频。PLL的接口包括输入时钟(inclk0)、复位信号(areset)、输出时钟(c0)和锁定信号(locked)。

配置PLL的步骤如下:

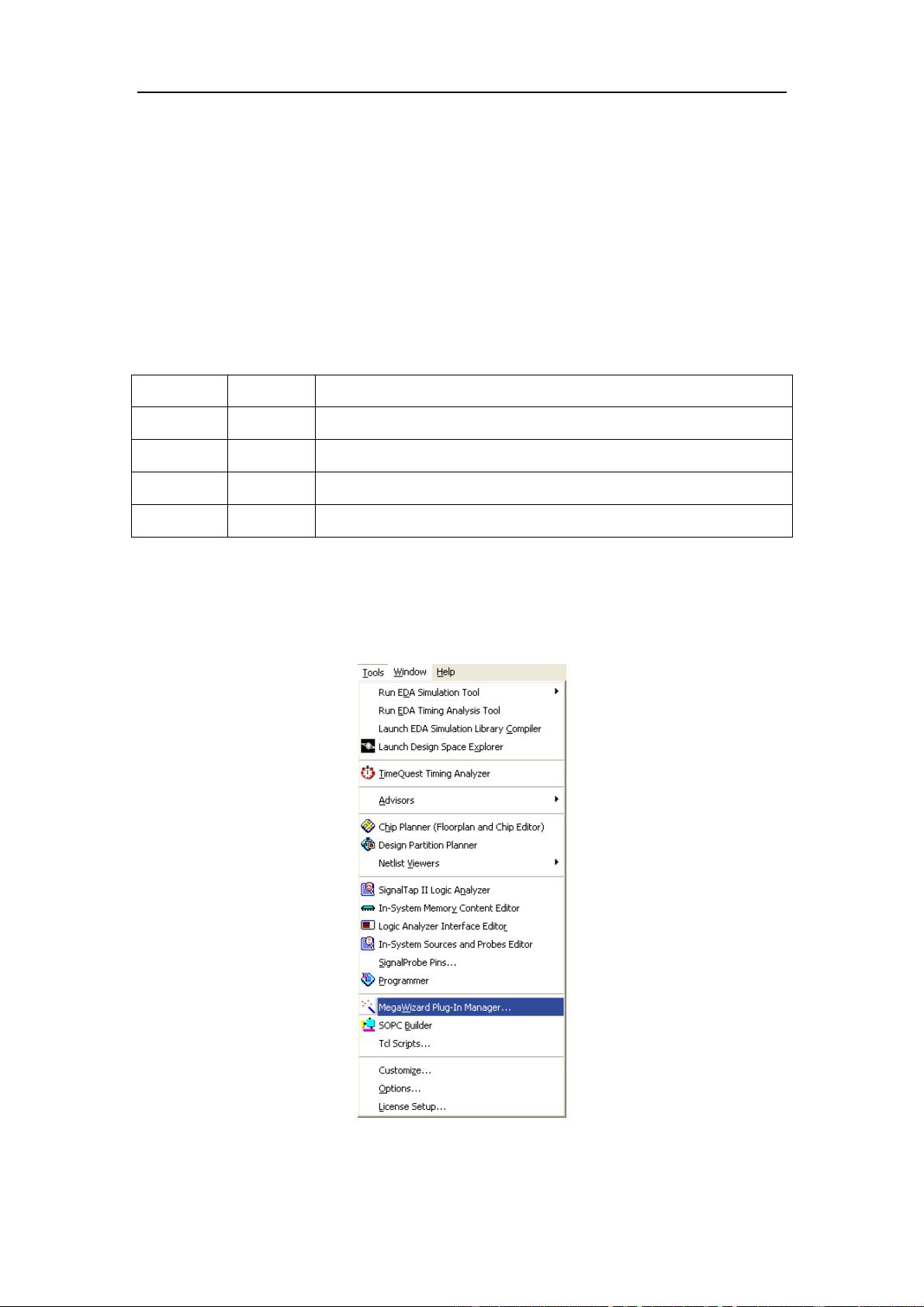

1. 打开Quartus II,通过“Tools—> MegaWizard Plug-In Manager…”启动MegaWizard向导。

2. 选择“Create a new custom megafunction variation”,点击“Next>”。

3. 在下拉框中选择“I/O”下的“ALTPLL”作为PLL内核,选择“Verilog HDL”作为输出文件的语言,指定PLL实例名为“PLL_ctrl”。

4. 根据工程所用器件的速度等级选择合适的“Which device speed grade will you be using?”,并输入输入时钟频率(例如25MHz)。

5. 在“Options input”中勾选“Create an ‘areset’ input”,以便为PLL添加复位信号。

完成以上步骤后,向导将自动生成PLL的Verilog代码,该代码可直接在工程中实例化并进行综合。在综合和下载到FPGA后,PLL会根据设定的参数工作,产生所需的50MHz系统时钟。同时,locked信号会表示PLL是否已锁定,即输出时钟是否稳定。

在实际应用中,PLL的配置还包括对输出分频比、相位偏移、带宽和噪声性能等方面的调整,以优化系统的时钟质量和功耗。对于不同的FPGA器件,PLL的具体配置选项可能会有所不同,因此在设计过程中应参考具体器件的数据手册和软件的用户指南。

理解并熟练掌握PLL配置是FPGA设计的关键技能之一,它能够帮助设计者灵活地生成各种时钟频率,满足复杂系统的需求。通过实践和学习,开发者可以进一步优化PLL的设置,实现更高效、更稳定的FPGA设计。

107 浏览量

201 浏览量

181 浏览量

108 浏览量

107 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

1556 浏览量

smail_fly

- 粉丝: 0

- 资源: 4

最新资源

- torch_cluster-1.5.6-cp36-cp36m-linux_x86_64whl.zip

- D-无人机:拉无人机。 使用计算机视觉在喷漆墙上画画以实现精确导航

- myloader

- Metro_Jiu-Jitsu-crx插件

- 导航条,鼠标悬停滑动下拉二级导航菜单

- 中国企业文化理念:提炼与实施的流程及方法(第一天课程大纲)

- 使用videojs/aliplayer 实现rtmp流的直播播放

- irt_parameter_estimation:基于项目响应理论(IRT)的物流项目特征曲线(ICC)的参数估计例程

- visualvm_21.rar

- torch_sparse-0.6.4-cp38-cp38-linux_x86_64whl.zip

- redratel:数字代理

- JumpStart!-开源

- api-2

- Adoptrs-crx插件

- redis windows x64安装包msi格式的

- XX轧钢企业文化诊断报告