FPGA开发板PLL配置指南

需积分: 49 177 浏览量

更新于2024-09-15

收藏 664KB PDF 举报

“PLL配置详细说明,适用于SF-EP1C FPGA开发板的实验,通过Quartus II软件配置ALTPLL,生成50MHz系统时钟。”

PLL(Phase-Locked Loop,相位锁定环路)是一种重要的时钟发生器,常用于数字电路中,特别是FPGA(Field-Programmable Gate Array)设计中,用于产生不同频率的时钟信号。本说明将详细介绍如何在Quartus II环境下配置PLL,以实现从25MHz输入时钟生成50MHz的系统时钟。

首先,PLL的配置需求是基于SF-EP1C FPGA开发板,它有一个25MHz的外部晶振作为PLL的输入时钟源。目标是生成这个输入时钟的2倍频,即50MHz,供FPGA内部使用。PLL的接口包括:`inclk0`作为输入时钟,`areset`作为复位信号,`c0`作为输出时钟,以及`locked`作为PLL锁相状态指示。

配置PLL的步骤如下:

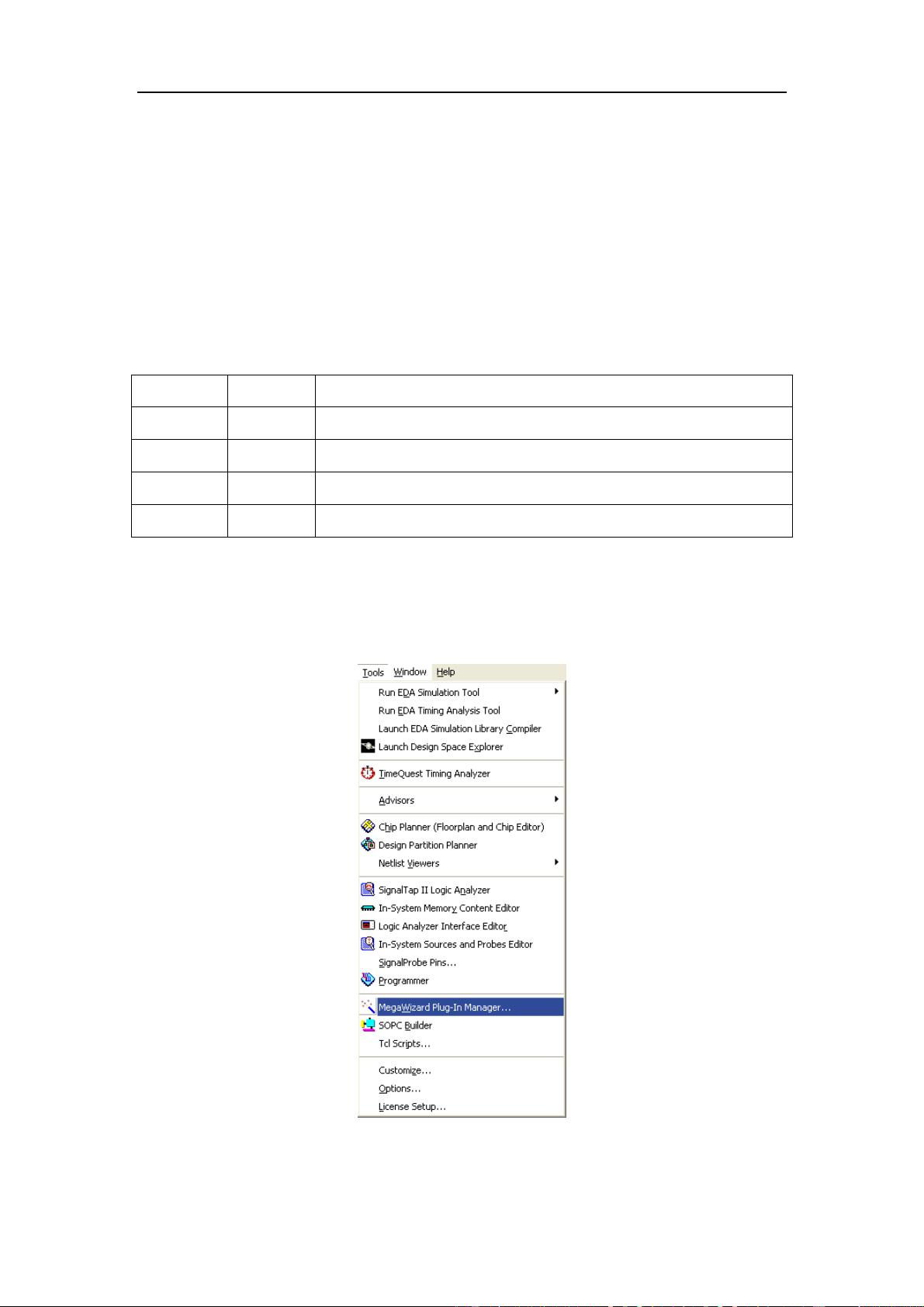

1. 打开Quartus II软件,通过“Tools—>MegaWizard Plug-In Manager…”启动MegaWizard向导。

2. 选择“Create a new custom megafunction variation”,并点击“Next>”。

3. 在选择megafunction的列表中,从“I/O”下拉框中选择“ALTPLL”。接着,选择“Verilog HDL”作为输出文件的语言,并在“Output file name”中输入PLL实例的名称,例如“PLL_ctrl”。

4. 在输入时钟配置界面,选择对应的器件速度等级,输入PLL的输入时钟频率(25MHz)。

5. 在“Options input”部分,勾选“Create an ‘areset’ input”,创建一个复位输入。

继续配置PLL:

6. 在“Clock Outputs”部分,设置所需的输出时钟。在本例中,我们需要一个倍频输出,因此选择“Multiply”选项,将输入时钟乘以2,得到50MHz的输出时钟`c0`。

7. “Additional Outputs”可以用来配置辅助输出,如分频时钟,如果不需要,可以保持默认设置。

8. 在“Advanced”选项中,根据具体应用的需求调整PLL的锁定范围、抖动性能等参数。

9. 完成配置后,点击“Finish”生成PLL的Verilog代码,并将其添加到工程中。

10. 在顶层模块中例化PLL_ctrl,连接输入时钟`inclk0`、复位信号`areset`和输出时钟`c0`,以及`locked`信号到你的设计中,以监控PLL是否已锁定并稳定工作。

在FPGA设计中,正确配置PLL至关重要,因为它直接影响到系统的时序性能和稳定性。遵循上述步骤,开发者能够为SF-EP1C FPGA开发板生成所需的时钟频率,为后续的数字逻辑设计提供稳定的时钟源。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-05-23 上传

2021-05-25 上传

2021-05-19 上传

2012-10-03 上传

点击了解资源详情

2021-09-11 上传

gkillua35

- 粉丝: 0

- 资源: 1

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践