Altera FPGA时序分析实战:从基础到Timequest约束

"通向FPGA之路---七天玩转Altera之时序篇V1.0" 是一个针对初学者的教程,旨在帮助读者在一周内掌握Altera FPGA的时序设计、分析、验证和优化。教程内容涵盖时序分析的基础概念、公式、Altera器件的时序模型、基本单元、路径分析以及时序约束和优化策略。

在时序分析基本概念部分,教程介绍了同步逻辑时延模型,包括时钟抖动与偏斜的影响,以及建立时间、保持时间、恢复时间和移除时间的概念。这些是理解和分析数字系统时序性能的关键因素。建立时间是指数据必须在时钟边沿之前到达接收端,保持时间则指数据在时钟边沿之后必须保持稳定的时间。恢复时间和移除时间是时钟到数据的关系,用于确保在时序路径上的正确传输。

时序分析基本公式部分详细解释了如何检查这些时间参数,例如设置时间检查确保数据在时钟边沿前到达,保持时间检查确保数据在时钟边沿后保持稳定。此外,还讨论了多周期路径检查,允许在某些路径上放宽时序限制以提高设计性能。

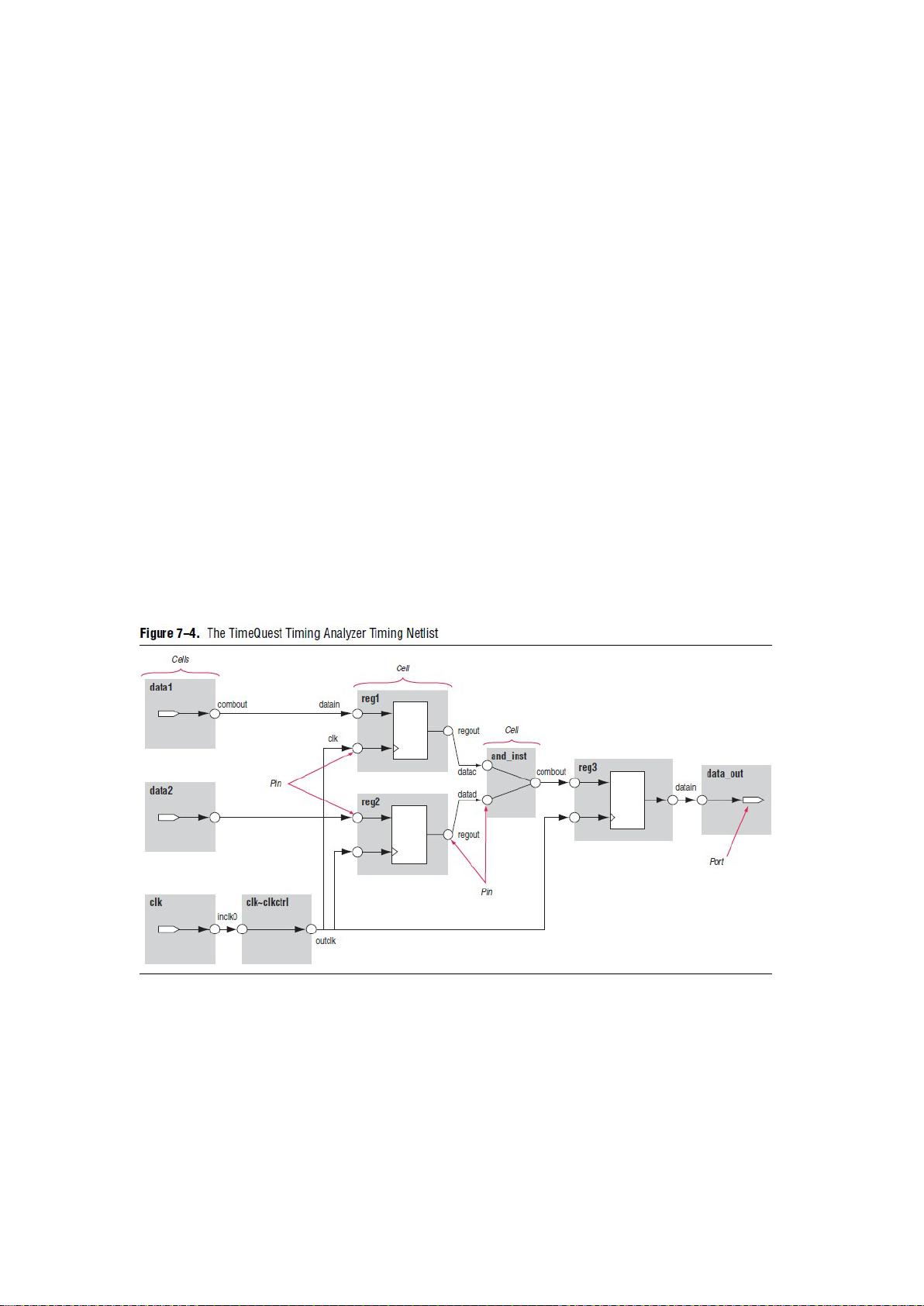

Altera器件的时序模型部分,教程将介绍FPGA内部结构对时序的影响,以及基本单元如查找表(LUTs)和触发器如何形成路径。关键路径与时序优化方法探讨了如何通过改变设计布局或利用特定的时序优化技术来改善系统性能。

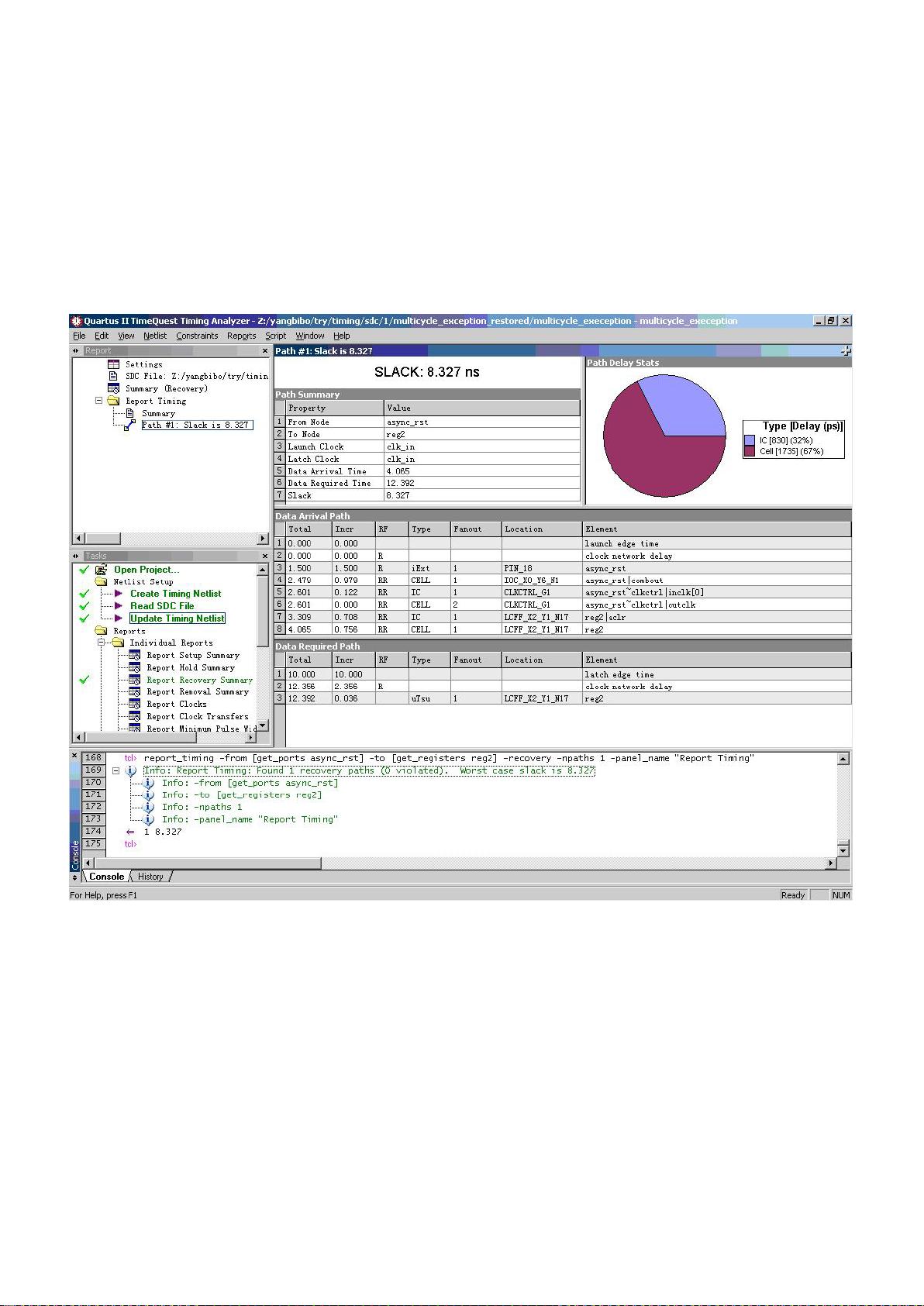

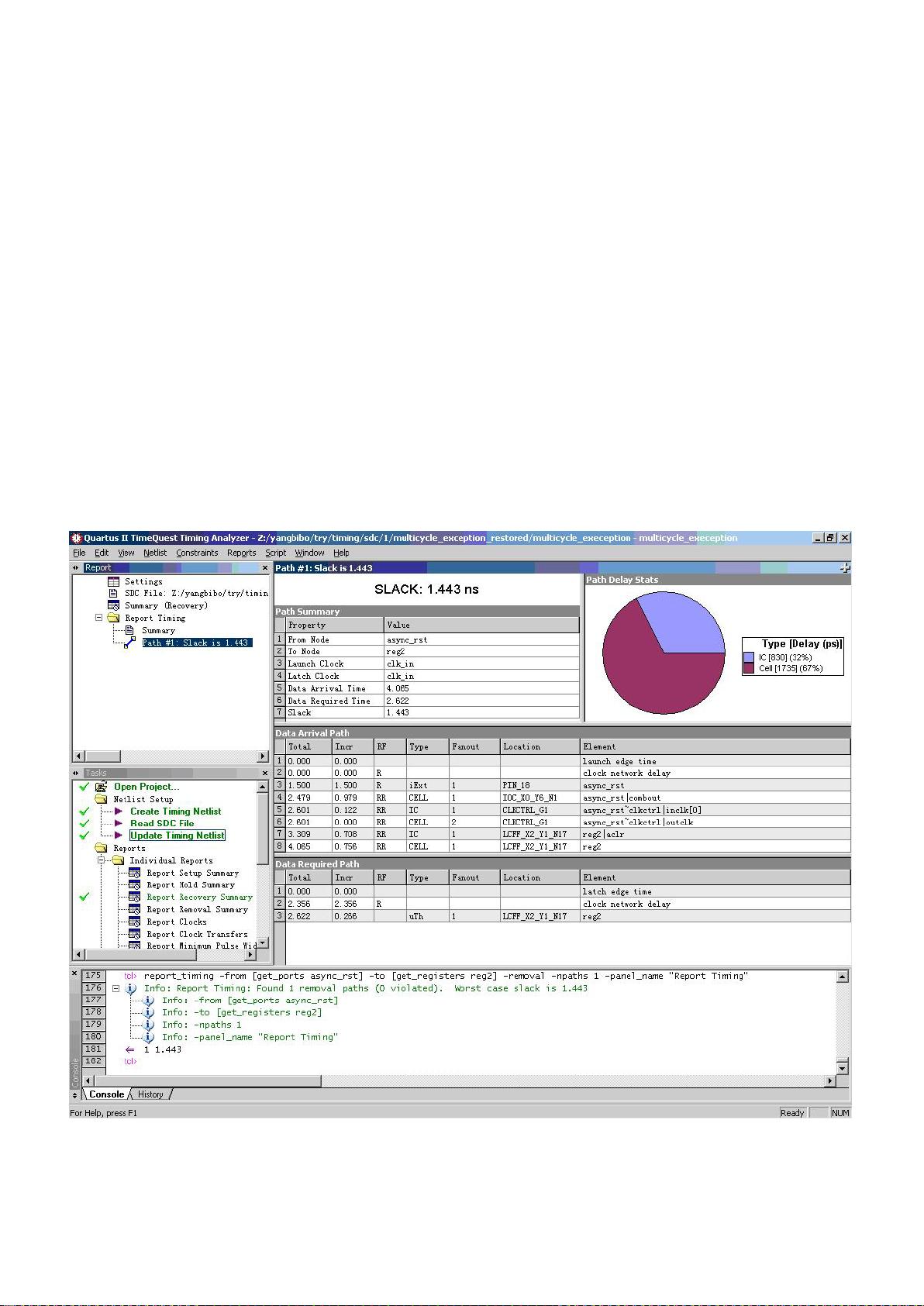

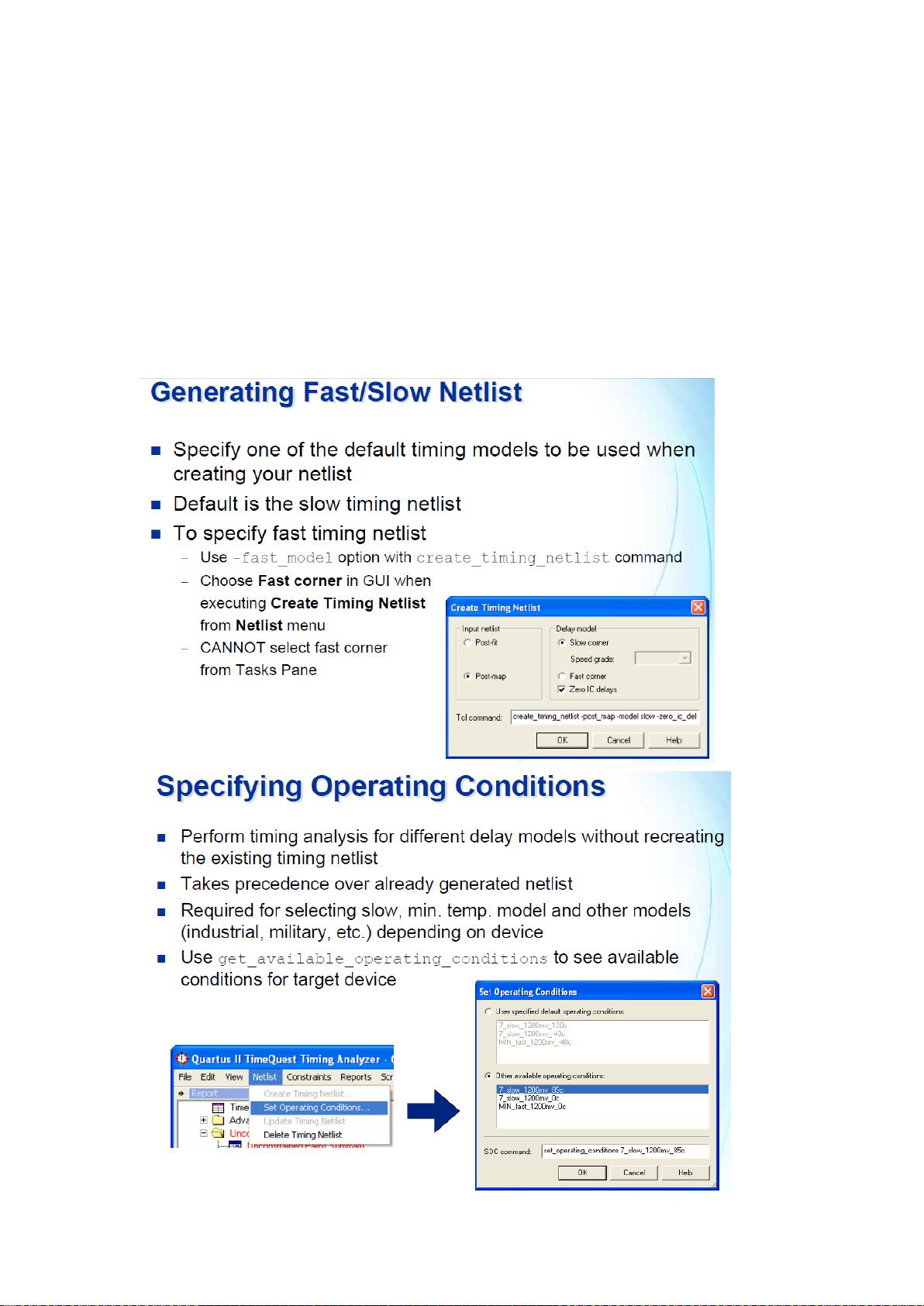

时序约束是FPGA设计中的重要环节,教程详述了几种约束方法,如对Tsu(建立时间余量)和Tco(传播时间余量)的简单约束,以及如何使用Timequest时序分析器进行更高级的约束设置。Timequest工具的使用包括时序约束的流程、图形用户界面(GUI)、时序波形图的解读,以及如何计算和调整时序余量。

在时序约束的深入讲解中,教程涵盖了时钟约束的各种方面,如创建时钟、生成时钟、PLL时钟、自动检测和创建时钟,以及默认约束、时钟延迟、时钟不确定性等。I/O约束部分则讨论了组合逻辑和同步I/O接口的时序考虑。

这个教程提供了FPGA时序设计的全面指导,不仅理论知识丰富,还包含了实际操作步骤,是学习和掌握Altera FPGA时序设计的重要资源。通过这个教程,读者可以深入了解时序分析的基本原理,以及如何在实际设计中应用这些知识以达到最优性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-04-22 上传

2021-10-14 上传

2012-02-22 上传

2012-08-16 上传

2014-06-01 上传

huangwujiong

- 粉丝: 0

- 资源: 2

最新资源

- SpringTest:测试一些弹簧功能

- matlab心线代码-EEG-ECG-Analysis:用于简单EEG/ECG数据分析的MATLAB程序

- Stack-C-language-code.rar_Windows编程_Visual_C++_

- 企业名称:Proyecto Reto 2,企业最终要求的软件,企业最终合同的最终目的是在埃塞俄比亚,而在埃塞俄比亚,企业管理者必须是西班牙企业,要求客户报名参加埃洛斯和埃塞俄比亚普埃登的征状,要求参加比赛的男子应征入伍

- bh前端

- scratch-blocks-mod

- hugo-bs-refreshing

- CRC16ForPHP:这是一个符合modbus协议的CRC16校验算法PHP代码的实现

- SnatchBox(CVE-2020-27935)是一个沙盒逃逸漏洞和漏洞,影响到版本10.15.x以下的macOS。-Swift开发

- dep-selector:使用Gecode的Ruby快速依赖解决方案

- clickrup:与R中的ClickUp v2 API交互

- FelCore

- react-markdown-previewer

- ch.rar_通讯编程_Others_

- 图片:允许您向应用提供高度优化的图片

- matlab心线代码-3DfaceHR:基于3D面部界标的基于视频的HR估计项目