基于WISHBONE总线的Am29LV160D FLASH接口设计

8 浏览量

更新于2024-09-01

1

收藏 173KB PDF 举报

"本文主要探讨了嵌入式系统/ARM技术中,如何基于WISHBONE总线设计一个与AMD公司Am29LV160D芯片兼容的FLASH闪存接口,包括接口设计的详细步骤和部分Verilog HDL程序源代码。"

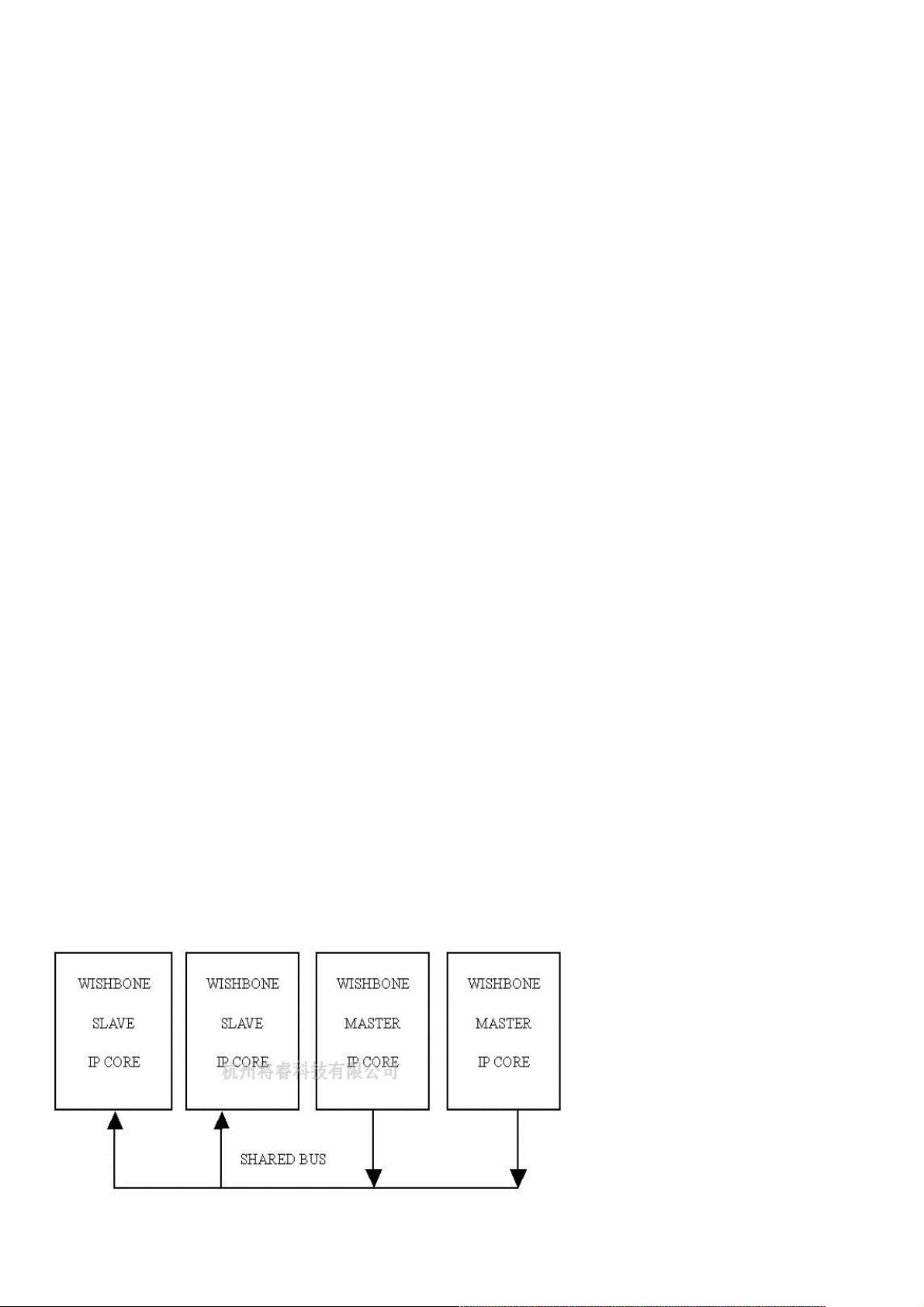

在嵌入式系统和ARM技术中,构建高效的存储解决方案至关重要。WISHBONE总线是一个开放标准的互连架构,广泛应用于片上系统(SoC)设计中,为各种IP核提供了通用的通信接口。本文针对的是在SoC设计中,如何利用WISHBONE总线与外部存储器,特别是闪存(FLASH MEMORY)进行交互。

AMD的Am29LV160D芯片是一种常见的非易失性存储器,具备大容量、低功耗和快速擦写能力,适合于需要频繁更新数据和存储关键信息的场合。相对于DRAM和SRAM,它无需持续刷新,且在断电后仍能保留数据,因此成为SoC设计的理想选择。

在设计过程中,首先需要理解Am29LV160D芯片的特性。该芯片支持电擦除和编程,允许独立的扇区擦写,具有较高的耐用性和可靠性。为了连接到使用WISHBONE总线的处理器(如Openrisc1200),必须设计一个适配的硬件接口。这个接口需要处理地址、数据和控制信号的转换,确保处理器能够正确地读写Am29LV160D。

接口设计通常涉及以下步骤:

1. **地址映射**:将WISHBONE总线的地址空间映射到Am29LV160D的地址空间,确保每个有效的总线地址对应到正确的闪存地址。

2. **数据传输**:实现数据线的连接,确保数据可以从处理器通过总线传输到闪存,反之亦然。

3. **控制信号**:处理读/写、使能、片选等控制信号,确保在正确的时间启动和结束操作。

4. **时序匹配**:由于处理器和闪存的时序可能不同,需要调整接口逻辑以适应两者之间的差异。

5. **错误处理**:添加必要的错误检测和恢复机制,如奇偶校验、ECC等。

在Verilog HDL编程中,这些设计概念会被转化为具体的逻辑门电路描述。通过编写模块来实现上述功能,然后在FPGA上进行仿真和验证,最后可以将验证通过的设计下载到实际的FPGA设备中,完成硬件接口的实现。

WISHBONE总线的使用使得接口设计具有可移植性,因为不同的处理器如果遵循WISHBONE规范,那么设计的接口可以轻松地应用于其他WISHBONE兼容的处理器,提高了设计的复用性和灵活性。

基于WISHBONE总线的FLASH闪存接口设计是嵌入式系统设计中的关键技术之一,它涉及到存储器特性的理解、总线协议的遵循以及硬件描述语言的编程技巧。通过这样的设计,可以有效地连接和管理外部存储资源,满足SoC系统对存储的需求。

点击了解资源详情

184 浏览量

681 浏览量

124 浏览量

184 浏览量

112 浏览量

111 浏览量

200 浏览量

184 浏览量

weixin_38711149

- 粉丝: 4

最新资源

- 普天身份证阅读器新版二次开发包发布

- C# 实现文件的数据库保存与导出操作

- CkEditor增强功能:轻松实现图片上传

- 掌握DLL注入技术:测试工具使用与探索

- 实现带节假日农历功能的jQuery日历选择器

- Spring循环依赖示例:深入理解与Git代码仓库实践

- ABB PLC液压阀门控制程序开发指南

- 揭秘4核旋风密版626象棋引擎的超牛实力

- HTML5实现的经典游戏:小霸王坦克大战源码分享

- 让Visual Studio兼容APM硬件信息的方法

- Kotlin入门:创建我的第一个应用

- Android语音识别技术研究报告与应用分析

- 掌握JavaScript基础:第8版教程源代码解析

- jQuery制作动态侧面浮动图片广告特效教程

- Android PinView仿支付宝密码输入框源码分析

- HTML5 Canvas制作的围住神经猫游戏源码分享