17

SN65DSI86

www.ti.com.cn

ZHCSBP5B –SEPTEMBER 2013–REVISED MARCH 2017

Copyright © 2013–2017, Texas Instruments Incorporated

Feature Description (continued)

(1) For case when DPPLL_CLK_SRC = 1, the SN65DSI86 will update the CHA_DSI_CLK_RANGE and CHB_DSI_CLK_RANGE with a

value that represents the selected DSI clock frequency. Software can change this value.

(2) REFCLK pin must be tied or pull-down to GND when the DACP/N is used as the clock source for the DPPLL.

(3) If GPIO selection of REFCLK or DACP/N frequency is not used, then software must program the REFCLK_FREQ,

CHA_DSI_CLK_RANGE and CHB_DSI_CLK_RANGE through the I

2

C interface prior to issuing any DSI commands or packets to the

SN65DSI86.

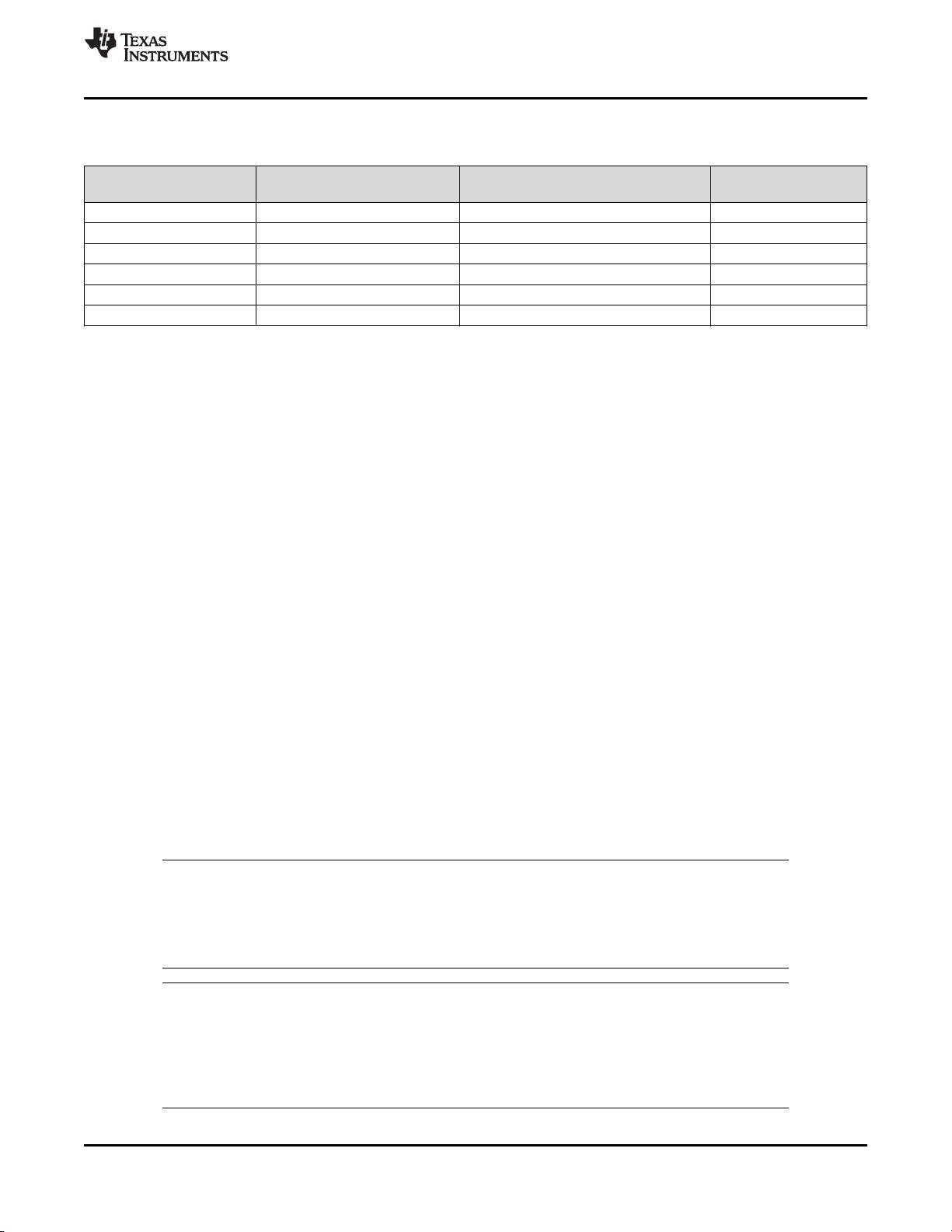

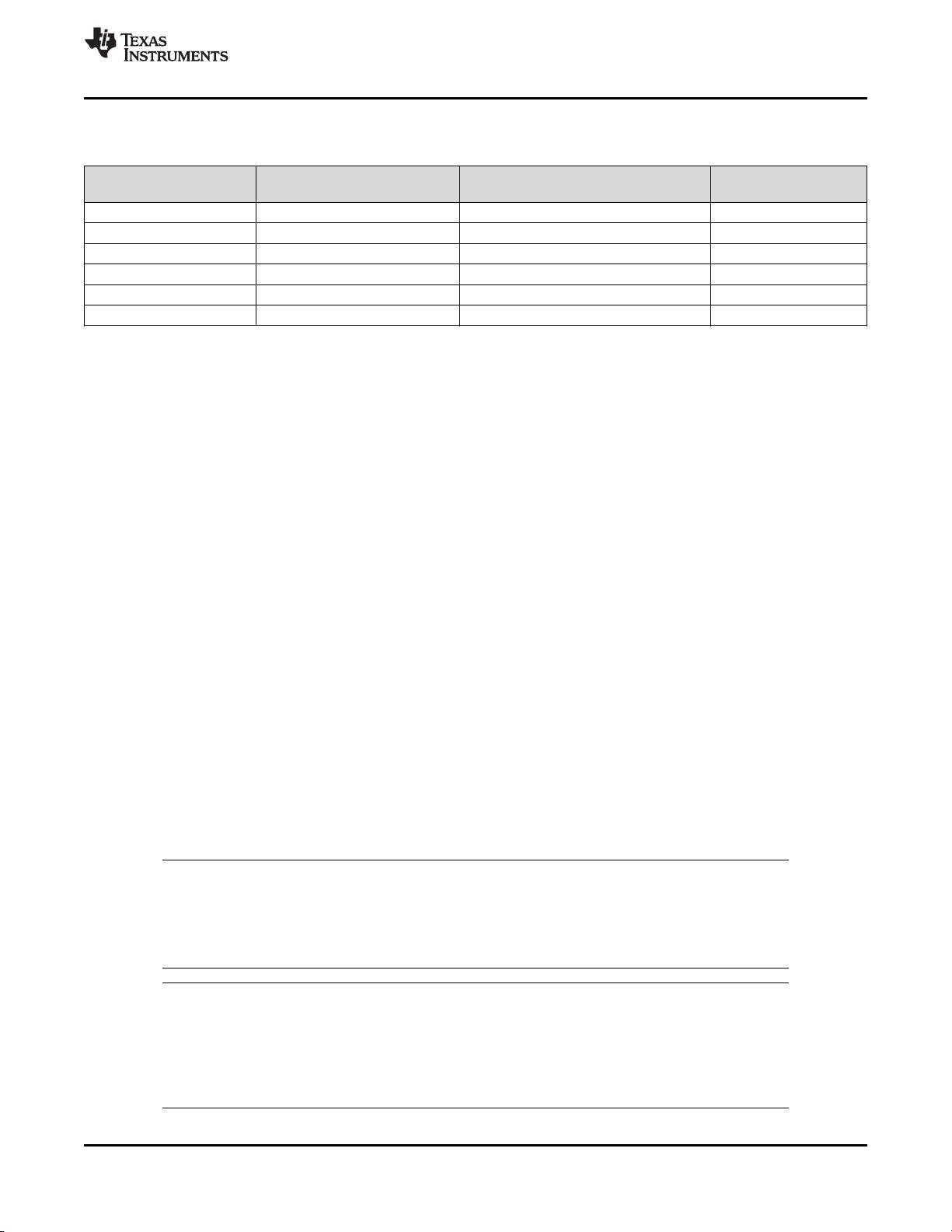

Table 1. GPIO REFCLK or DACP/N Frequency Selection

(1)(2)(3)

GPIO[3:1]

REFCLK FREQUENCY

(DPPLL_CLK_SRC = 0)

DACP/N CLOCK FREQUENCY

(DPPLL_CLK_SRC = 1)

REFCLK_FREQ

3’b000 12 MHz 468 MHz (DSIACLK / 39 = 12 MHz ) 0x0

3’b001 19.2 MHz 384 MHz (DSIACLK / 20 = 19.2 MHz) 0x1

3’b010 26 MHz 416 MHz (DSIACLK / 16 = 26 MHz) 0x2

3’b011 27 MHz 486 MHz (DSIACLK / 18 = 27 MHz) 0x3

3’b100 38.4 MHz 460.8 MHz (DSIACLK / 12 = 38.4 MHz) 0x4

3’b101 through 3’b111 19.2 MHz 384 MHz (DSIACLK / 20 = 19.2 MHz) 0x5 through 0x7

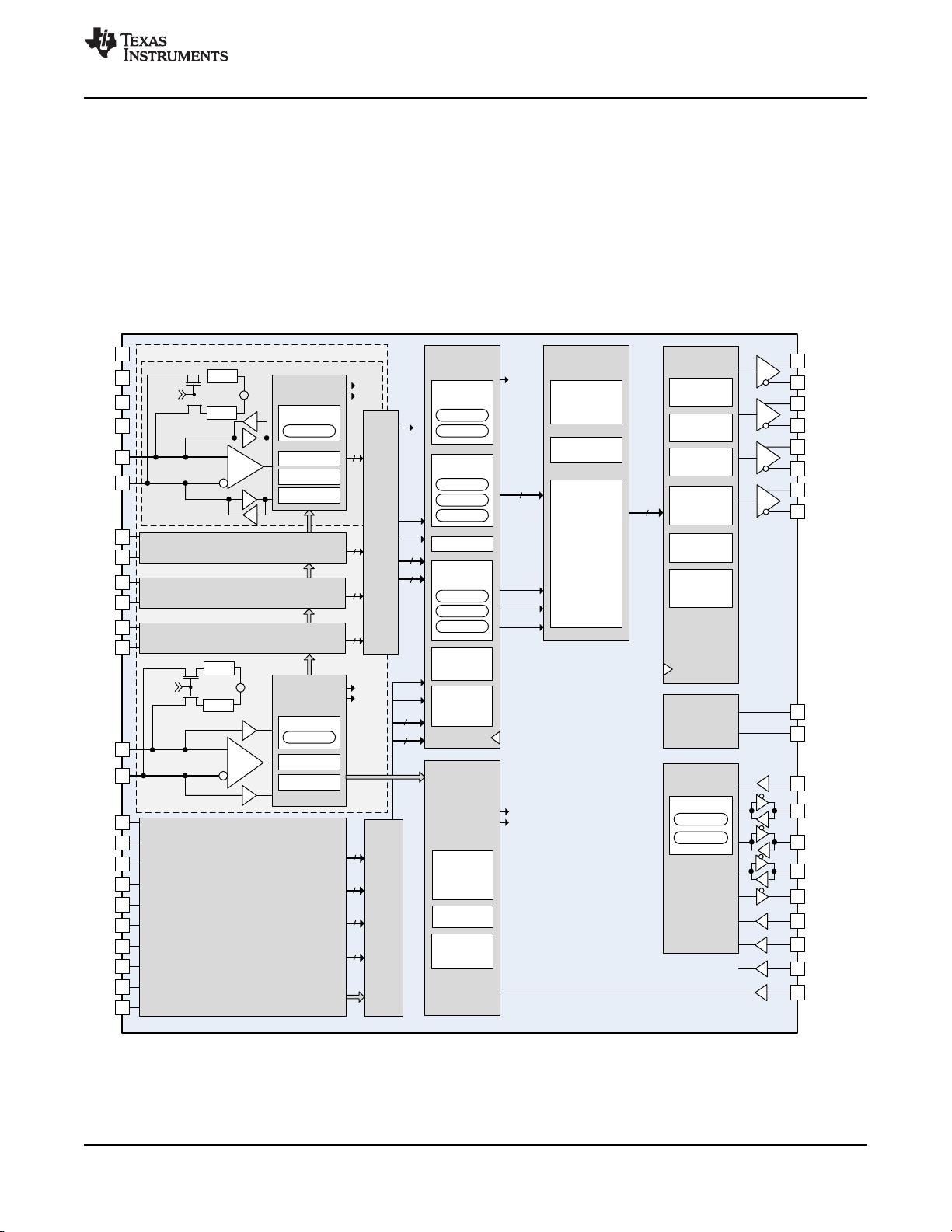

8.3.3.2 Suspend Mode

Suspend mode is intended to be used with the Panel Self Refresh (PSR) feature of the eDP sink. The PSR

feature saves system power but this power savings must not produce any noticeable display artifacts to the end

user. The deassertion of EN produces the greatest DSIx6 power savings, but the reconfiguration of the DSIx6

may be too slow, and therefore produce a bad end-user experience. In this case, Suspend mode is the next best

option for reducing DSIx6 power consumption while in an active PSR state. Suspend mode allows for quick exit

from an active PSR state.

When GPIO1 is configured for suspended operation (GPIO1 pin is asserted), then the DSIx6 is placed in low-

power mode. The suspend (GPIO1) pin is sampled by the rising edge of REFCLK. If the suspend pin is sampled

asserted, then all CSR registers do not reset to the default values, and the DP PLL, DP interface, and DSI

interfaces are powered off, as shown in Figure 3. REFCLK can be turned off when DSIx6 is in Suspend mode.

Timing Requirements summarizes the timing requirements to take the DSIx6 into Suspend mode.

The DSIx6 supports assertion of IRQ for HPD events. When an IRQ_HPD event is detected and both IRQ_EN

and IRQ_HPD_EN bits are set, then the DSIx6 will assert the IRQ.

In order to take the DSIx6 out of Suspend mode, the REFCLK must be running before and after the suspend

(GPIO1) pin is deasserted. After the DP PLL is locked, the DSIx6 transitions the ML_TX_MODE from Main Link

Off to either Normal or Semi-Auto Link depending on the state of PSR_TRAIN register. If the PSR_EXIT_VIDEO

bit is set, then active video begins transmitting over the DisplayPort interface after the first vertical sync start

(VSS) is detected on the DSI interface. If the PSR_EXIT_VIDEO bit is not set, software must enable the

VSTREAM_ENABLE bit. Then active video begins transmitting over the DisplayPort interface after the first

vertical sync start The Timing Requirements table summarizes the timing requirements to take the DSIx6 into

SUSPEND mode. (VSS) is detected on the DSI interface.

NOTE

If the GPIO4_CTRL is configured for PWM, the PWM will be active during SUSPEND. If

the system designer does not wish the PWM active during SUSPEND, then software can

change the GPIO4_CTRL to Input before entering SUSPEND and then re-enable PWM

after exiting SUSPEND by changing the GPIO4_CTRL to PWM.

NOTE

For the case when DPPLL_CLK_SRC = 1, REFCLK mentioned in this section is replaced

with a divided down version of the DSIA_CLK (DCAP/N). The means that DSIA_CLK must

be active before the assertion of SUSPEND and before the deassertion of SUSPEND as

specified in Timing Requirements . The DSIA_CLK can be stopped while in SUSPEND as

long as above requirements are meet.