等精度测频原理频率计设计与仿真实现

需积分: 10 117 浏览量

更新于2024-09-12

收藏 172KB DOC 举报

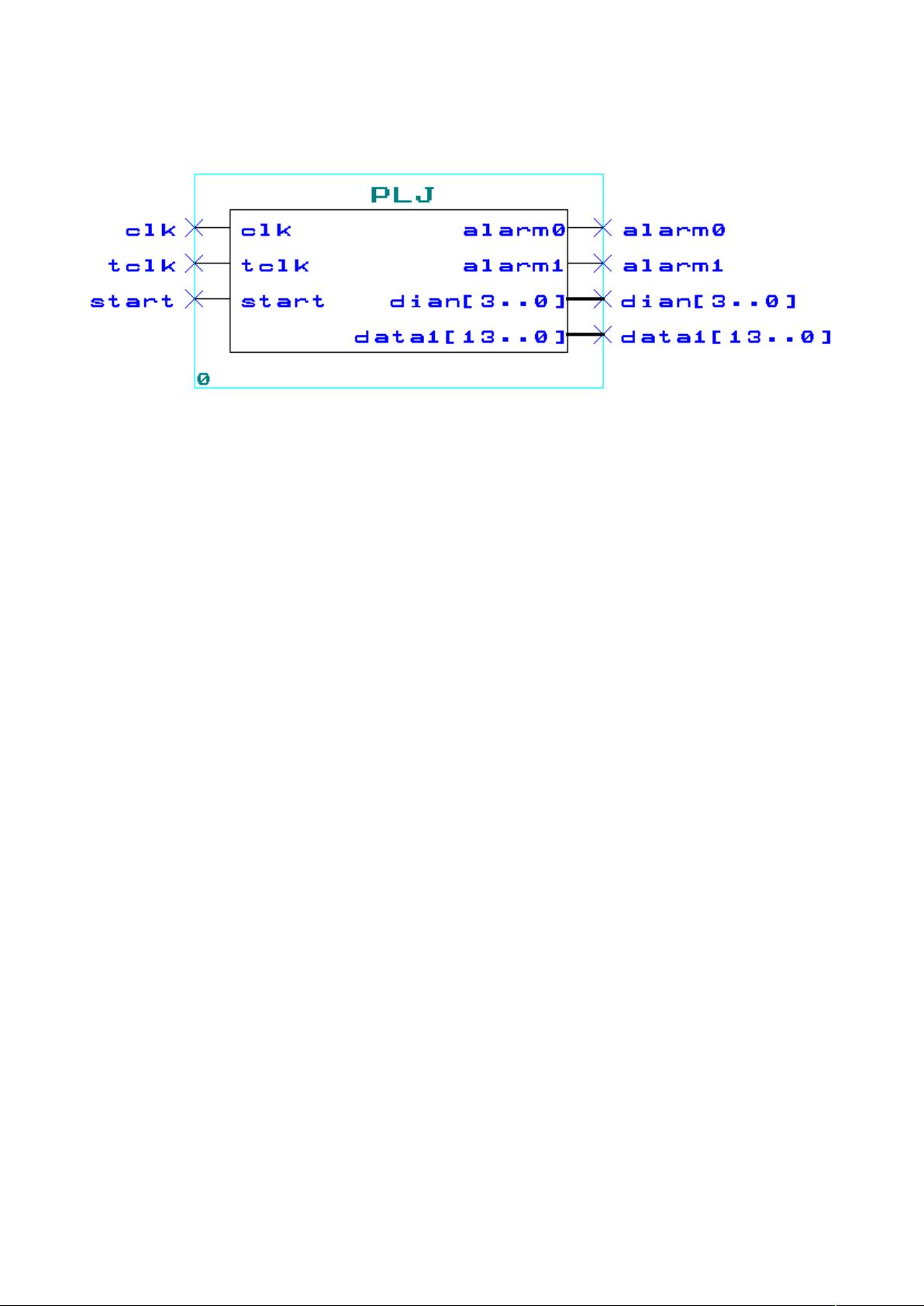

"该资源是关于使用等精度测频原理设计和仿真的频率计程序,主要涉及FPGA实现。程序文件名为PLJ.vhd,功能是实现4位显示的频率计,可以显示频率数据和控制小数点显示,并具有超量程和欠量程报警功能。"

在数字系统中,频率计是一种重要的测量设备,用于测量输入信号的频率。等精度测频法是一种常见的频率测量方法,它的基本思想是通过比较两个不同频率的时钟信号的周期,从而计算出待测信号的频率。在这个程序中,设计者使用了FPGA(Field-Programmable Gate Array)进行硬件实现,FPGA允许用户自定义逻辑电路,非常适合于这种定制化的测量任务。

代码中的关键部分包括以下几个模块:

1. **预置闸门分频系数**(q):这是一个计数器,当达到预设值(9999)时,预置闸门关闭(en='0')。这个预置闸门的作用是控制数据采集的时间窗口,以确保在测量过程中有足够的时间获取准确的计数值。

2. **被测信号计数器**(q1):在实际闸门(en1)开启期间,它记录输入信号(tclk)的脉冲数。每当输入信号的上升沿到来且实际闸门开启时,q1的值会增加1。

3. **基准信号计数器**(q2):这是另一个计数器,用于记录基准时钟(clk)的脉冲数。通常,基准时钟的频率远高于被测信号,用于提供精确的时间基准。

4. **实际闸门信号**(en1):根据预置闸门信号(en)和被测信号(tclk)的状态,控制被测信号计数器的计数。只有当预置闸门开启时,才会对被测信号进行计数。

5. **运算器**(qq, qqq):这部分可能用于计算频率数据,通过比较被测信号计数器(q1)和基准信号计数器(q2)的值,计算出频率比,然后进一步处理得到最终的频率数据。

6. **小数点控制**(dian):在en1的下降沿输出,但只有在数据转换完成后,小数点dian的信号才能保证正确。这部分可以通过译码逻辑实现,以确保在显示频率数据时,小数点的位置准确无误。

7. **报警信号**(alarm0, alarm1):用于指示频率超出量程,即被测频率超过或低于预定范围。

通过VHDL(Very High Speed Integrated Circuit Hardware Description Language)编写的设计描述了整个系统的逻辑行为。在仿真阶段,可以验证所有这些逻辑是否按照预期工作,确保频率计的精度和可靠性。一旦通过仿真验证,这个设计可以被综合并下载到FPGA中,实现在硬件上的实际运行。

126 浏览量

112 浏览量

236 浏览量

126 浏览量

2024-06-19 上传

2022-03-11 上传

2021-10-07 上传

2022-03-07 上传

469 浏览量

Aleanne

- 粉丝: 0

- 资源: 3

最新资源

- Pokemon-App

- 变焦级镜考勤

- English to Bengali Dictionary | BDWord-crx插件

- ACAM_Demo:工作演员条件注意地图的实时动作检测演示。 此回购包括用于人员检测的完整管道,用于实时跟踪和分析其行为

- FE内容付费系统响应式 带手机版 v5.42

- matlab的slam代码-16-833:机器人定位和地图绘制-2019年Spring[CMU]

- 快乐的地方

- payment-integration-project:作为Sparks Foundation的GRIP实习的一部分,完成了Payment Gateway集成项目

- 一款简单的潜艇大战游戏

- 智睿政务问卷调查系统 v10.9.0

- olive-dolphin-prophecy

- 2019国赛C题资源(1).zip

- ElvishElvis.github.io

- grape-oink:Grape 的中间件,允许使用 Oink

- buyers-remorse-app:一个基于React的Web应用程序,以提高个人对购买选择的认识

- TinyPNG For Photoshop