25Gbps高速无源通道设计的挑战与关键技术

需积分: 10 131 浏览量

更新于2024-09-16

收藏 923KB PDF 举报

"本文详细探讨了25G高速无源通道设计所面临的挑战,特别是信号完整性问题,涵盖了25Gbps链路的结构、信号处理技术以及未来发展趋势。"

在高速电子设计领域,25G高速无源通道的设计是当前的重要议题,尤其对于高速PCB设计工程师来说,这一技术的掌握至关重要。随着通信技术的发展,数据传输速率的需求不断提高,从10Gbps逐步提升至25Gbps甚至更高,这对无源通道的设计提出了新的挑战。

25Gbps的无源通道设计涉及到多个关键因素,首先,它需要处理高频率信号的传输,这要求通道具有极低的插入损耗和回波损耗,以保证信号的完整性。随着速率的增加,信号的衰减和失真问题变得更加显著,可能引发眼图闭合、误码率(BER)上升等严重问题。因此,设计者必须精确控制布线的长度、宽度、介电常数以及串扰等因素,确保信号在通道中的有效传输。

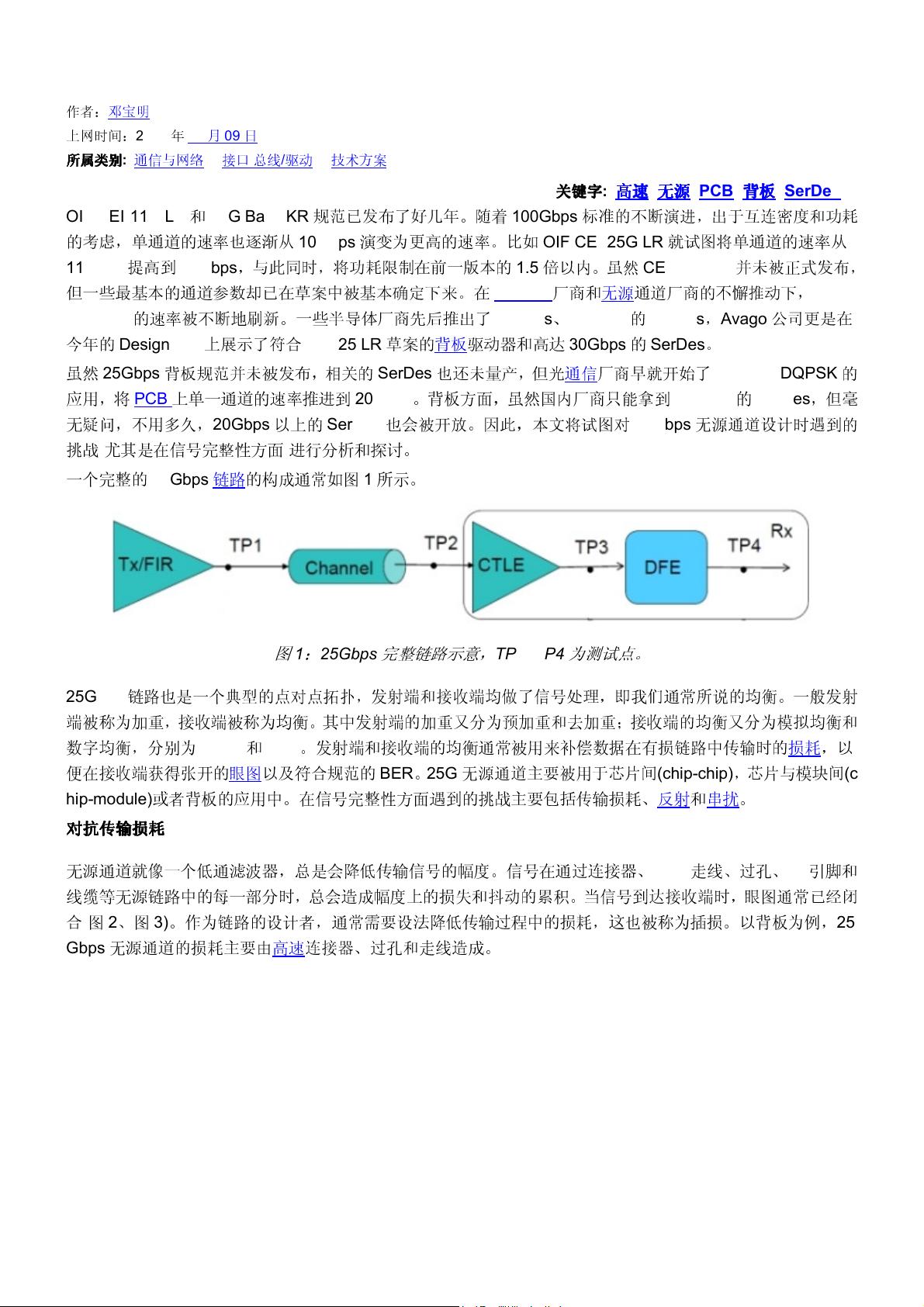

其次,发射端和接收端的信号处理技术是解决这些问题的关键。发射端的预加重和去加重技术可以改善信号的上升时间,减少过冲和下冲,而接收端的CTLE(连续时间线性均衡)和DFE(决定反馈均衡)则用于消除通道中的脉冲响应失真,恢复出清晰的眼图。这些均衡技术的精细调整是确保25Gbps信号在有损通道中正确传输的核心。

此外,高速无源通道还面临着阻抗匹配的挑战。在25Gbps的速率下,任何微小的阻抗不匹配都可能导致反射,从而降低信号质量。设计者需要通过精确的仿真和实验来优化通道的阻抗特性,使其与发送和接收端的阻抗相匹配。

在25Gbps的背板应用中,串扰问题也变得尤为突出。由于相邻信号线之间的距离缩小,相互间的耦合效应会加剧,导致信号质量下降。因此,布线策略和屏蔽技术的运用成为设计中的重要环节,例如采用差分对、增加间距、使用屏蔽层等手段来降低串扰影响。

不仅如此,随着技术的不断发展,半导体厂商已经在研发更高速率的SerDes,如Avago展示的30Gbps SerDes,预示着未来可能面临更严峻的挑战。因此,25Gbps无源通道设计的研究不仅是为了满足当前的标准,也是为了应对未来的高速接口需求。

25G高速无源通道设计的挑战主要集中在信号完整性、阻抗匹配、串扰控制以及发射和接收端的信号处理技术上。设计者需要结合理论知识、仿真工具和实践经验,不断优化设计,以应对不断提高的数据传输速率需求。同时,随着行业标准的更新和新技术的涌现,设计者还需要持续学习和适应,以保持在这个快速发展的领域的竞争力。

2017-04-24 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-03-06 上传

2021-02-08 上传

2020-10-25 上传

逸江南

- 粉丝: 2

- 资源: 5

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程