25Gbps无源通道设计:挑战与信号完整性分析

32 浏览量

更新于2024-09-01

收藏 245KB PDF 举报

"这篇文章除了讨论25G高速无源通道的设计挑战,还提到了OIF CEI-11G LR和10G Base KR标准的发展,以及随着100Gbps标准演进中单通道速率的提升。文章指出,尽管OIF CEI-25G LR规范尚未正式发布,但在SerDes制造商和无源通道供应商的推动下,高带宽技术正不断进步。例如,Avago公司在DesignCon上展示了符合CEI-25G LR草案的组件,包括高达30Gbps的SerDes。"

在高数据速率通信领域,特别是随着100Gbps标准的发展,单通道速率的提升是至关重要的。OIF CEI-11G LR和10G Base KR标准已经无法满足日益增长的带宽需求,因此出现了CEI-25G LR规范,它旨在将单通道速率从11Gbps提升至25Gbps,同时控制功耗不超过原有标准的1.5倍。尽管该规范尚未正式确立,但它定义的基本通道参数已经在草案中得到了确认。

文章特别强调了SerDes技术在推动这一速率提升中的作用。不同半导体厂商已经推出15Gbps和20Gbps的SerDes产品,Avago公司甚至展示出达到30Gbps速率的解决方案,这表明技术正在快速进步。此外,光通信行业也在积极应用40Gbps DQPSK技术,使得PCB上的单一通道速率达到20Gbps。

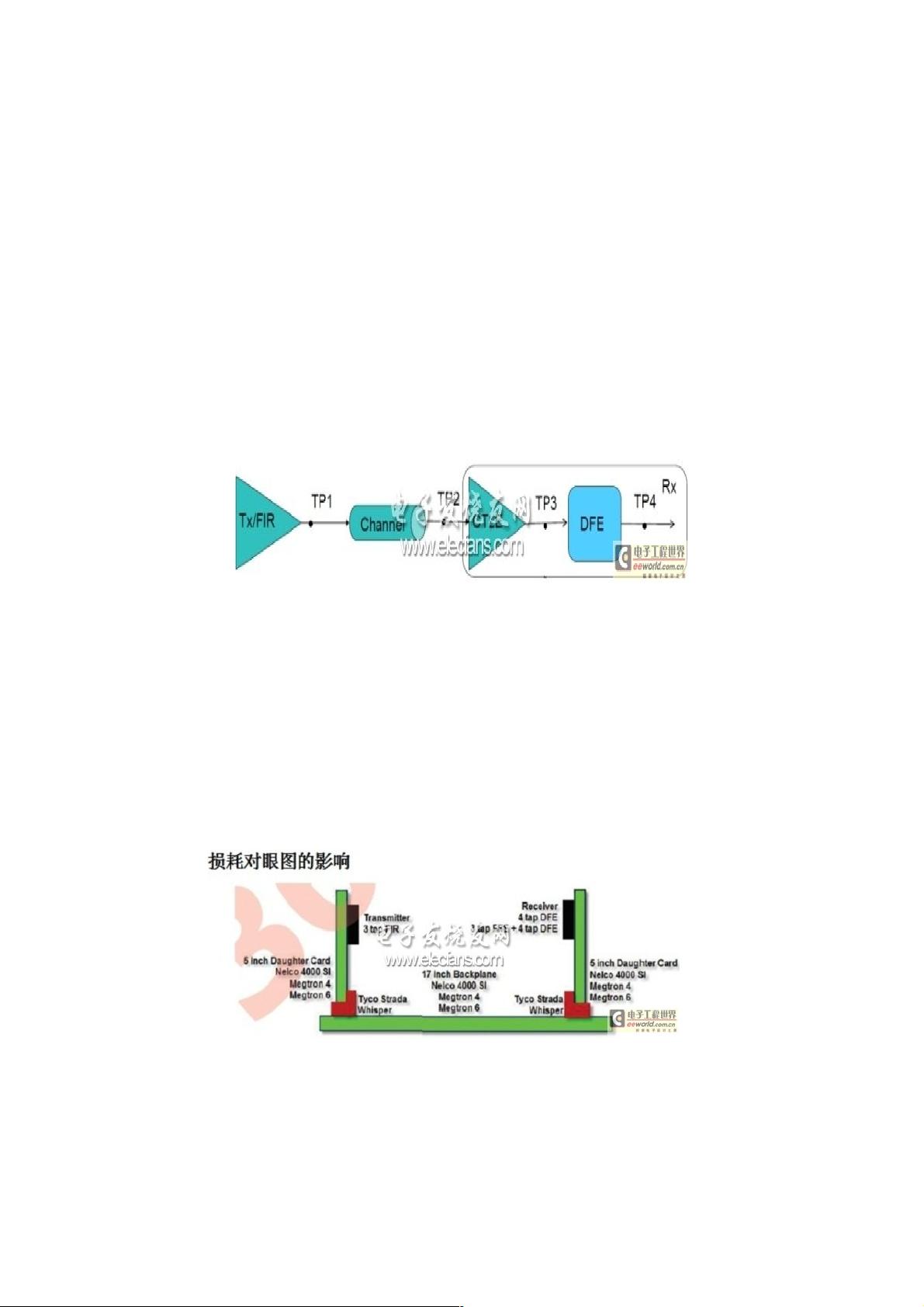

面对25Gbps无源通道设计的挑战,尤其是信号完整性问题,文章指出无源通道如同低通滤波器,会衰减传输信号的幅度。整个链路包含发射端、接收端以及中间的连接器、PCB走线、过孔和IC引脚等组成部分,每个环节都可能引入损耗和干扰。设计者需要考虑如何在这些环节中对抗传输损耗,确保信号质量。

25Gbps高速无源通道设计不仅涉及技术规格的更新,还包括对信号完整性的深度理解和优化,这需要在物理层面上解决一系列复杂的工程问题,如信号衰减、噪声、串扰和反射等。随着技术的不断发展,未来的挑战将是如何在保证性能的同时,实现更高带宽、更低功耗和更紧凑的互连设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2017-04-24 上传

2021-03-06 上传

weixin_38641876

- 粉丝: 3

- 资源: 942

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程