Xilinx Vivado HLS:高阶综合指南与设计优化

需积分: 9 102 浏览量

更新于2024-07-23

收藏 11.73MB PDF 举报

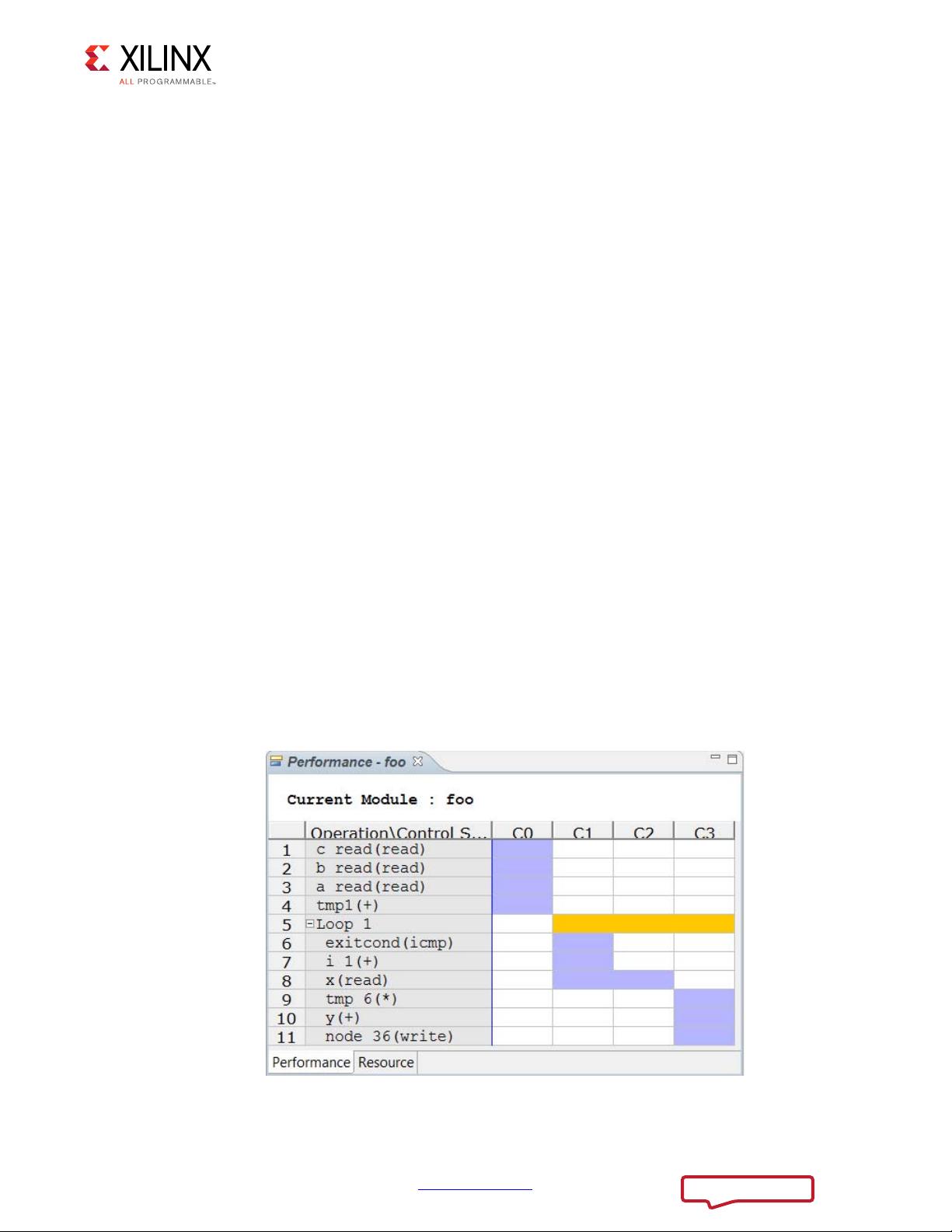

Vivado High-Level Synthesis (HLS)是Xilinx Vivado Design Suite的一部分,专注于将高级语言(如C)编写的算法转化为硬件设计,旨在简化FPGA和ASIC设计过程。该指南(UG902 v2014.1)于2014年4月发布,更新了Vivado Design Suite用户手册中的HLS内容组织,并引入了名为HLS UltraFast Design Methodology的新方法论。

第1章详细介绍了HLS的基本概念,包括如何利用基于C的编程进行FPGA设计。它涵盖了如何在Vivado HLS环境中工作,从编写C代码到实现高性能、低延迟的设计。这部分还讨论了接口管理、设计优化策略以及如何通过RTL Verification确保代码的质量,以及如何最终导出硬件描述语言(RTL)设计。

第2章着重于使用Vivado HLS库,这些库为特定应用提供了预定义的功能和数据类型,例如Arbitrary Precision DataTypes Library用于处理高精度数据,HLS Stream Library支持流处理,HLS Math Library提供数学运算功能,Vivado HLS Video Library专为视频处理设计,而IPLibraries(Image Processing Libraries)则针对图像处理任务。另外,还有HLS Linear Algebra Library,便于执行线性代数计算。

第3章探讨了在HLS编程时需要注意的一些限制和最佳实践,如不支持的C构造、如何创建有效的测试平台(CTestBench),以及函数的使用方式。这些指导有助于开发者编写高效且可转换的代码,避免在HLS转换过程中遇到的问题。

Vivado HLS是一个强大的工具,它允许工程师使用熟悉的C语言开发,同时利用Xilinx的优化算法将代码自动映射到硬件上。通过理解并遵循指南中的内容,设计师可以提升设计效率,缩短开发周期,并在满足性能需求的同时,降低硬件复杂度。随着技术的发展,后续版本可能会包含更多优化方法和库,以适应不断变化的需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-05-13 上传

2019-06-12 上传

2020-08-13 上传

2020-08-13 上传

2021-08-09 上传

2019-08-22 上传

lkzai

- 粉丝: 0

- 资源: 1

最新资源

- casa-inteligente

- esp:esp咨询开发人员

- Accuinsight-1.0.23-py2.py3-none-any.whl.zip

- 径向基函数 (RBF) 教程 - 作为函数逼近器的神经网络:关于径向基函数 (RBF) 的西班牙语教程,仅供学术和教育使用-matlab开发

- neighbors:le Wagon编码训练营的最终项目,批次531

- DP-060JA-Migrating-your-Database-to-Cosmos-DB

- 九九乘法口诀表(word打印版).rar

- AdsAuth

- athena_health:雅典娜健康宝石的叉子

- Digimon Database 数码兽数据库-数据集

- 西门子200发脉冲控制步进电机程序.rar

- monitor-bot:通过官方手柄跟踪网站的变化和新推文

- tap-console-parser:通过劫持 console.log 解析 TAP

- Login-page:登录页面以及链接到postgres的数据库

- TomKingDAO-猫王DAO框架

- Projeto-Site-de-Noticias-Cidade:城市新闻网站的设计