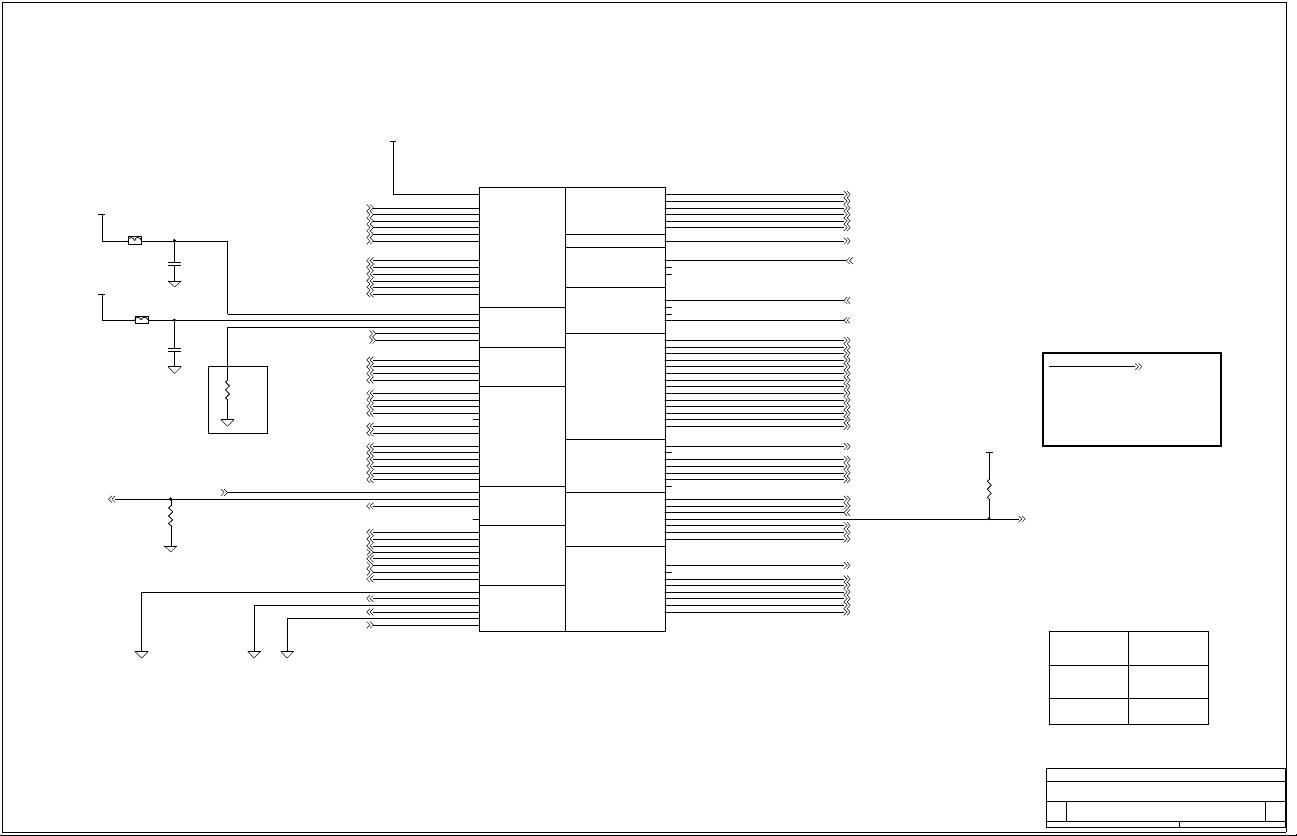

MT6253原理图关键引脚及信号解析

"10112@52RD_MT6253原理图"

MT6253是一款由联发科(Mediatek)设计的集成电路,常用于移动通信设备,如智能手机和平板电脑。这份原理图详细展示了该芯片在电路设计中的应用,包含了各种电源、接口、控制信号以及音频、摄像头等关键模块的连接。

首先,我们看到多个电源引脚,如USB_AVDD33、PAD_VRT、USB_AVDD12、VCORE_PMU等,它们分别对应USB接口的供电、芯片工作所需的电压参考、核心电源管理单元的电压以及模拟电源,这些都是芯片正常工作的基础。

SRCLKENAI是一个时钟使能输入信号,通常用于同步或控制芯片内部的时钟生成器。VM_SEL可能是一个电压模式选择信号,用于选择芯片的不同工作模式。

VUSB、MICBIAS、VIO是关键的电源引脚,VUSB为USB接口供电,MICBIAS为麦克风提供偏置电压,VIO则是用于IO接口的电压。

URXD1、UTXD1代表串行数据接收和发送,是UART接口的一部分,用于与外部设备进行异步通信。3,10表示这些信号可能通过3.3V逻辑电平进行传输,并且可能具有10kΩ的上拉电阻。

GPIO(通用输入/输出)引脚如GPIO22_FMARK、GPIO15_BT_PCMCLK等,可以配置为系统需要的各种功能,如标记信号、蓝牙PCM时钟等。GPIO74_BT_32k可能是蓝牙模块的32kHz时钟输出。

MCDA0到MCDA3以及MCCK、MCCMD是SPI(串行外围接口)总线的一部分,用于与外部存储器或传感器进行通信。MCINS可能用于芯片的内插信号。

音频相关的引脚包括MICP0、MICN0、MICN1、MICP1,它们是麦克风的正负极输入,用于捕捉声音。LoudSPKN0、LoudSPKP0、MP3_OUTR、MP3_OUTL是扬声器和耳机的输出端口,而AU_OUT0_P、AU_OUT0_N是音频输出的差分信号。

摄像头接口包含CAMDAT0到CAMDAT7,CMMCLK、CMPCLK、CMHREF、CMVREF、CMRST以及GPIO45_LPCE0B_LCM等,这些用于与摄像头传感器交换数据并控制其操作。

USB接口的信号有USB_DP和USB_DM,它们是USB数据加和数据减信号,而EINT_Headphone_Det可能是耳机插入检测中断。

此外,还有KCOL和KROW系列引脚,这些通常与键盘矩阵扫描有关。WATCHDOG是看门狗定时器,用于系统稳定性。APC可能是自动电源控制信号,ADC2_ACC则涉及模数转换器,用于采集模拟信号。

最后,GPIO1_FM_SDA、GPIO24_CM_SCL、GPIO25_CM_SDA与GPIO18_BT_RESET等引脚涉及到I2C(互连设备总线)和SPI通信,以及蓝牙模块的复位控制。

这份原理图涵盖了MT6253芯片在实际电路中的各种功能和接口,是理解系统硬件设计的重要参考资料。

2011-10-21 上传

2023-04-27 上传

2023-06-28 上传

2023-06-03 上传

2023-05-29 上传

2023-03-20 上传

2023-04-23 上传

2023-06-03 上传

huangshouyi

- 粉丝: 0

- 资源: 22

最新资源

- 天池大数据比赛:伪造人脸图像检测技术

- ADS1118数据手册中英文版合集

- Laravel 4/5包增强Eloquent模型本地化功能

- UCOSII 2.91版成功移植至STM8L平台

- 蓝色细线风格的PPT鱼骨图设计

- 基于Python的抖音舆情数据可视化分析系统

- C语言双人版游戏设计:别踩白块儿

- 创新色彩搭配的PPT鱼骨图设计展示

- SPICE公共代码库:综合资源管理

- 大气蓝灰配色PPT鱼骨图设计技巧

- 绿色风格四原因分析PPT鱼骨图设计

- 恺撒密码:古老而经典的替换加密技术解析

- C语言超市管理系统课程设计详细解析

- 深入分析:黑色因素的PPT鱼骨图应用

- 创新彩色圆点PPT鱼骨图制作与分析

- C语言课程设计:吃逗游戏源码分享